Method and device for reducing interconnection line model of great quantity of ports

A technology of model reduction and interconnection, which is applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of long simulation time of models, achieve short simulation time, high efficiency, and ensure passivity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

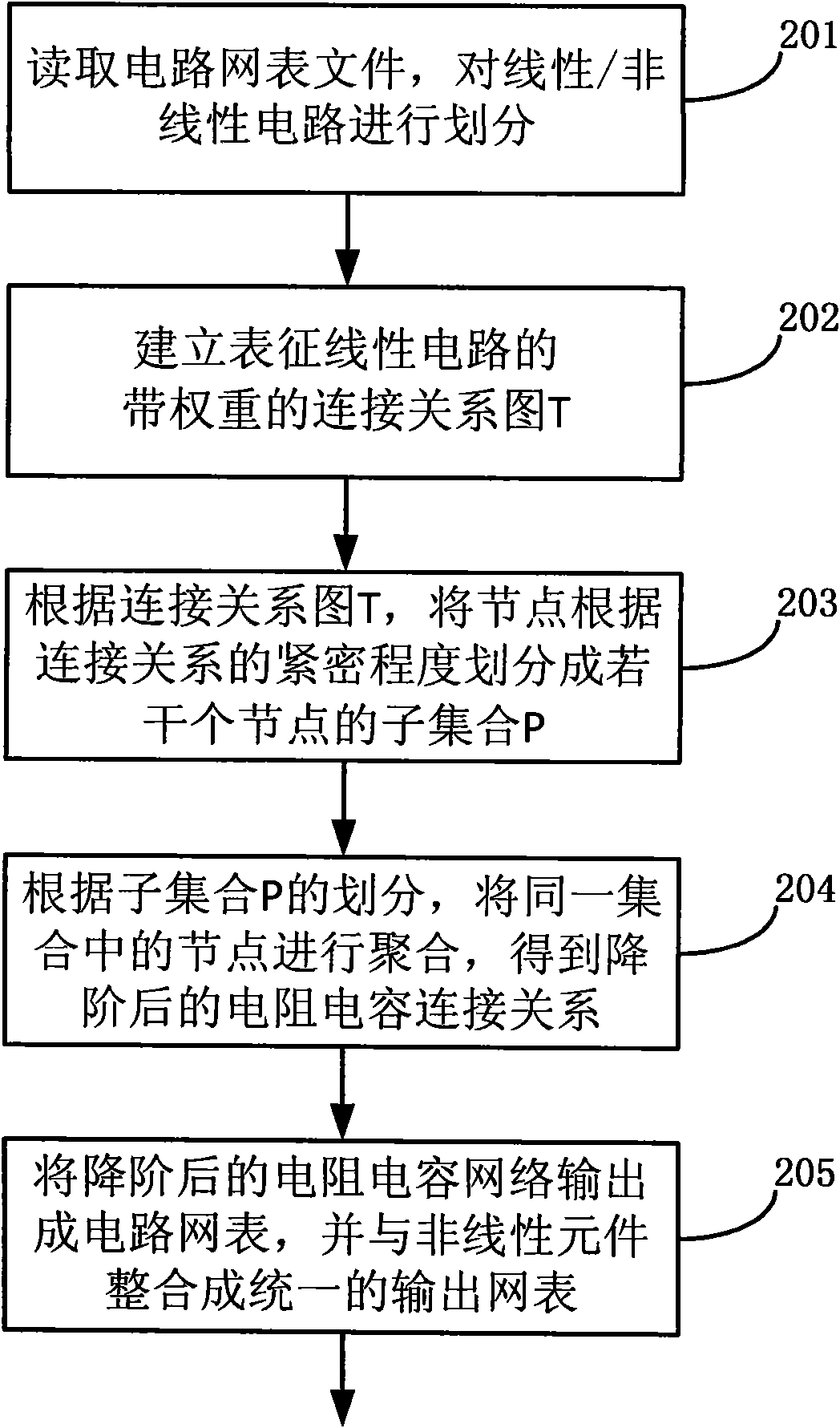

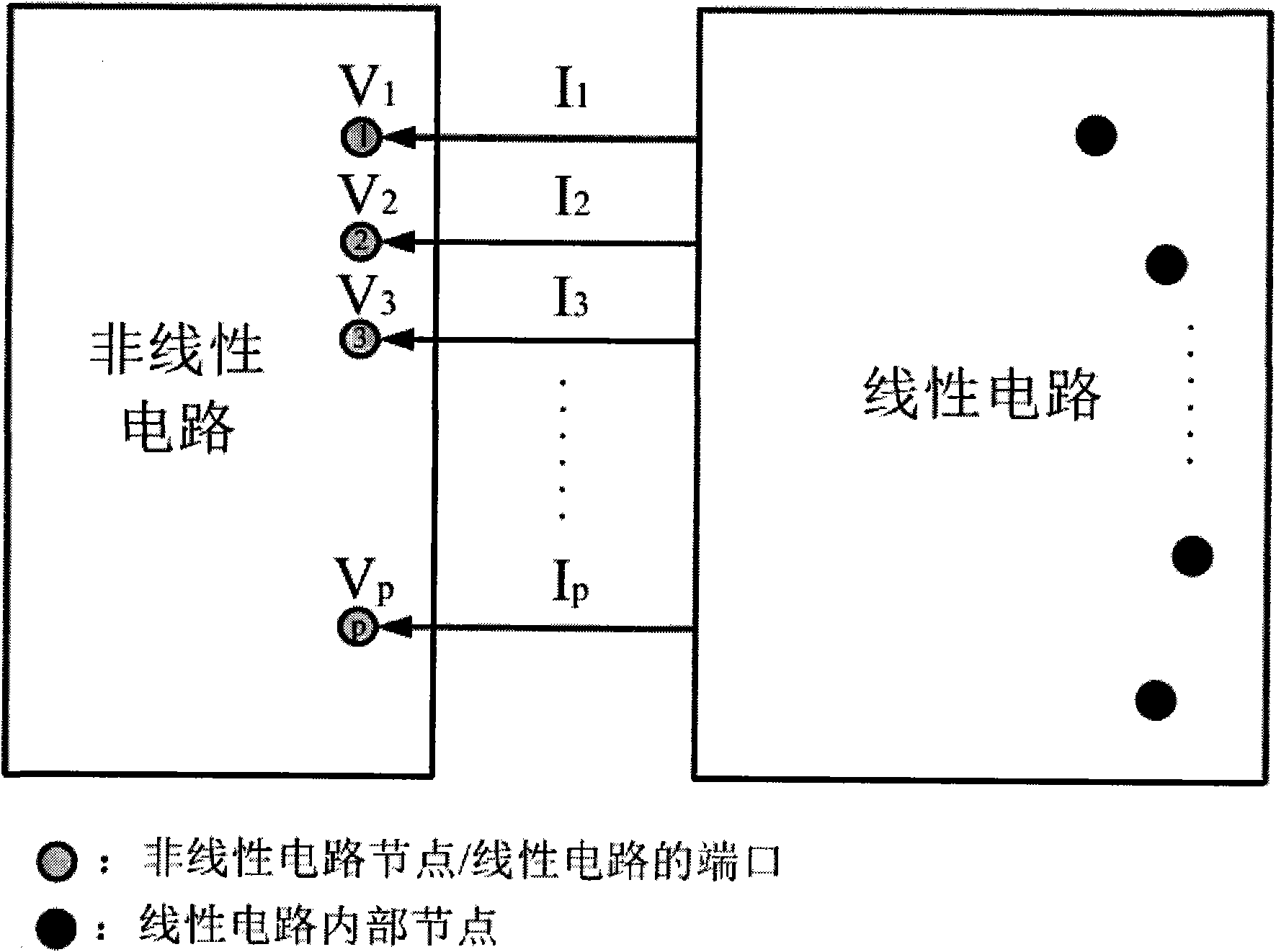

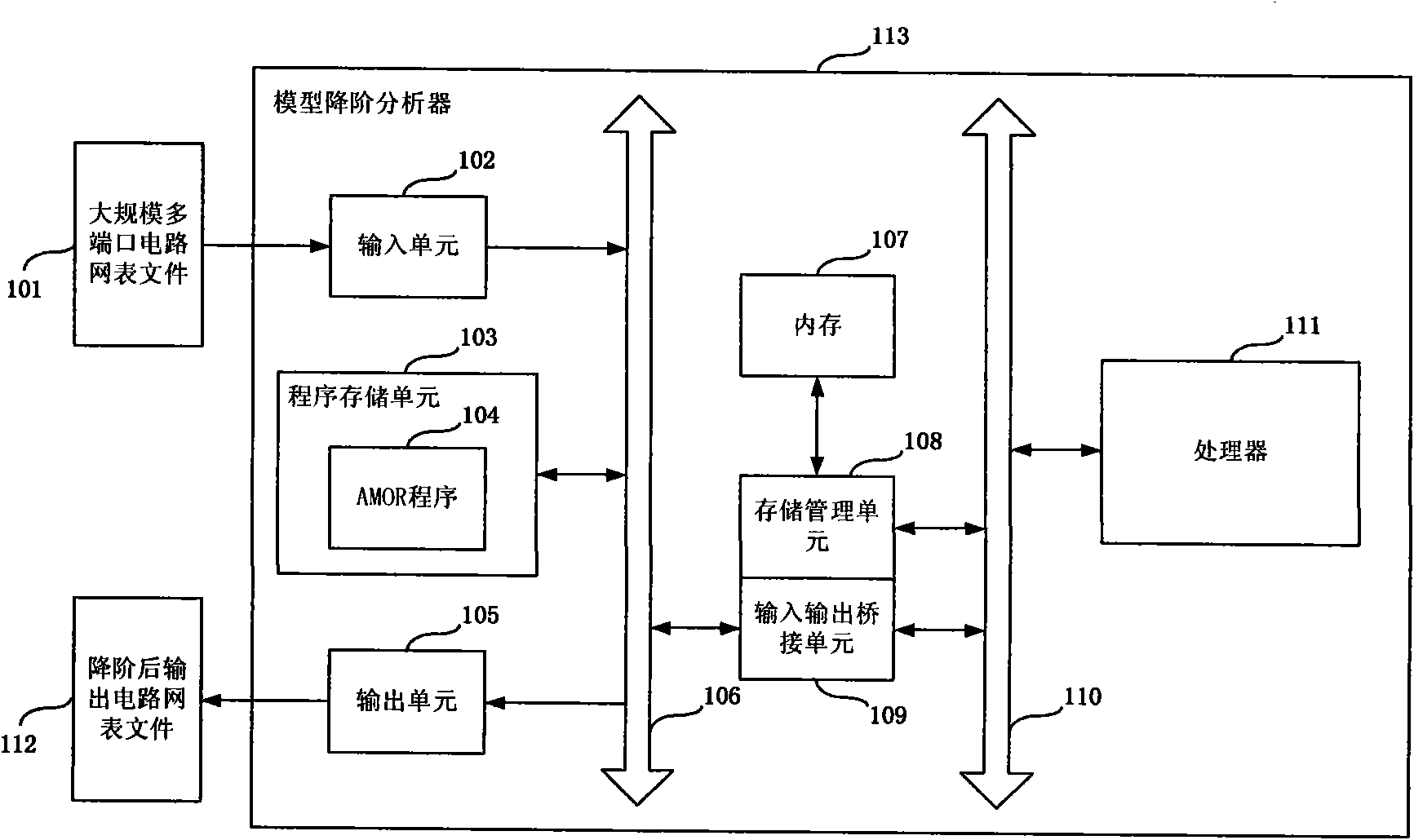

Method used

Image

Examples

Embodiment 1

[0052] A phase-locked loop circuit is composed of 836 MOS tubes. After extracting the parasitic parameters, there are 44726 resistor-capacitor linear elements, and the number of circuit nodes is 7314. By dividing into linear sub-circuits and nonlinear sub-circuits in step 201, it can be obtained that the number of ports of the linear sub-circuit is 1326. The original circuit simulation time was 14 seconds. Setting the maximum number of nodes in the subset in step 203 to 10, the linear subcircuit can be divided, and a part of the result obtained by division is as follows Figure 6 As shown in , where the ellipse represents the port of the linear circuit, the rectangle represents the internal node of the linear circuit, and the number represents the number of the sub-set to which the node belongs after division. It can be seen that the nodes connected together are divided into the same subset, and such division has physical meaning.

[0053] In order to compare the proposed me...

Embodiment 2

[0058] A multiplier circuit is composed of 3685 MOS tubes. After extracting the parasitic parameters, there are 208497 resistor-capacitor linear elements, and the number of circuit nodes is 18112. By dividing into linear sub-circuits and nonlinear sub-circuits in step 201, it can be obtained that the number of ports of the linear sub-circuit is 3685. The original circuit simulation time is 190 seconds.

[0059]In order to compare the proposed method with the elimination-based method SIP, the present invention uses the above-mentioned embodiments using AMOR and Z.Ye, D.Vasilyev, Z.Zhu and J.R.Phillips at the 1999 International Conference on Computer Aided Design (ICCAD) published the paper "Sparse implicit projection (SIP) for reduction of general many-terminal networks" proposed SIP method (Z.Ye, D.Vasilyev, Z.Zhu, and J.R.Phillips, "Sparse implicit projection (SIP) for reduction of general many-terminal networks," in Proc.ICCAD'2008) two methods for model reduction, and then...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More