Bit-level twin-port nonvolatile static random access memory and implementation method thereof

A static random access, non-volatile technology, applied in static memory, read-only memory, digital memory information, etc., can solve the problem that NVSRAM cannot be realized through the bit level, and achieve the effect of shortening storage time and simple control circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be described in further detail in conjunction with the following specific examples and accompanying drawings, and the protection content of the present invention is not limited to the following examples. Without departing from the spirit and scope of the inventive concept, changes and advantages conceivable by those skilled in the art are all included in the present invention, and the appended claims are the protection scope.

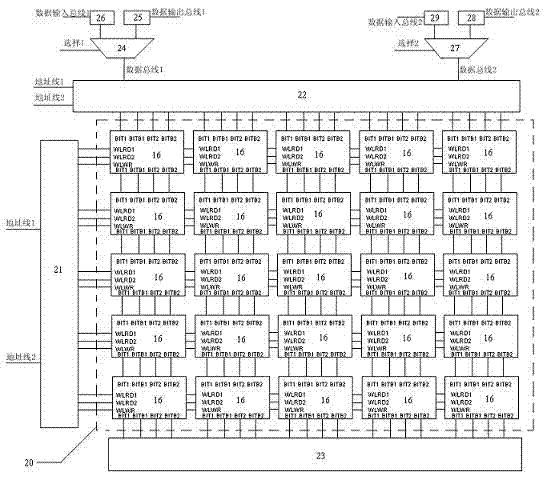

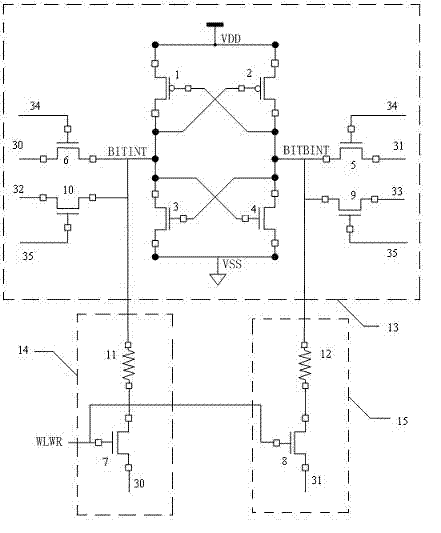

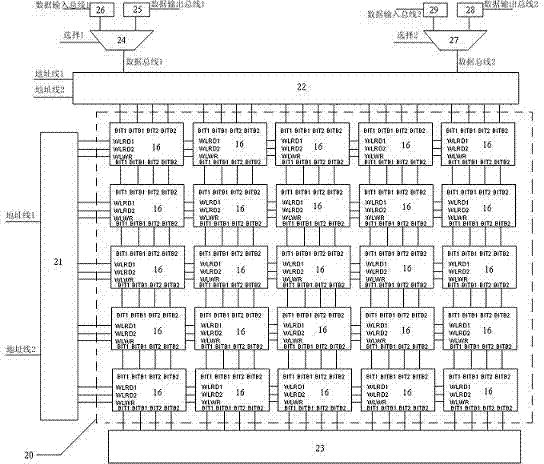

[0038] Such as Figure 1-2, 1-PMOS transistor, 2-PMOS transistor, 3-NMOS transistor, 4-NMOS transistor, 5-NMOS transistor, 6-NMOS transistor, 7-NMOS transistor, 8-NMOS transistor, 9-NMOS transistor, 10-NMOS transistor , 11-Phase-change resistor, 12-Phase-change resistor, 13-Dual-port static storage unit, 14-Phase-change storage unit, 15-Phase-change storage unit, 16-Dual-port non-volatile static storage unit, 20-Dual Non-volatile static memory cell array, 21-word line decoder, 22-bit line decoder, 23-precharge circuit,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More