Method for automatically generating test pattern vector of DSP (Digital Signal Processor) device

A test pattern, automatic generation technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of difficult signal acquisition, difficult to determine, complex instructions, etc., and achieve the effect of easy signal acquisition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

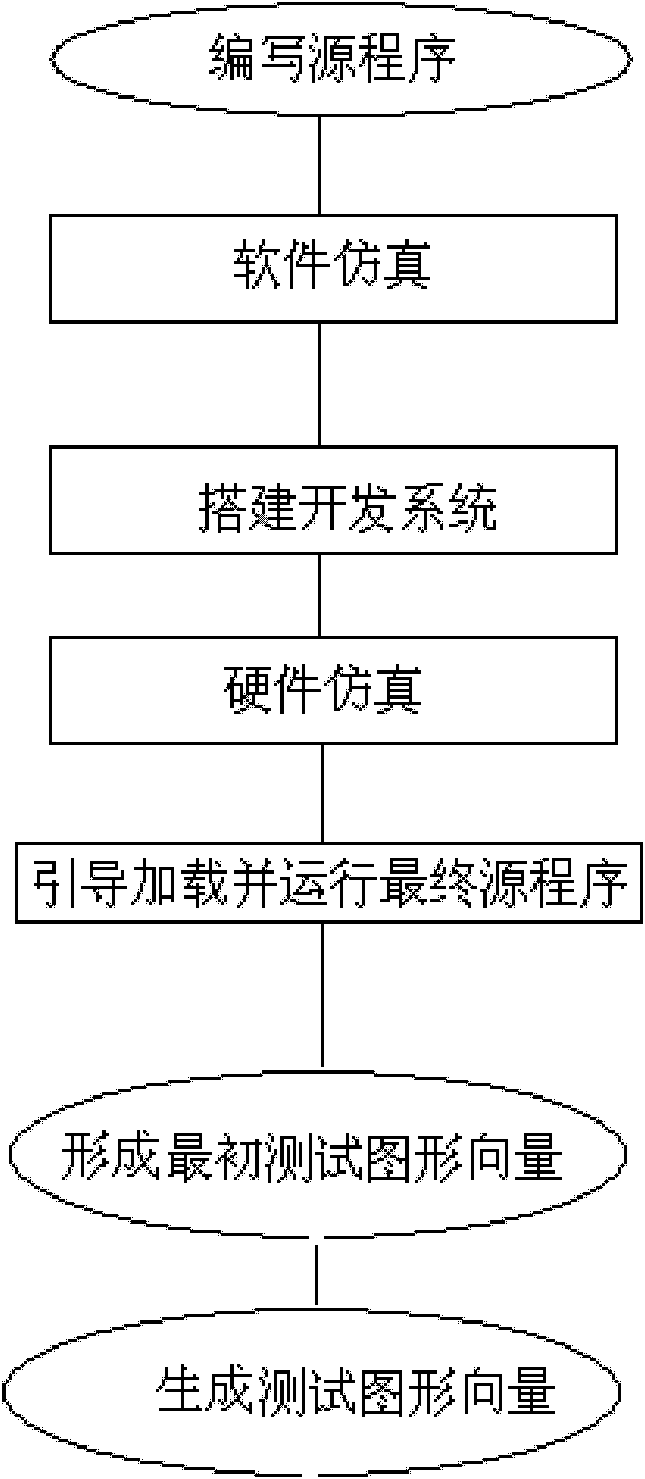

[0030] a. Write the source program:

[0031] Use the assembly language in the DSP instruction set to write the source program;

[0032] b. Software simulation:

[0033] Use CCS3.3 software to simulate the functions of each part of the DSP device, convert the final source program into an executable .out file, and convert the .out file into a .hex file;

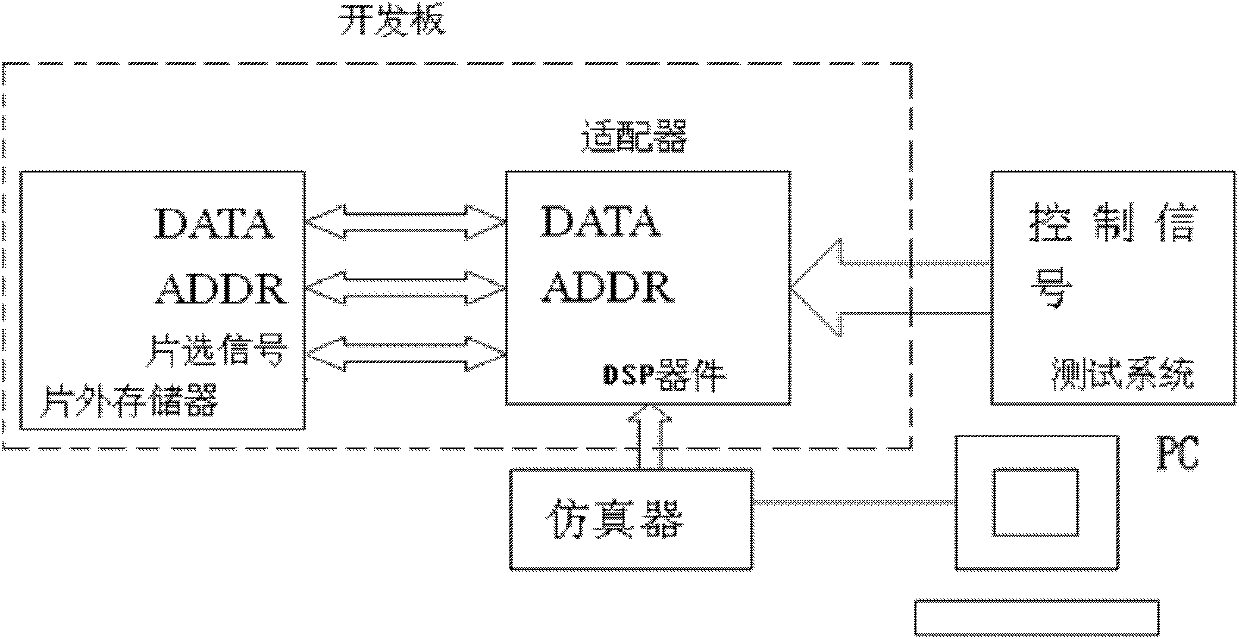

[0034] c. Build a development system:

[0035] Burn the .hex file to the external memory, build a development system consisting of SP3160V large-scale integrated circuit test system, development board and adapter, and provide DSP devices with power supply, clock, reset signal and off-chip auxiliary devices and information for normal operation ;

[0036] d. Hardware emulation:

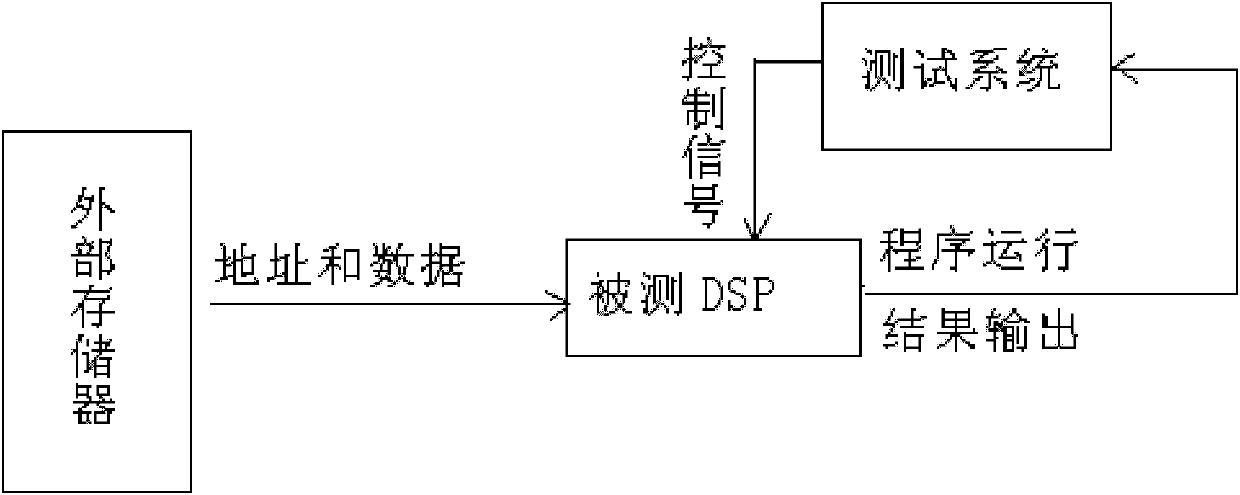

[0037] The development system provides the signal of the normal operation of the DSP device, uses the hardware emulation box to burn the final source program to the DSP device through the JTAG port on the DSP device, and checks the running process an...

Embodiment 2

[0045] a. Write the source program:

[0046] Use the C language in the DSP instruction set to write the source program;

[0047] b. Software simulation:

[0048] Use CCS3.3 software to simulate the functions of each part of the DSP device, convert the final source program into an executable .out file, and convert the .out file into a .hex file;

[0049] c. Build a development system:

[0050] Burn the .hex file to EEPROM, build a development system consisting of SP3160V large-scale integrated circuit test system, development board and adapter, and provide DSP devices with power, clock, reset signals, and off-chip auxiliary devices and information for normal operation;

[0051] d. Hardware emulation:

[0052] The development system provides the signal of the normal operation of the DSP device, uses the hardware emulation box to burn the final source program to the DSP device through the JTAG port on the DSP device, and checks the running process and results of the program th...

Embodiment 3

[0060] a. Write the source program:

[0061] Use the C language in the DSP instruction set to write the source program;

[0062] b. Software simulation:

[0063] Use CCS3.3 software to simulate the functions of each part of the DSP device, convert the final source program into an executable .out file, and convert the .out file into a .hex file;

[0064] c. Build a development system:

[0065]Burn the .hex file to EEPROM, build a development system consisting of SP3160V large-scale integrated circuit test system, development board and adapter, and provide DSP devices with power, clock, reset signals, and off-chip auxiliary devices and information for normal operation;

[0066] d. Hardware emulation:

[0067] The development system provides the signal of the normal operation of the DSP device, uses the XDS560 hardware simulation box to burn the final source program to the DSP device through the JTAG port on the DSP device, and checks the process and results of the program run...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More