Method for forming interconnecting groove and through hole and method for forming interconnecting structure

An interconnection structure and trench technology, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of hydrofluoric acid corrosion of cobalt-tungsten-phosphorus copper, increase of k value, and damage of ultra-low-k dielectric layer, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

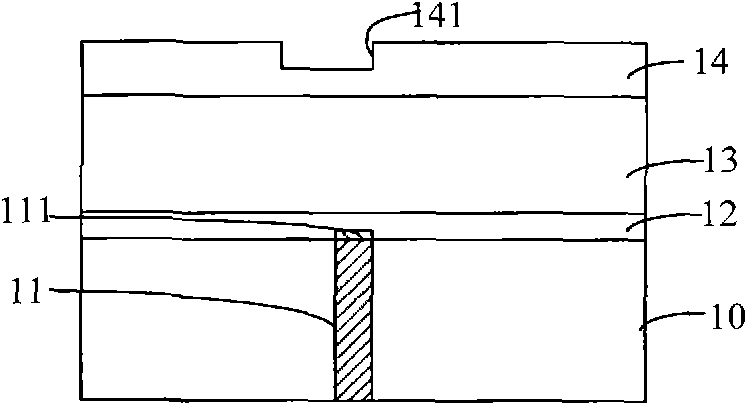

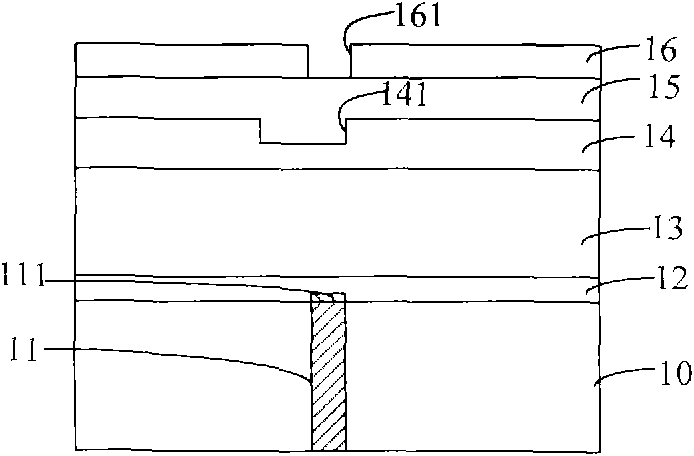

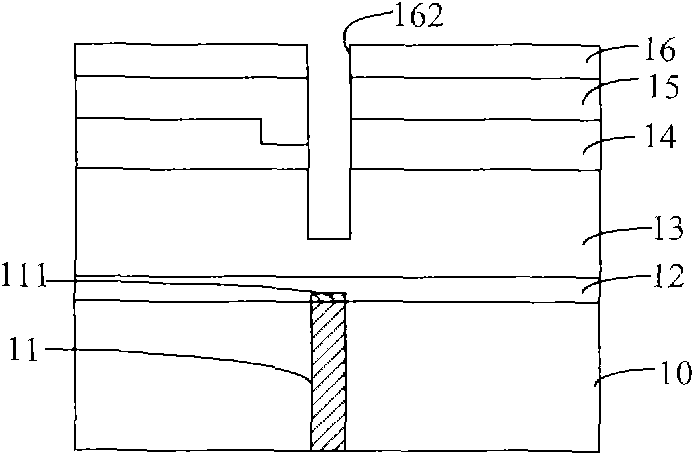

[0046] In the method for forming interconnect trenches and via holes according to specific embodiments of the present invention, in the process of forming interconnect trenches and via holes in the dielectric layer, the etch stop layer is not removed, and the etch stop layer separates the cap layer from the acid isolation so the acid does not corrode the cap layer as well as the copper. Afterwards, the etch stop layer is removed, and then the interconnection trenches and through holes are processed. The treatment method is: irradiating the interconnection trenches and through holes with ultraviolet rays, and injecting into the interconnection trenches and through holes. Ozone gas and water vapor, and then use an organic solvent to clean the interconnection trenches and via holes.

[0047] In order to enable those skilled in the art to better understand the present invention, specific embodiments of the present invention will be described in detail below in conjunction with the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More