Optimizing process of wafer-level packaging

A wafer-level packaging and process technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve problems affecting product reliability, and achieve the effects of easy control, low cost, and short process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

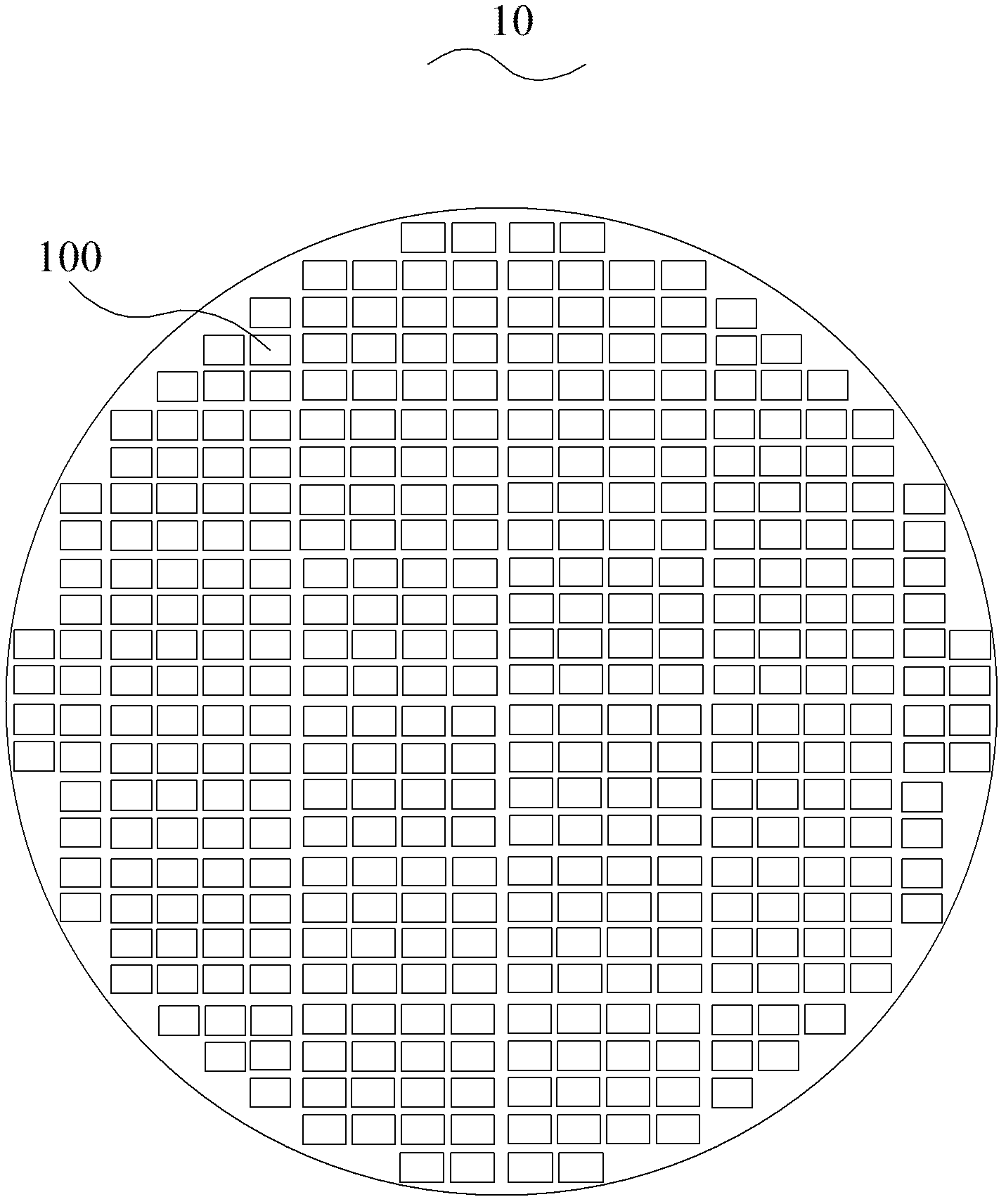

[0032] figure 2 It is a flow chart of a specific embodiment of the wafer-level packaging optimization process of the present invention, including steps:

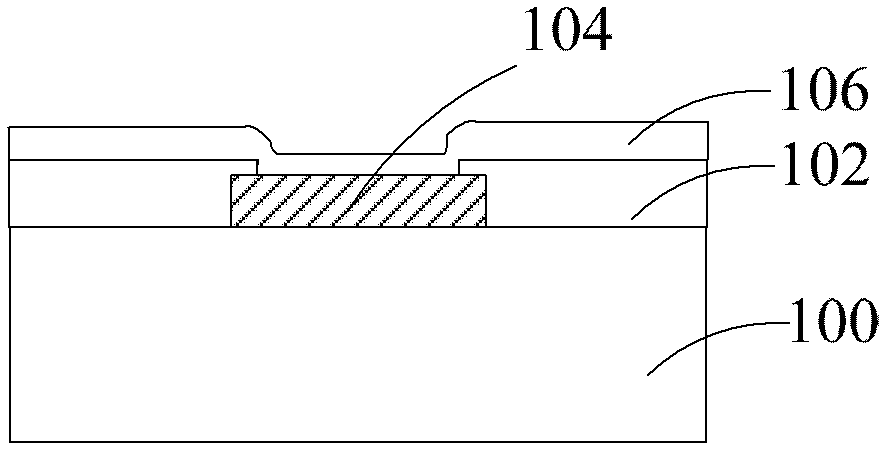

[0033] S101, forming a bonding metal bump on the pad of the chip, the bonding metal bump being higher than the surface of the passivation layer;

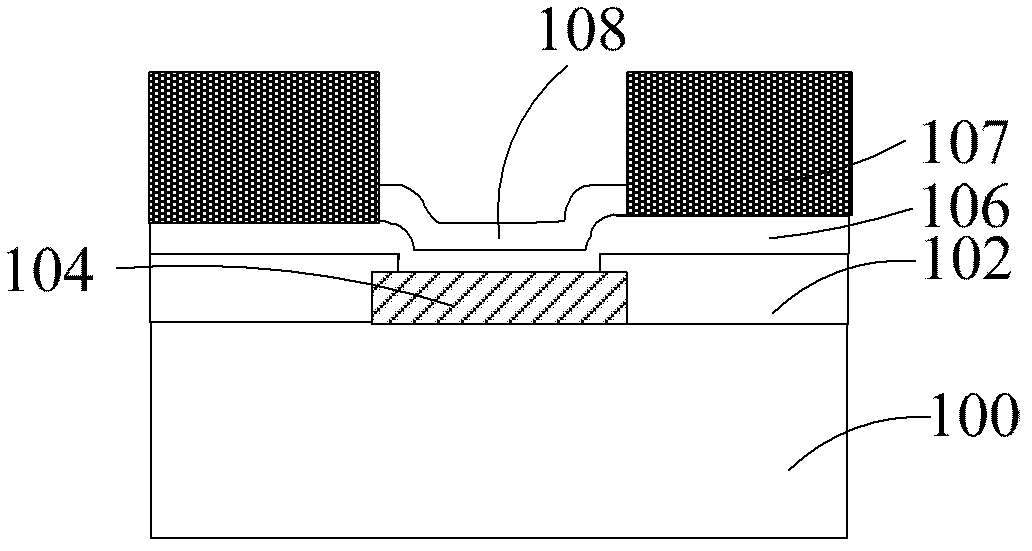

[0034] S102, forming a protective glue on the chip, the protective glue covering the passivation layer and the bonding metal bump;

[0035] S103, grinding the protective adhesive layer to expose the surface of the bonding metal bump;

[0036] S104, forming solder bumps on the surface of the exposed bonding metal bumps and reflowing them;

[0037] First, step S101 is performed to form a bonding metal bump on the pad of the chip, and the bonding metal bump is higher than the surface of the passivation layer, forming such as Figure 3A struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More