A method of high-speed interconnection between fpga boards based on aurora protocol

A high-speed interconnection and protocol technology, applied in the computer field, can solve the problems of data influx, rate limitation, and poor scalability, and achieve the effect of facilitating interconnection, eliminating bandwidth limitations, and reducing design difficulty.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

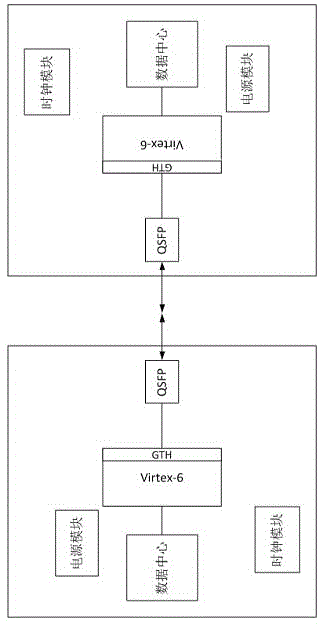

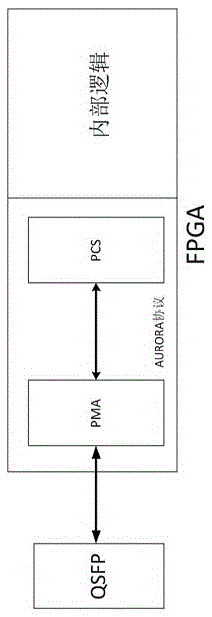

[0018] 1. Data processing and transmission process: The optical fiber signal from another board first enters the optical fiber jumper module QSFP module, and then extracts data through the aurora protocol protocol in the field programmable gate array FPGA. The specific data processing is that the electrical signal enters the field. Program the moving average PMA of the gate array FPGA, perform parallel-to-serial conversion of data in the moving average PMA, perform data and clock recovery, and then the data stream enters the batch processing module PCS, and performs block synchronization, descrambling code, and compensation in the batch processing module PCS , finally decoded, passed to the FPGA logic unit for use, and passed to the data center. Such as figure 2 shown;

[0019] 2. Data sending process: It is the opposite process to receiving data. The data from the FPGA internal logic is processed using the aurora protocol. The processing process is that the data enters the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More