Internet security and acceleration (ISA) interface internet protocol (IP) core based on processor local bus (PLB)

A bus and interface technology, applied in the field of ISA interface IP core, can solve the problems of low speed, reusable and upgradeable complex logic control, difficult implementation, etc., achieve low power consumption, free expansion of modules, and reduce operating burden Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Embodiments of the present invention are described in further detail below in conjunction with the accompanying drawings:

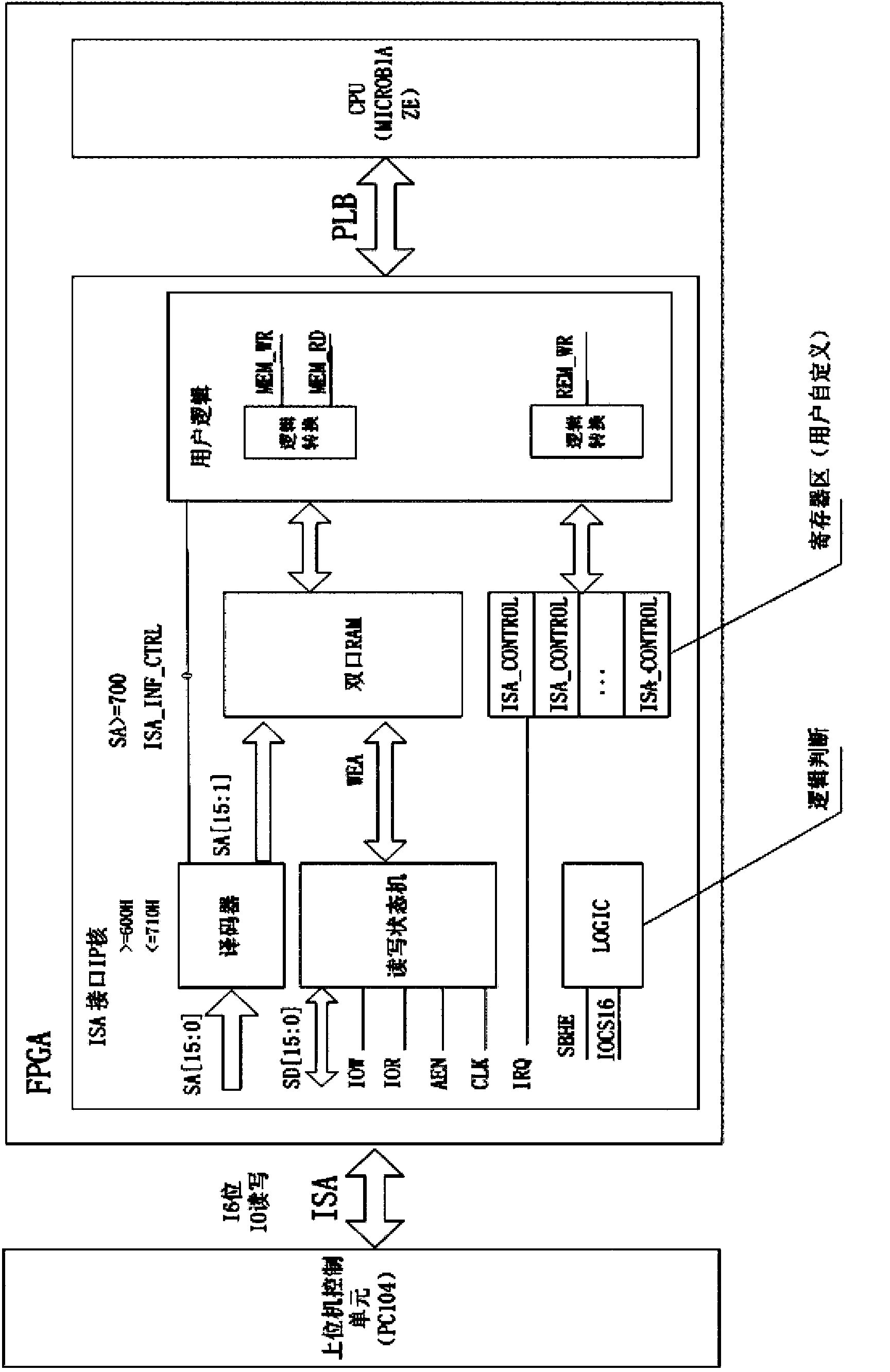

[0025] A kind of ISA interface IP core based on PLB bus, such as figure 1 As shown in the figure, it includes a decoder, a dual-port RAM, a register array, a read-write state machine, a logic judgment module and a user logic module; the decoder is connected to the user logic module through a control line, and the decoder is connected to the dual port through an address line. The RAM is connected with the register array; one end of the user logic module is connected with the PLB bus, and the other end of the user logic module is connected with the dual-port RAM and the register array respectively through the bidirectional data line; the input end of the read-write state machine is connected with the ISA bus. IO read and write signal (IOR, IOW signal), DMA control signal (AEN signal), clock signal (CLK signal) are connected, and the control signal (W...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More