Low-power-consumption xor/xnor gate circuit

A gate circuit, low-power technology, applied in the field of low-power XOR/XOR gate circuits, can solve the problems of increasing the number of transistors and circuit power consumption, and achieve the effect of reducing the number of transistors and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0024] Embodiment 1: As shown in the figure, a low-power XOR / XOR gate circuit includes an input inverter module 1, a complementary transmission tube logic module 2 and a differential series voltage switch logic module 3, and the input inverter module 1 includes the first PMOS transistor P1, the first NMOS transistor N1, the second PMOS transistor P2 and the second NMOS transistor N2, and the complementary transmission transistor logic module 2 includes the third NMOS transistor N3, the fourth NMOS transistor N4, and the fifth NMOS transistor N5 and the sixth NMOS transistor N6, the differential series voltage switching logic module 3 includes a third PMOS transistor P3 and a fourth PMOS transistor P4, the source of the first PMOS transistor P1, the source of the second PMOS transistor P2, the third PMOS transistor P3 The source of the fourth PMOS transistor P4 and the source of the power supply positive terminal V DD connected, the source of the first NMOS transistor N1 and th...

Embodiment 2

[0025]Embodiment 2: other parts are the same as Embodiment 1, the difference is: under the SMIC130nm standard process, the channel length of the first PMOS transistor P1, the channel length of the second PMOS transistor P2, and the channel length of the third PMOS transistor P3 The channel length, the channel length of the fourth PMOS transistor P4, the channel length of the first NMOS transistor N1, the channel length of the second NMOS transistor N2, the channel length of the third NMOS transistor N3, the channel length of the fourth NMOS transistor N4 The channel length, the channel length of the fifth NMOS transistor N5 and the channel length of the sixth NMOS transistor N6 are all 135nm.

Embodiment 3

[0026] Embodiment 3: other parts are the same as Embodiment 1, the difference is that: under the SMIC130nm standard process, the channel length of the first PMOS transistor P1, the channel length of the second PMOS transistor P2, and the channel length of the third PMOS transistor P3 The channel length, the channel length of the fourth PMOS transistor P4, the channel length of the first NMOS transistor N1, the channel length of the second NMOS transistor N2, the channel length of the third NMOS transistor N3, the channel length of the fourth NMOS transistor N4 The channel length, the channel length of the fifth NMOS transistor N5 and the channel length of the sixth NMOS transistor N6 are all 139nm.

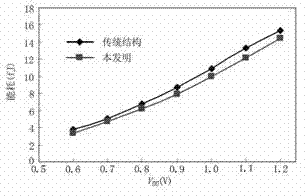

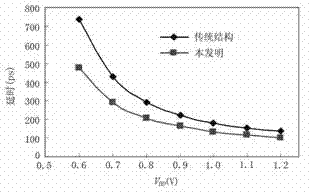

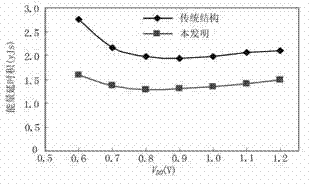

[0027] In order to compare the performance characteristics of the XOR / NOR gate circuit of the present invention with respect to the standard unit XOR gate circuit released by the SMIC130nm process, under the standard process of SMIC130nm, the circuit simulation tool HSPICE was used...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More