Silicon on insulator structure and semiconductor device structure

A silicon-on-insulator, device structure technology, applied in semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of parasitic capacitance that cannot meet product requirements, and parasitic capacitance becomes larger.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

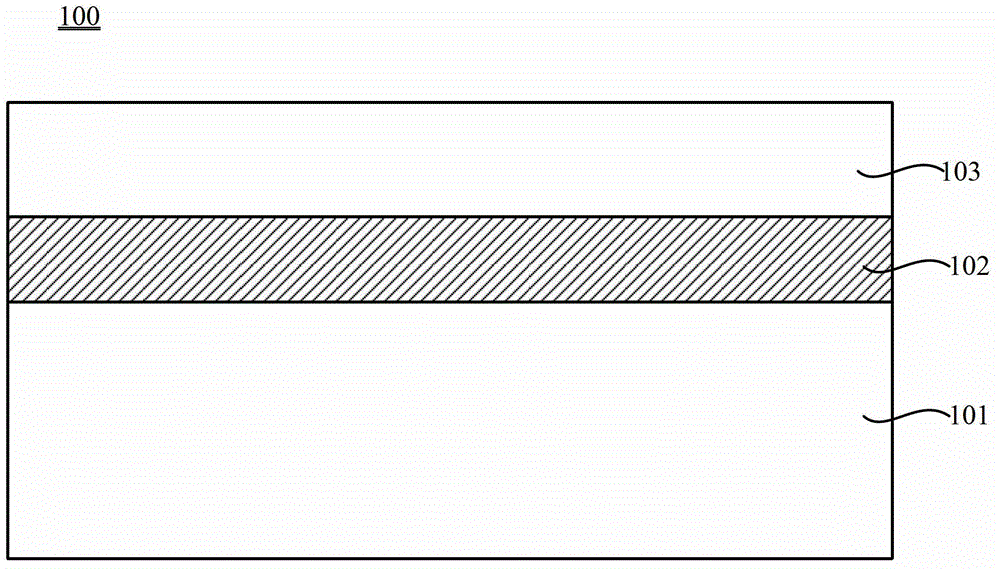

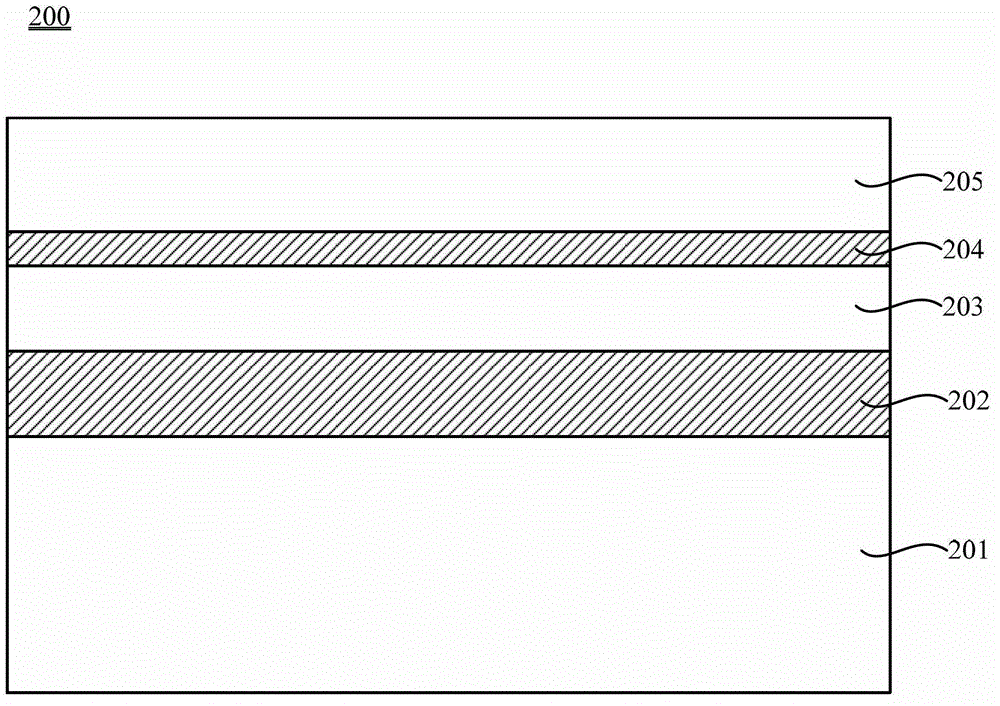

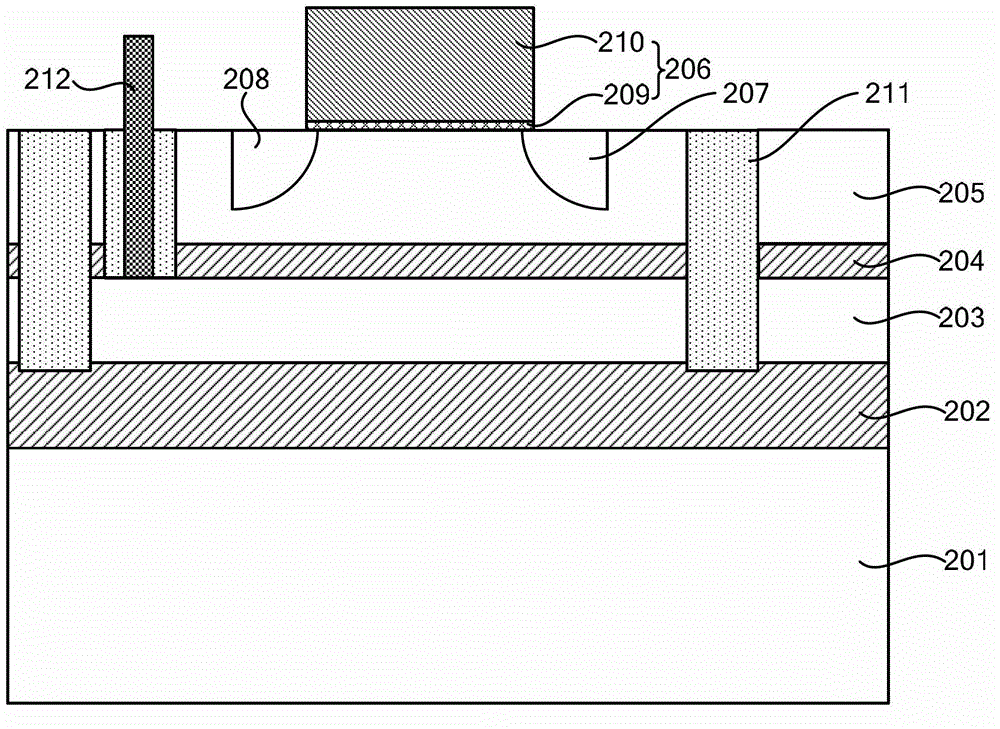

[0026] The core idea of the present invention is that two layers of buried oxide layers are included in the silicon-on-insulator structure, wherein the first buried oxide layer is used to isolate the electrical connection between the first silicon layer and the third silicon layer. connection; while the second buried oxide layer is used for some kind of insulating layer of the semiconductor device, so it is the second buried oxide layer that mainly affects the parasitic capacitance of the semiconductor device. In the above silicon-on-insulator structure, a better isolation effect can be achieved by thickening the thickness of the first buried oxide layer, and at the same time, by reducing the thickness of the second buried oxide layer, the isolation effect can be Next, the purpose of reducing the parasitic capacitance of the semiconductor device on the silicon-on-insulator structure is achieved.

[0027] In order to make the content of the present invention clearer and easie...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More