Digital time delay lock loop circuit

A technology of digital delay and locked loop, which is applied in the direction of electrical components, automatic power control, etc., can solve the problems of long cycle number, delay locked loop error locking, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

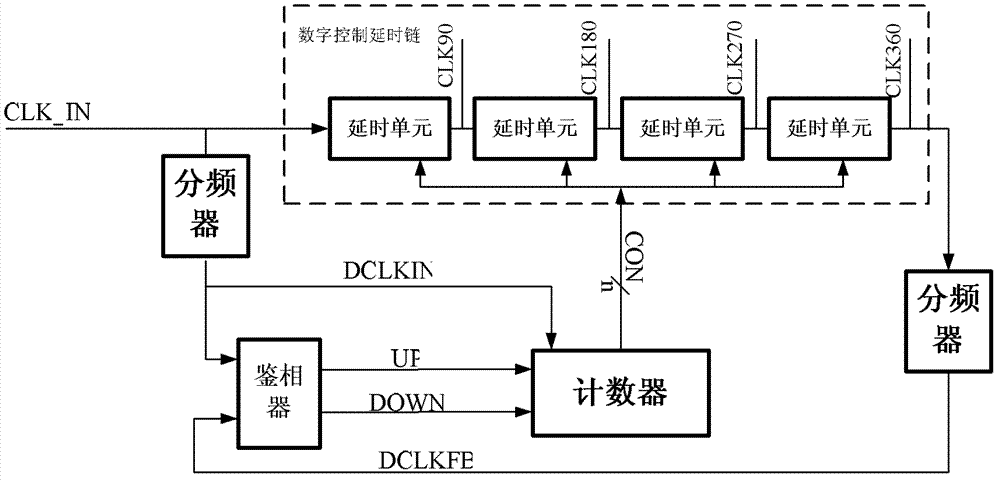

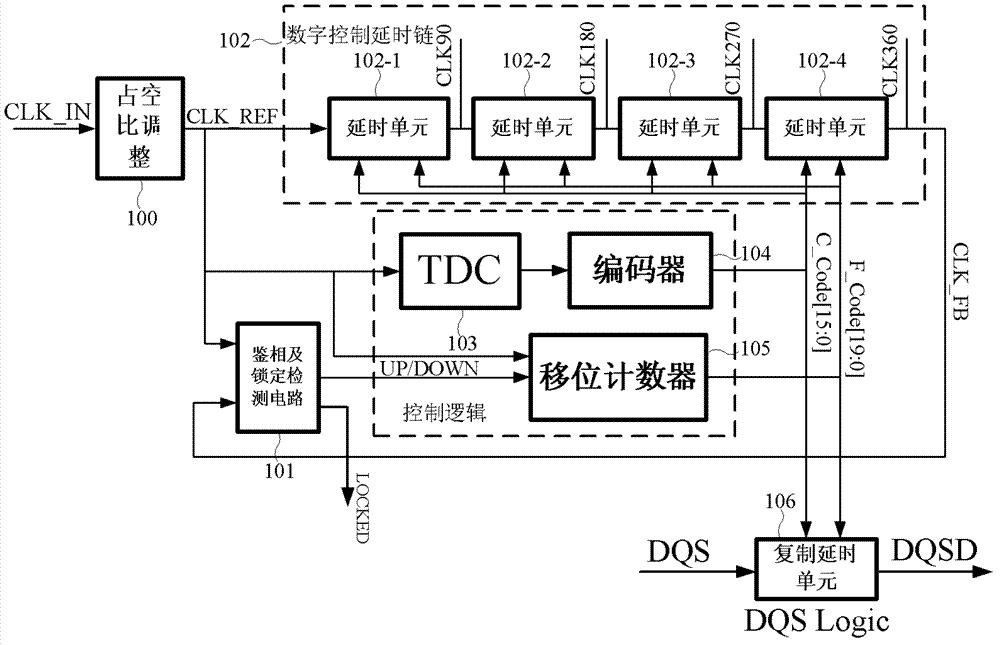

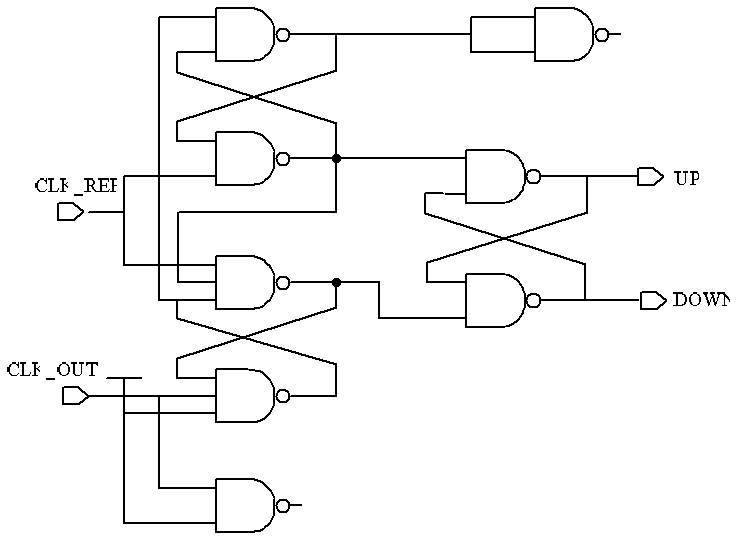

[0040] see figure 2 , 5 , 8, a kind of fast locking digital time-delay locked loop circuit of the present invention, comprises duty cycle adjustment circuit 100, phase discrimination and lock detection circuit 101, digital control delay chain 102, digital time converter 103, shift counter 105 and copy delay unit 106. The duty cycle adjustment circuit is connected to the input clock and the reference clock; the reference clock is input to one end of the phase detector, the input end of the digital control delay chain and the input end of the time-to-digital converter; the output of the digital control delay chain is connected to the phase detector The other input end of device; The output of phase detector connects the input end of shift counter; The control word that the time-to-digital converter output produces after encoder 104 receives the coarse adjustment delay unit 108 in the digital control delay chain Control word input end; the output control word of the shift coun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More