Zero dead area grid driving circuit

A gate drive circuit, zero dead zone technology, applied in electrical components, electronic switches, pulse technology, etc., can solve problems such as large electromagnetic interference, increased power consumption, diode voltage jumps, etc., to reduce electromagnetic interference and prevent loss. and electromagnetic interference, the effect of improving system efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

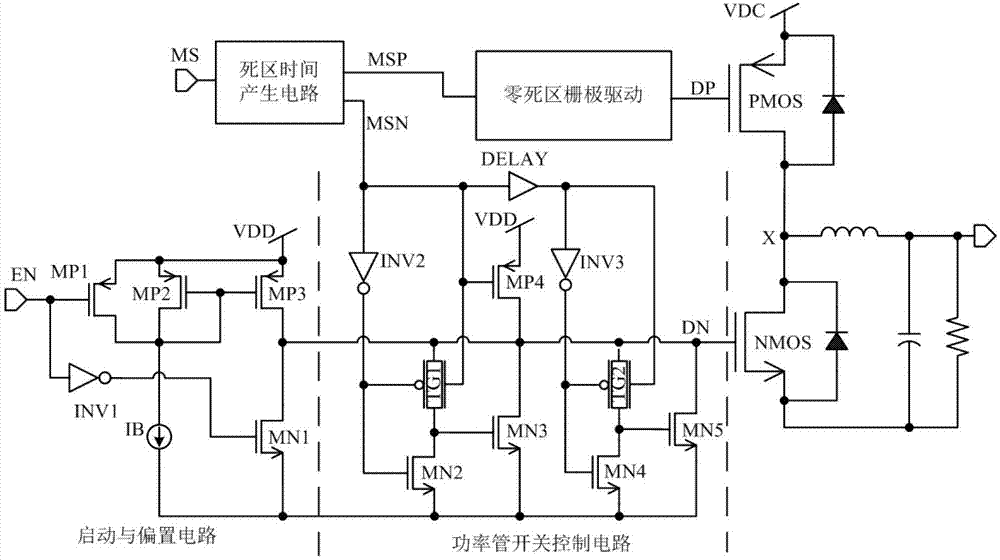

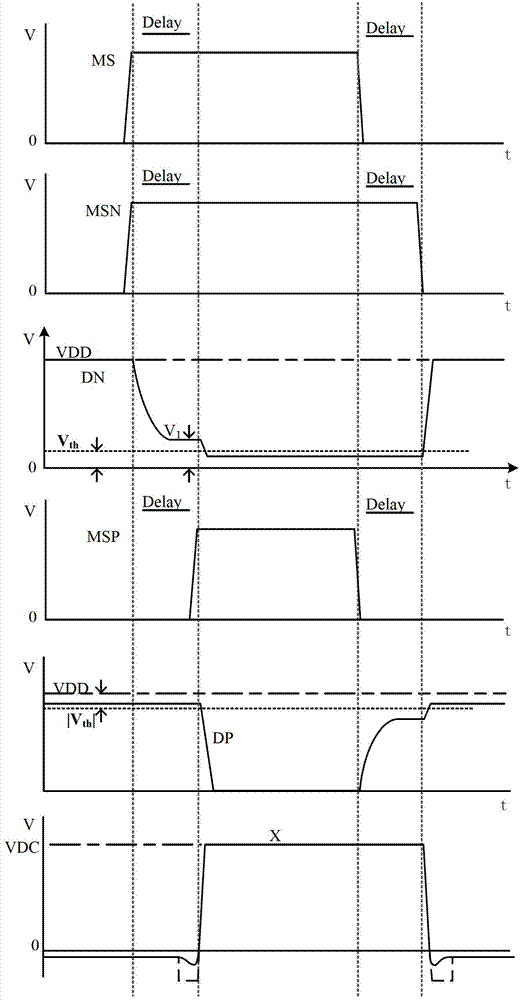

[0021] see figure 2 , is the zero-dead zone gate drive circuit of the present invention, and is used in a typical structure of a step-down voltage stabilizing circuit. The PMOS power transistor gate drive circuit and the NMOS power transistor gate drive circuit in the step-down voltage stabilizing circuit have similar structures, and both are composed of the zero dead zone gate drive circuit of the present invention. The PMOS power transistor gate drive circuit is connected between the dead time generation circuit and the PMOS power transistor, and the MOS power transistor gate drive circuit is connected between the dead time generation circuit and the NMOS power transistor gate, figure 2 Only shows the structure of NMOS power tube gate drive circuit. figure 2 In the circuit shown, except for the inductor L, the capacitor C and the load R, other components are integrated in the same chip to form a step-down regulator circuit of this example.

[0022] The gate drive circui...

Embodiment 2

[0029] In this example, the zero-dead zone gate drive circuit is used in a push-pull output circuit using PMOS power transistors and NMOS power transistors, such as various push-pull power amplifier circuits composed of field effect transistors, which constitute the gates of PMOS power transistors and NMOS power transistors. Drive circuit. The circuit of this example can also use integrated circuit technology to integrate the zero-dead zone gate drive circuit and the push-pull output circuit into the same chip to form a monolithic power amplifier.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More