Internal memory copying accelerating method and device facing multi-core microprocessor

A core microprocessor, memory copy technology, applied in machine execution devices, electrical digital data processing, instruments, etc., can solve the problems of low performance, low performance, long startup time of DMA equipment, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

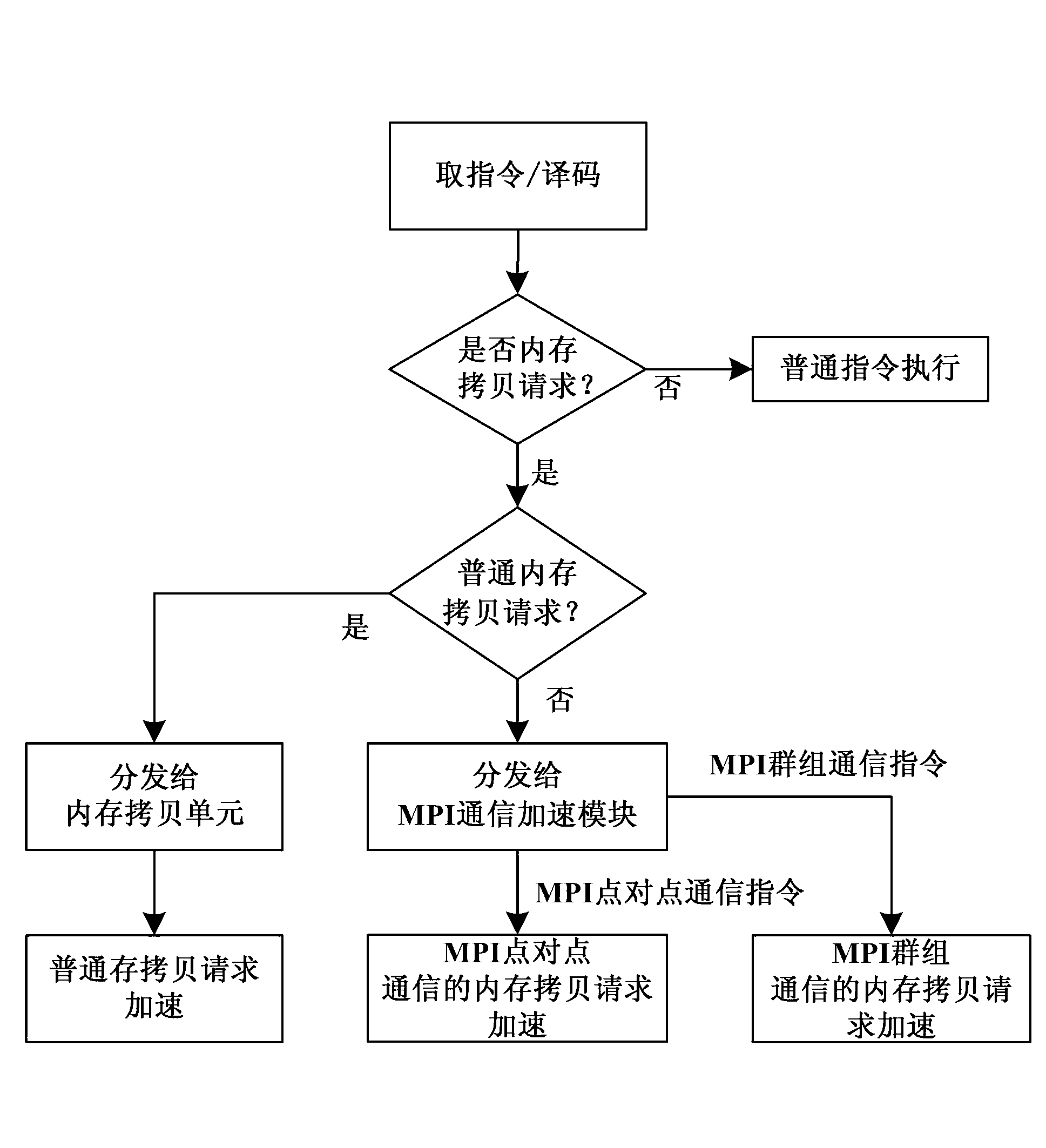

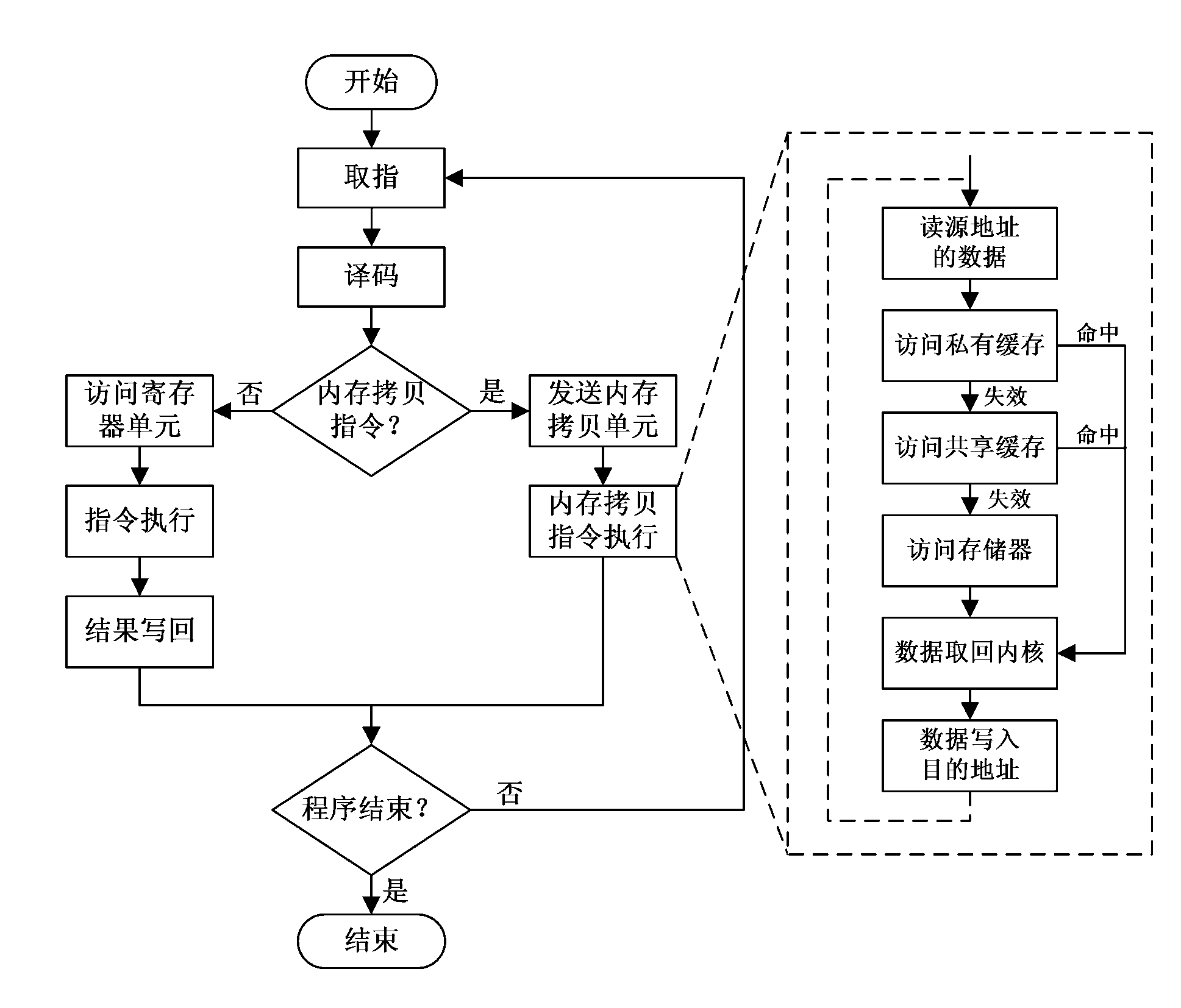

[0060] Such as figure 1 As shown, the implementation steps of the memory copy acceleration method for multi-core microprocessors in this embodiment are as follows:

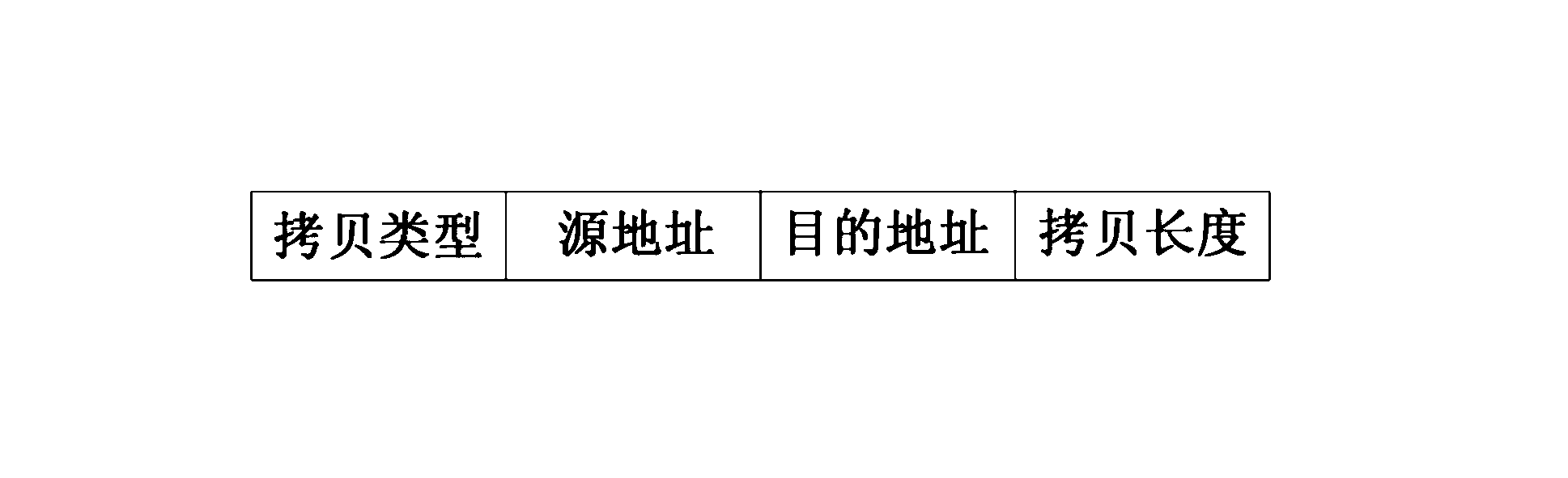

[0061] 1) Add memory copy instructions in the microprocessor instruction set, memory copy instructions include ordinary memory copy instructions, MPI point-to-point send instructions, MPI point-to-point receive instructions, MPI group send instructions and MPI group receive instructions; in the microprocessor An MPI communication acceleration module for executing memory copy requests based on MPI communication is established outside the instruction execution pipeline;

[0062] 2) Convert the decoded memory copy instruction into a corresponding memory copy request. If the current memory copy request is a normal memory copy request, distribute it to the memory copy unit in the instruction execution pipeline and jump to step 3); otherwise, it will The memory copy request is distributed to the MPI communication accel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com