Manufacture method of alignment mark protective layer

A production method and a technology of alignment marks, which are applied in the photolithography process of pattern surface, semiconductor/solid-state device manufacturing, optics, etc., can solve the alignment difficulties of lithography process, affect the alignment accuracy of lithography, and Poor alignment ability and other problems, to improve alignment accuracy and alignment ability, and solve the effect of lithography alignment difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

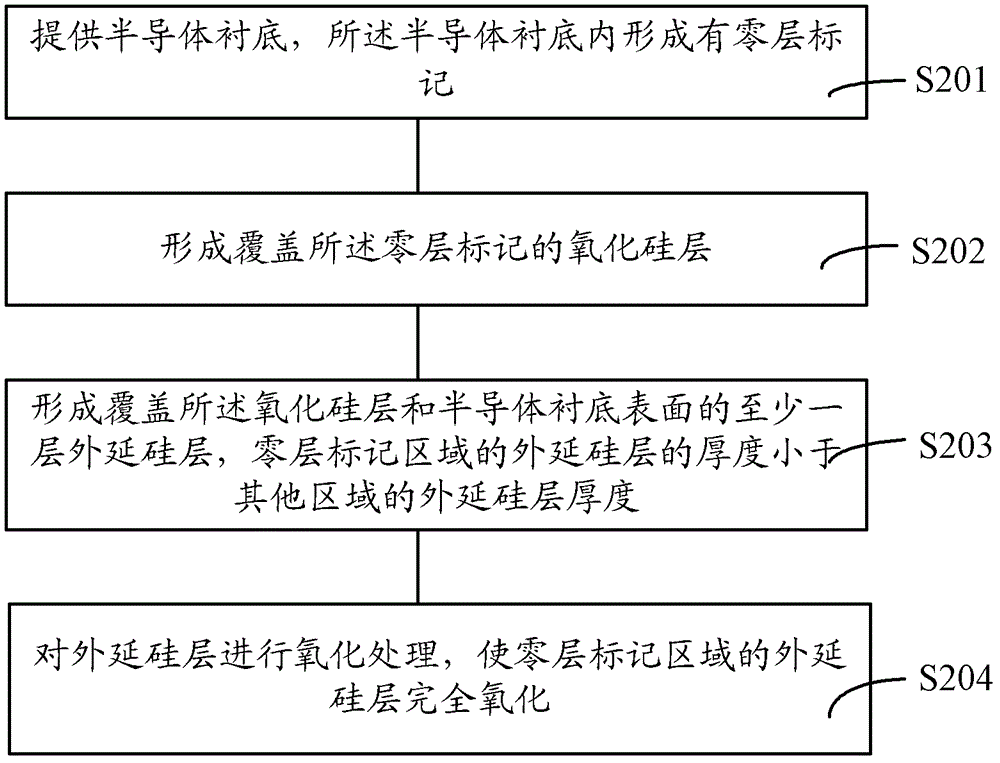

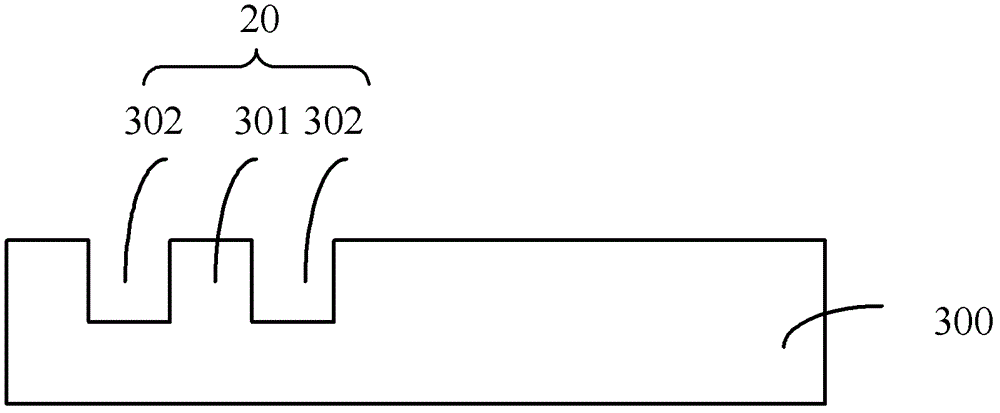

[0031] Existing super junction metal oxide layer semiconductor field effect transistors (Supper Junction MOSFET) generally need to carry out 5~7 times of epitaxial silicon layer growth process, photolithography process, and implantation process to form P-type and N-type doped regions, the inventors found During the alignment of the lithography process after the first silicon epitaxial layer process, the zero-layer mark step and shape received by the alignment sensor are relatively clear, and the alignment time has little influence on the alignment accuracy of the lithography, but in the second silicon epitaxial layer process During the alignment of the epitaxial layer growth process, especially the photolithography process after the 3rd to 7th silicon epitaxial layer growth process, the step and shape of the zero-layer mark received by the alignment sensor become less and less clear, and even deformed, which greatly It affects the accuracy of the alignment, resulting in the shi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More