Manufacturing method of high dielectric layer metal gate

A technology of high dielectric layer and manufacturing method, which is applied in the direction of semiconductor devices, can solve the problem of reducing the height of metal gates, and achieve the effect of increasing height, compensating losses, and ensuring height

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

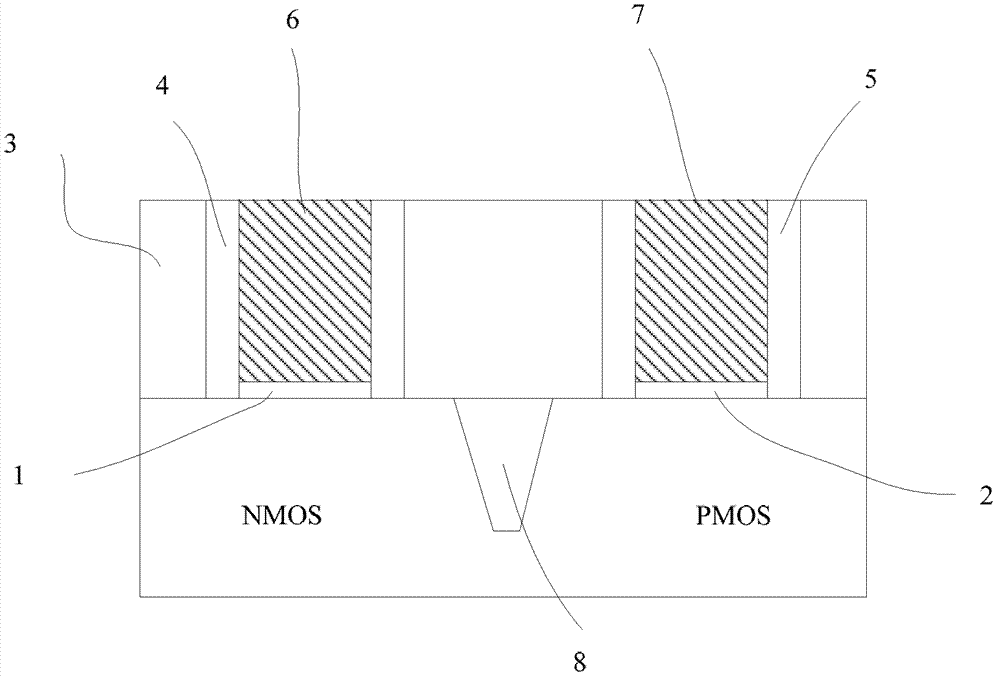

[0031] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

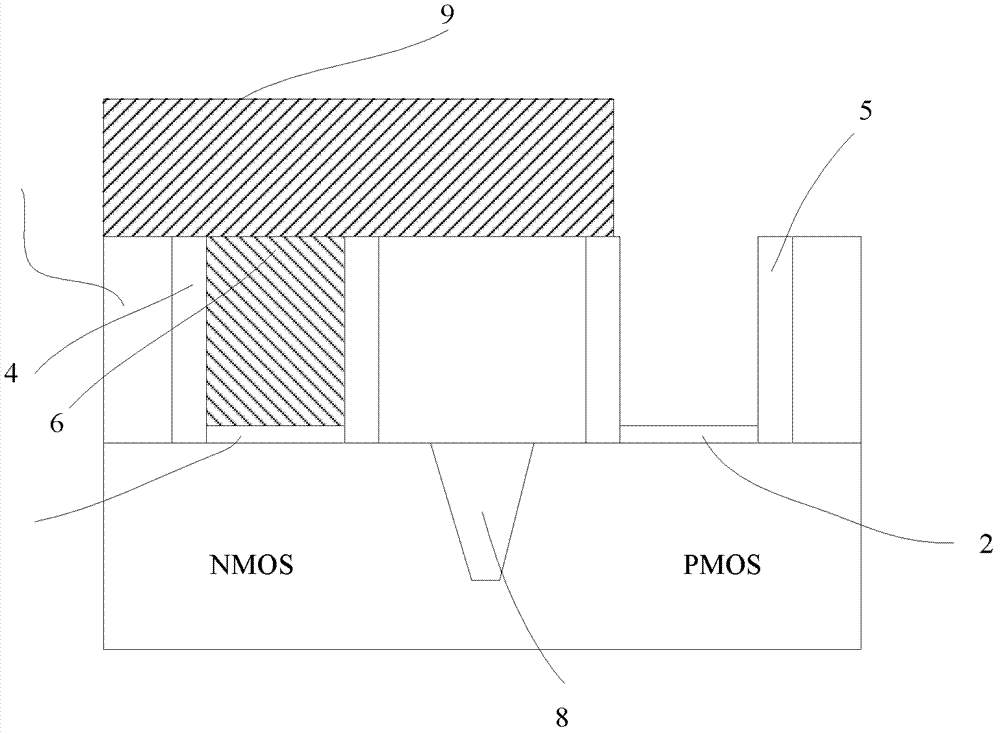

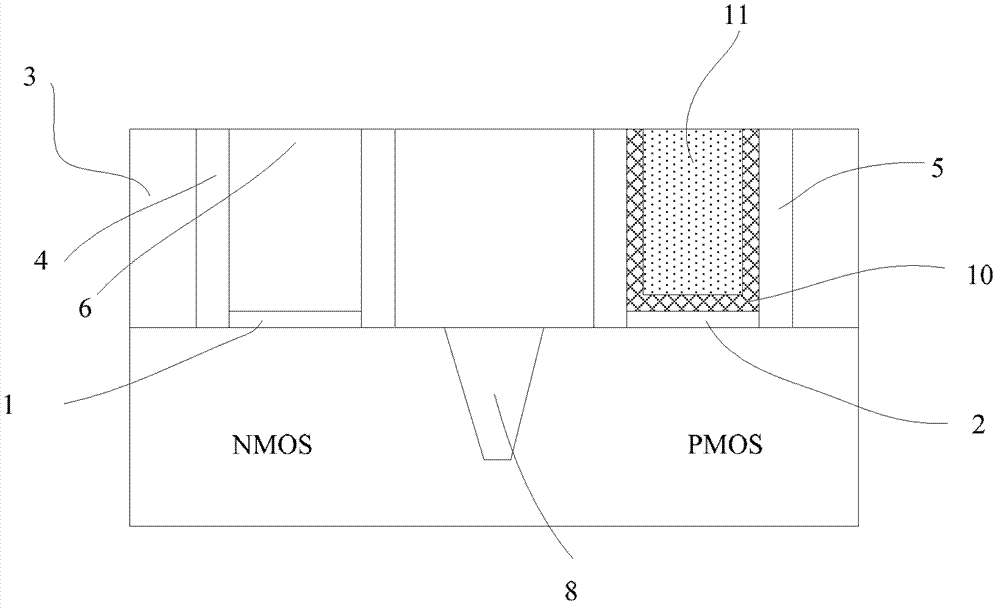

[0032] The technical means adopted in the present invention are realized based on the following concepts. In order to solve the problem of the reduction of the height of the metal gate caused by the loss of the interlayer insulating layer caused by the removal of pseudo-polysilicon by dry etching and the subsequent chemical mechanical polishing process, it is necessary to increase the interlayer insulation The thickness of the layer compensates for the loss caused by dry etching and chemical mechanical polishing.

[0033] Plasma-enhanced chemical vapor deposition using silane to form a seed layer on which selective chemical vapor deposition using ozone and tetraethylorthosilicate can achieve selective deposition, suc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More