Encapsulation structure of silicon substrate pinboard

A packaging structure and adapter board technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of incomplete insulation layer coverage, high cost of packaging technology, slow speed, etc., to solve process problems and cost problems, The effect of improving product yield and reliability and reducing product cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

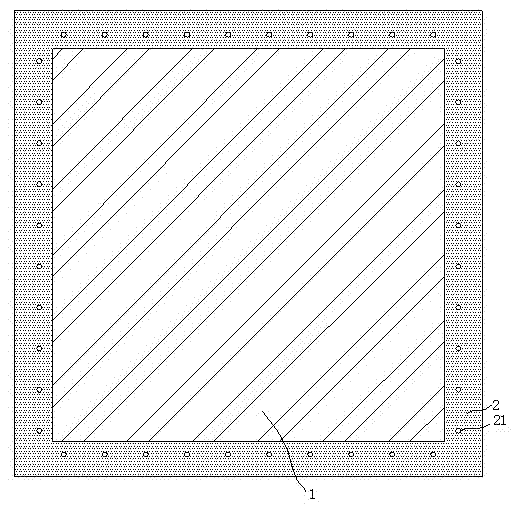

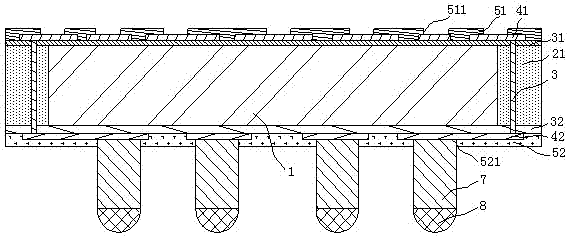

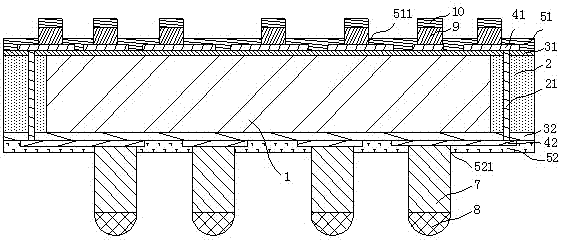

[0041] see Figure 2 to Figure 5 , The packaging structure of a silicon-based interposer in the present invention includes a silicon-based carrier 1, an insulating layer, a rewiring metal layer and a protective layer. An encapsulation area 2 is provided around the silicon-based carrier 1 , and the encapsulation area 2 is in encapsulation connection with the side of the silicon-based carrier 1 . The material of the encapsulation area 2 is resin, usually an epoxy resin material, which contains fillers to reduce the problem of a large difference in thermal expansion coefficient between the resin material and the silicon material, and improve the thermomechanical reliability of the structure. The encapsulation connection can be stepped, and single or multiple steps are used to increase the bonding area between the encapsulation material and the silicon-based carrier 1, thereby improving the bonding force between the encapsulation area 2 and the silicon-based carrier 1, as figure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com