Electro-static discharge (ESD) protective circuit

An ESD protection and circuit technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of poor anti-ESD ability, limit the application range, affect the discharge ability, etc., achieve small leakage current, suppress latch-up effect, The effect of strong anti-ESD ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

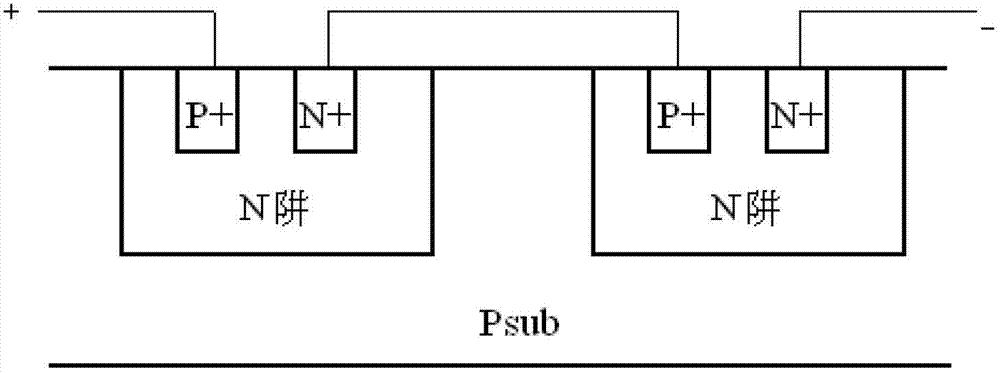

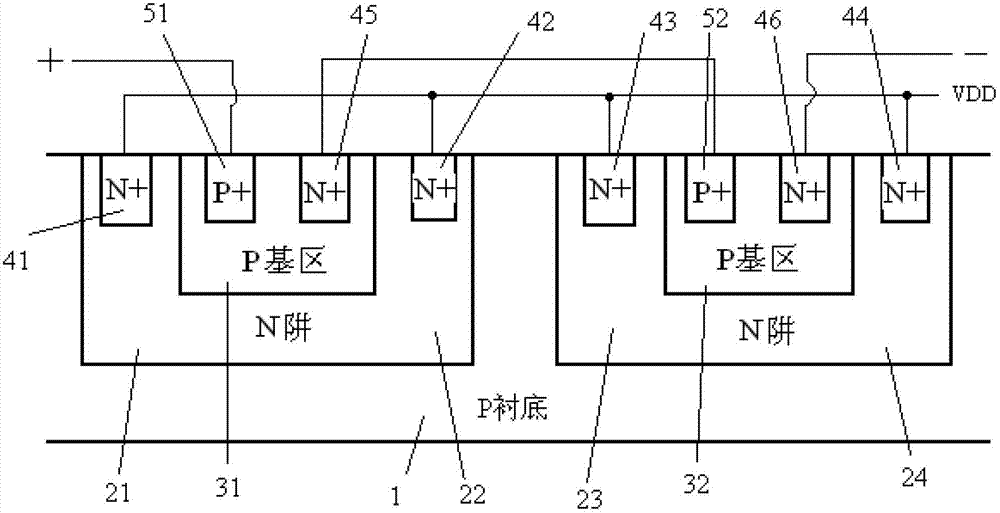

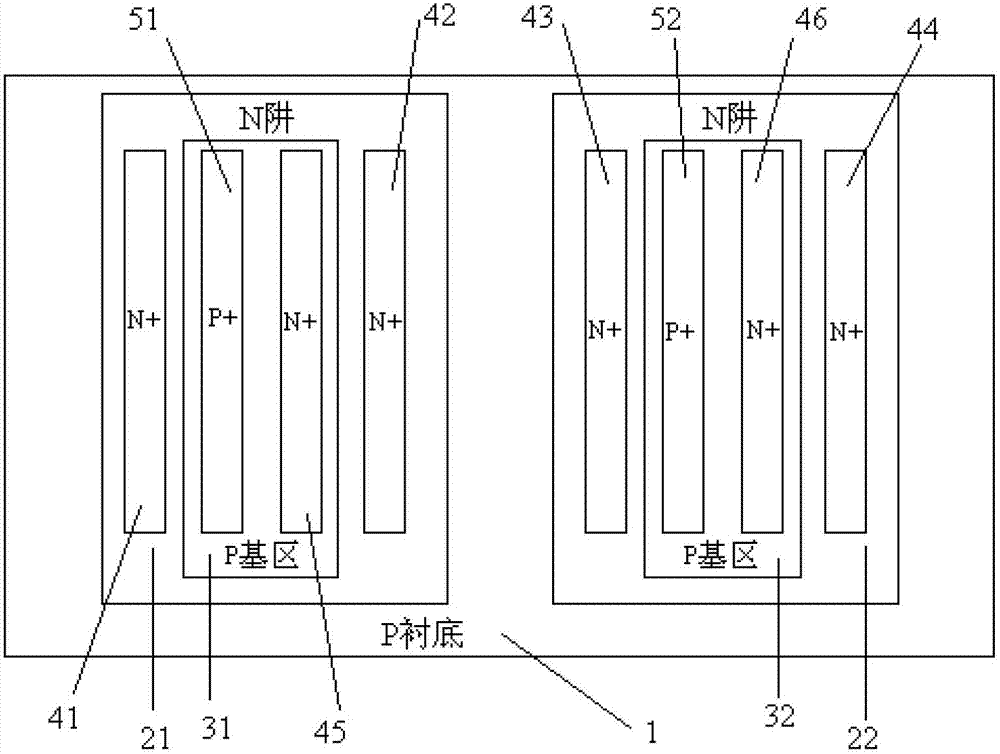

[0020] Such as figure 2 Shown is the schematic diagram of the cross-sectional structure of the ESD protection circuit of the present invention figure 1 , image 3 Shown is the structural representation of the ESD protection circuit of the present invention figure 2 ( figure 2 It can be seen from the figure that the ESD protection circuit of the present invention is a diode string structure that can suppress the Darlington effect, wherein one end of the P substrate 1 is provided with a first N well 21 and a second N well connected at the bottom 22, a first P base region 31 is provided between the first N well 21 and the second N well 22; the other end of the P substrate 1 is provided with a third N well 23 and a fourth N well 24 whose bottoms are integrated, A second P base region 32 is provided between the third N well 23 and the fourth N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More