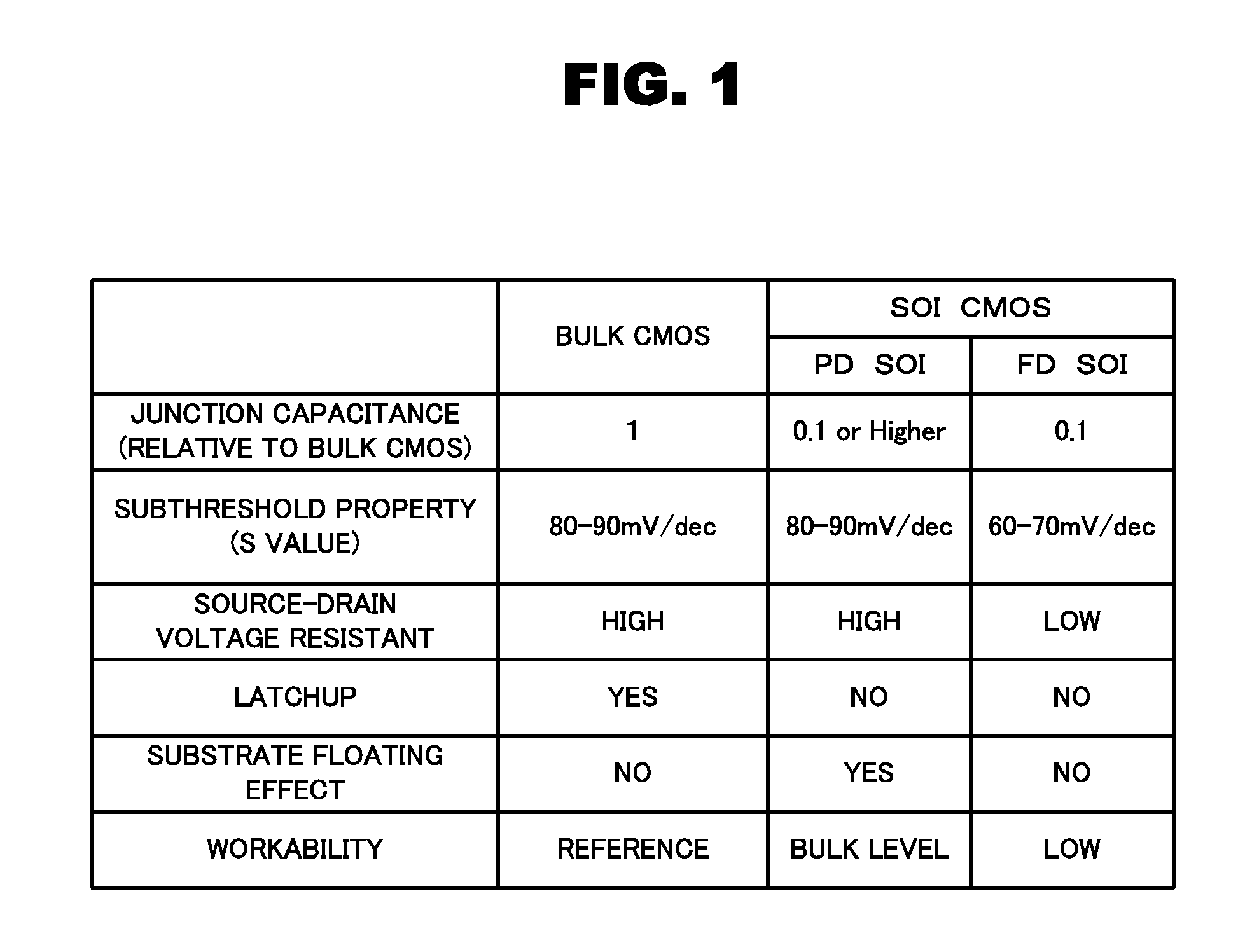

Patents

Literature

66results about How to "Increase junction area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Switching regulator

ActiveUS7002330B2Increase emitter-base junction areaDrive capabilityPower supply linesDc-dc conversionAudio power amplifierFeedback circuits

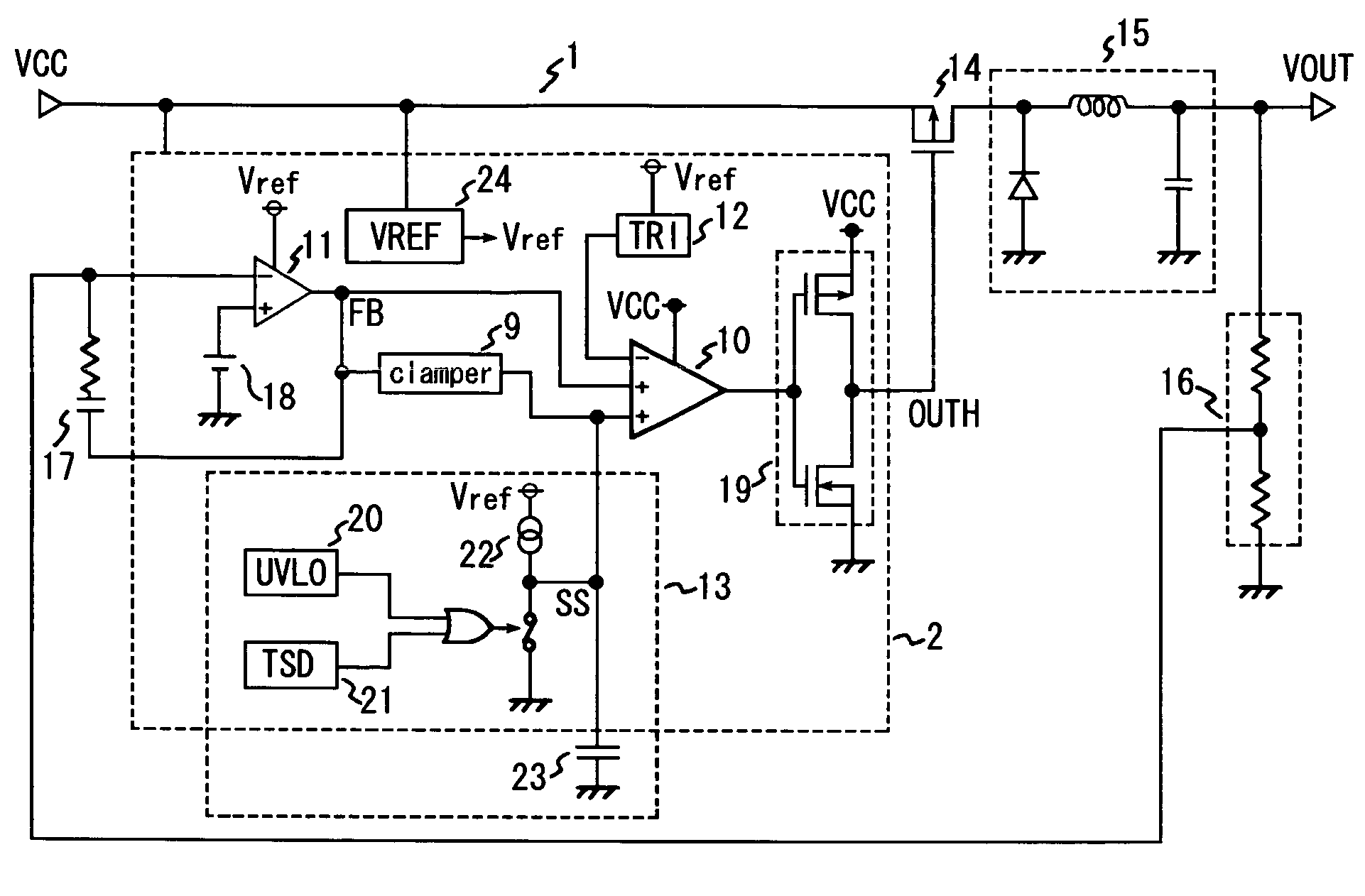

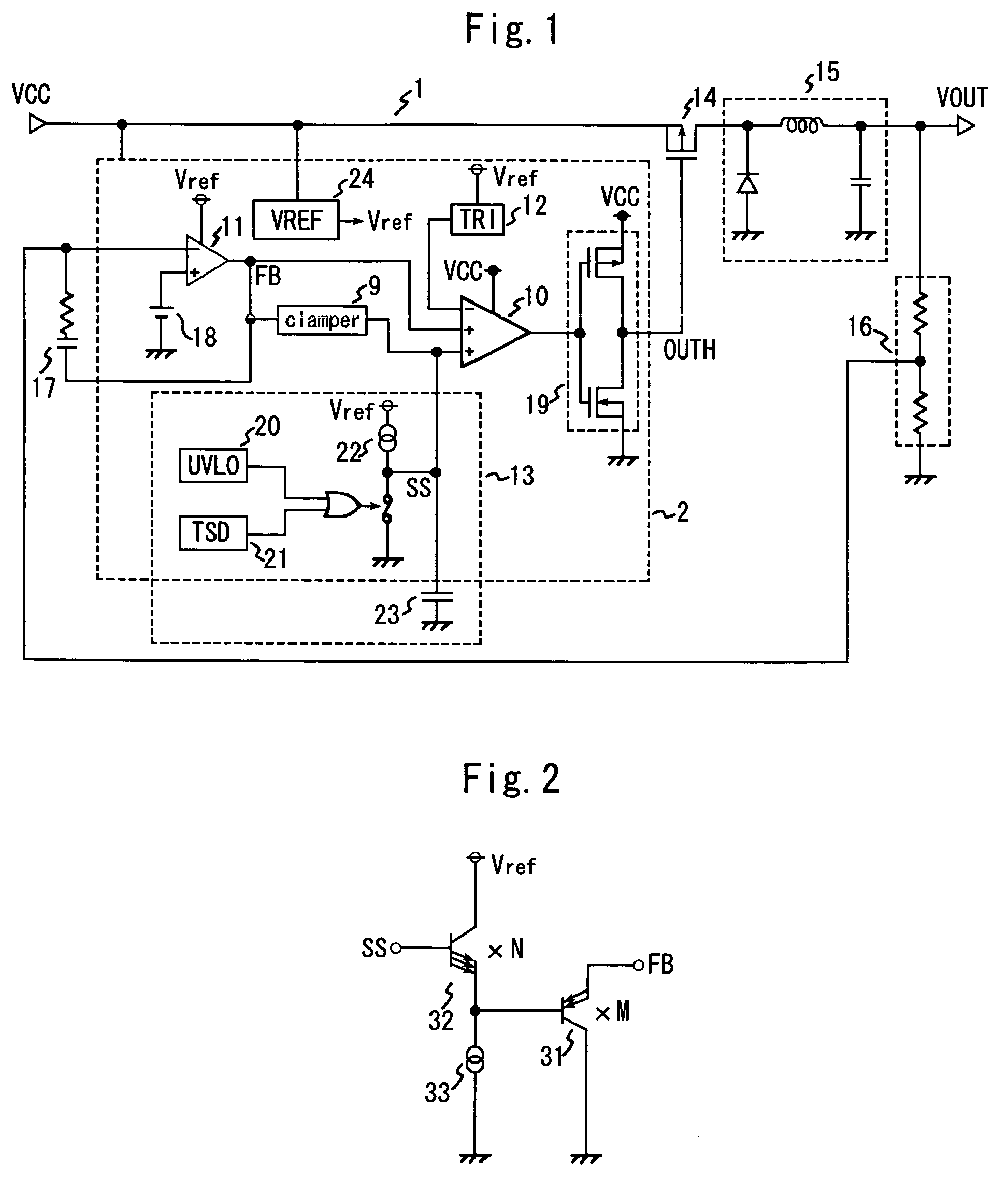

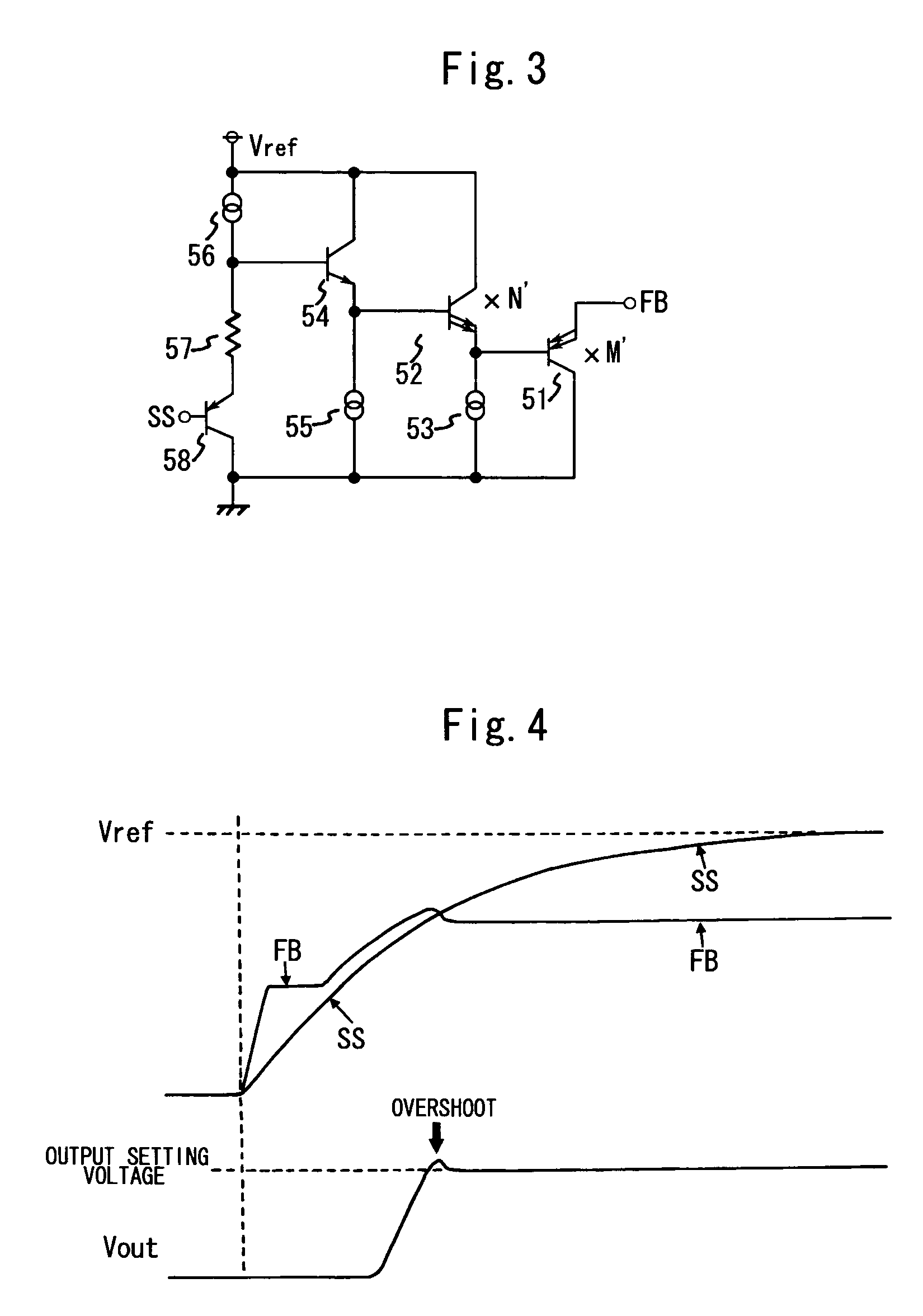

The present invention provides a switching regulator for controlling the overshoot voltage which is generated during transition from power ON, when soft start activates, to normal operation, when the load side output is maintained at the output setting voltage by the feedback circuit. A clamp circuit is disposed between a soft start circuit and an error amplifier, an upper limit value from the output of the soft start circuit (SS) to the output of the error amplifier (FB) is set, so that the rise of voltage of the output of the error amplifier (FB) is controlled when power is turned ON, and time until the output of the error amplifier (FB) is stabilized is decreased, by which the overshoot voltage generated in the load side output (VOUT) is controlled.

Owner:ROHM CO LTD

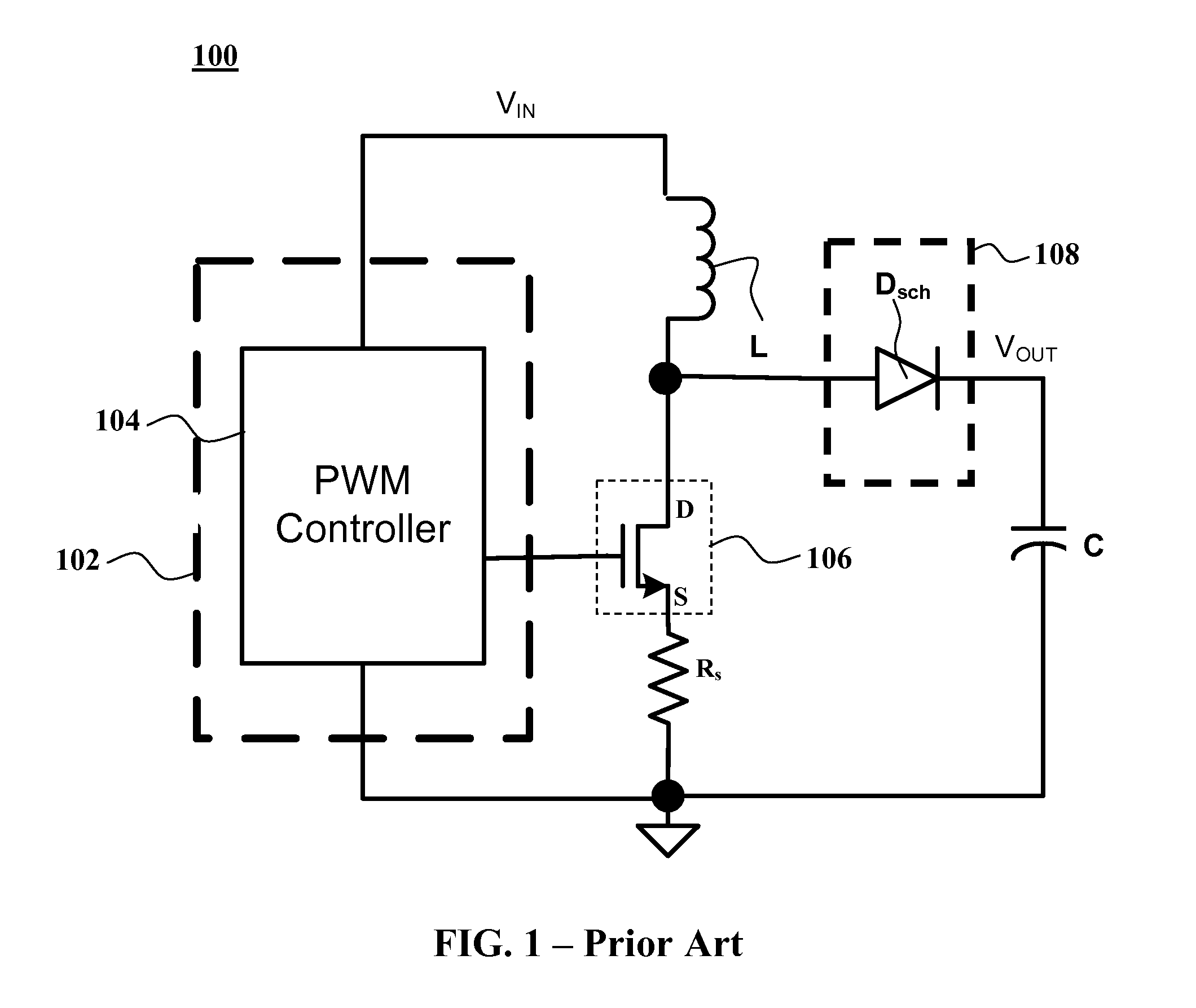

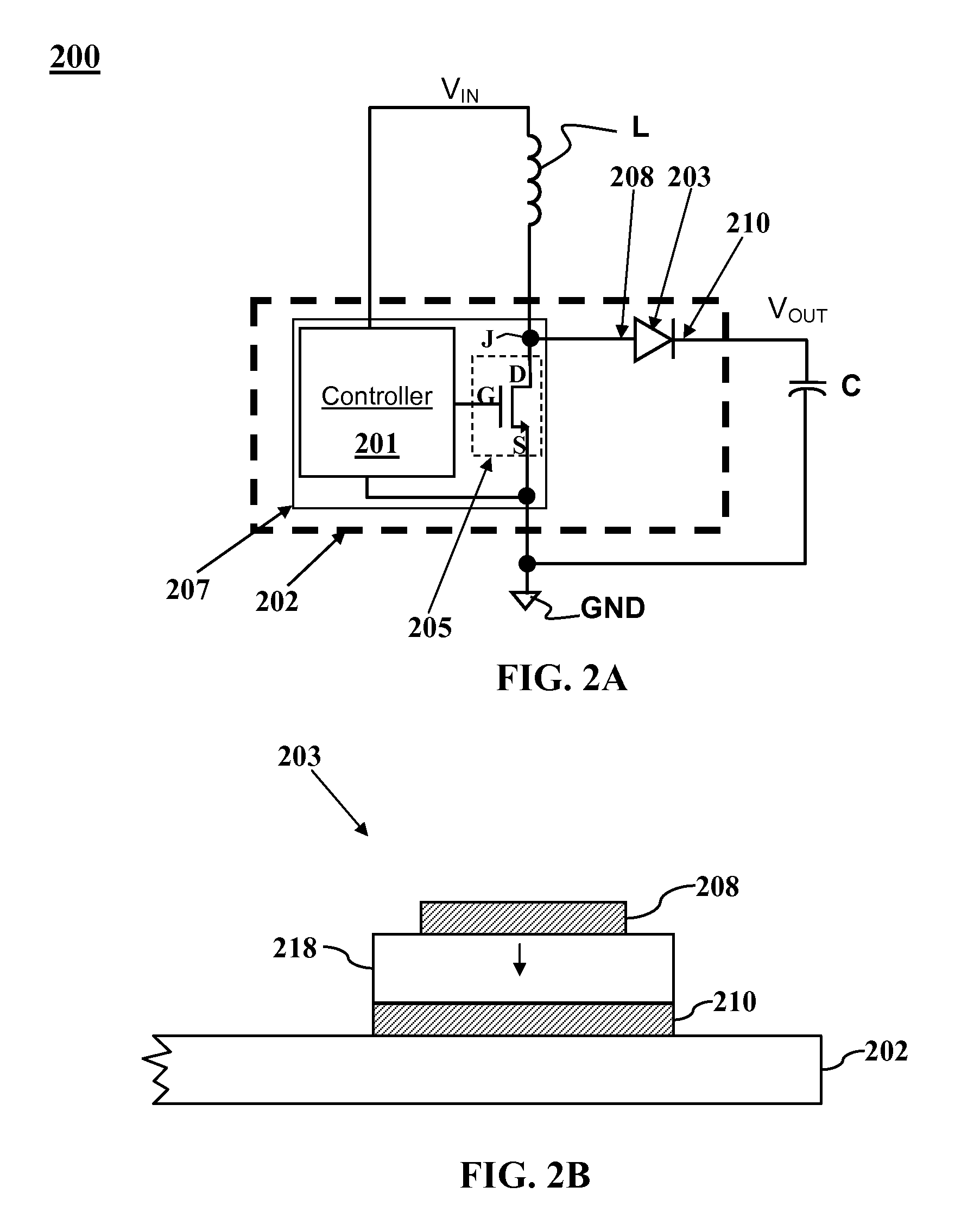

High voltage and high power boost converter with co-packaged Schottky diode

ActiveUS7750447B2High currentHigh voltageConversion constructional detailsSemiconductor/solid-state device detailsEngineeringHigh pressure

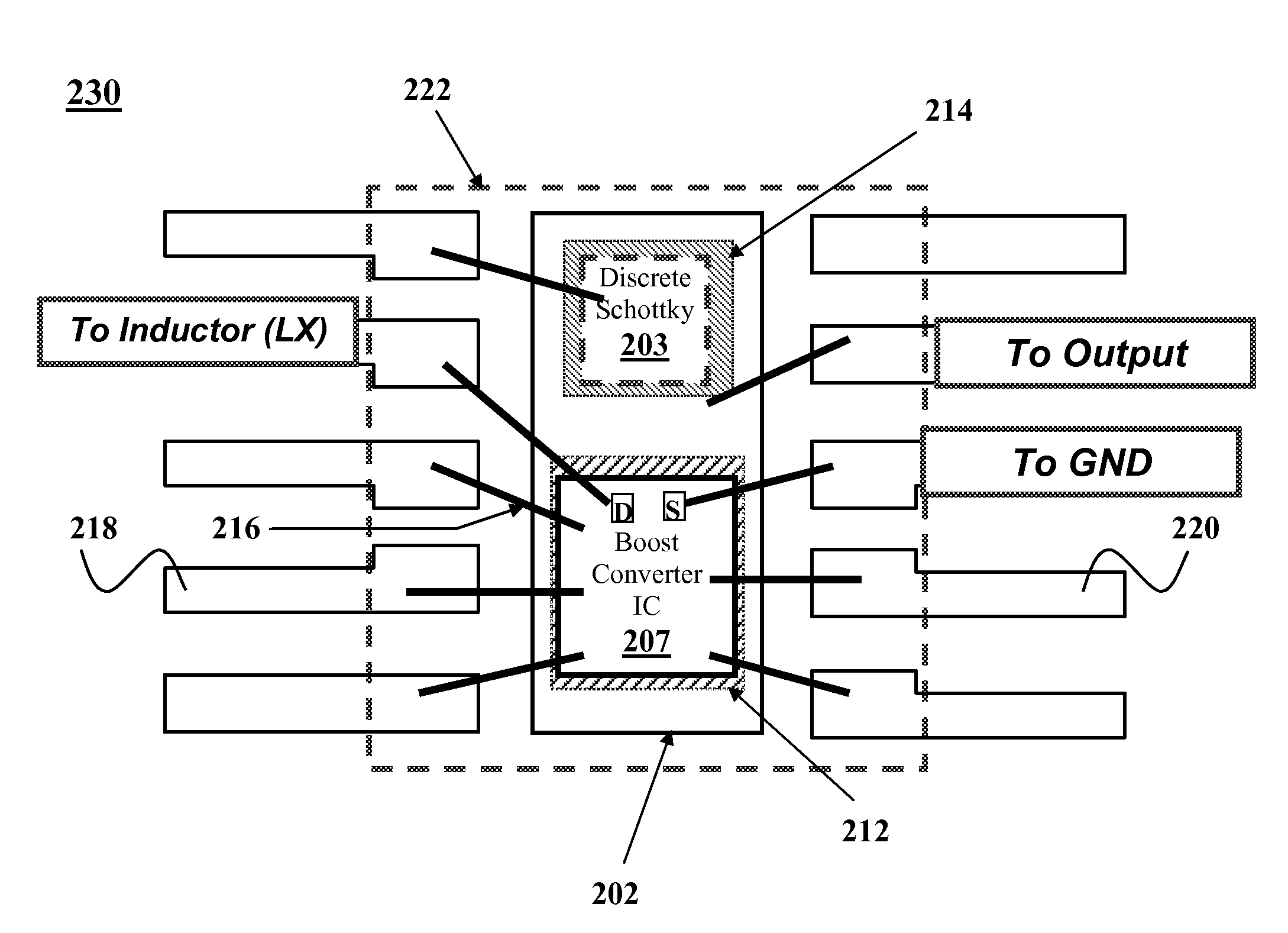

A high voltage and high power boost converter is disclosed. The boost converter includes a boost converter IC and a discrete Schottky diode, both of which are co-packaged on a standard single common die pad.

Owner:ALPHA & OMEGA SEMICON LTD

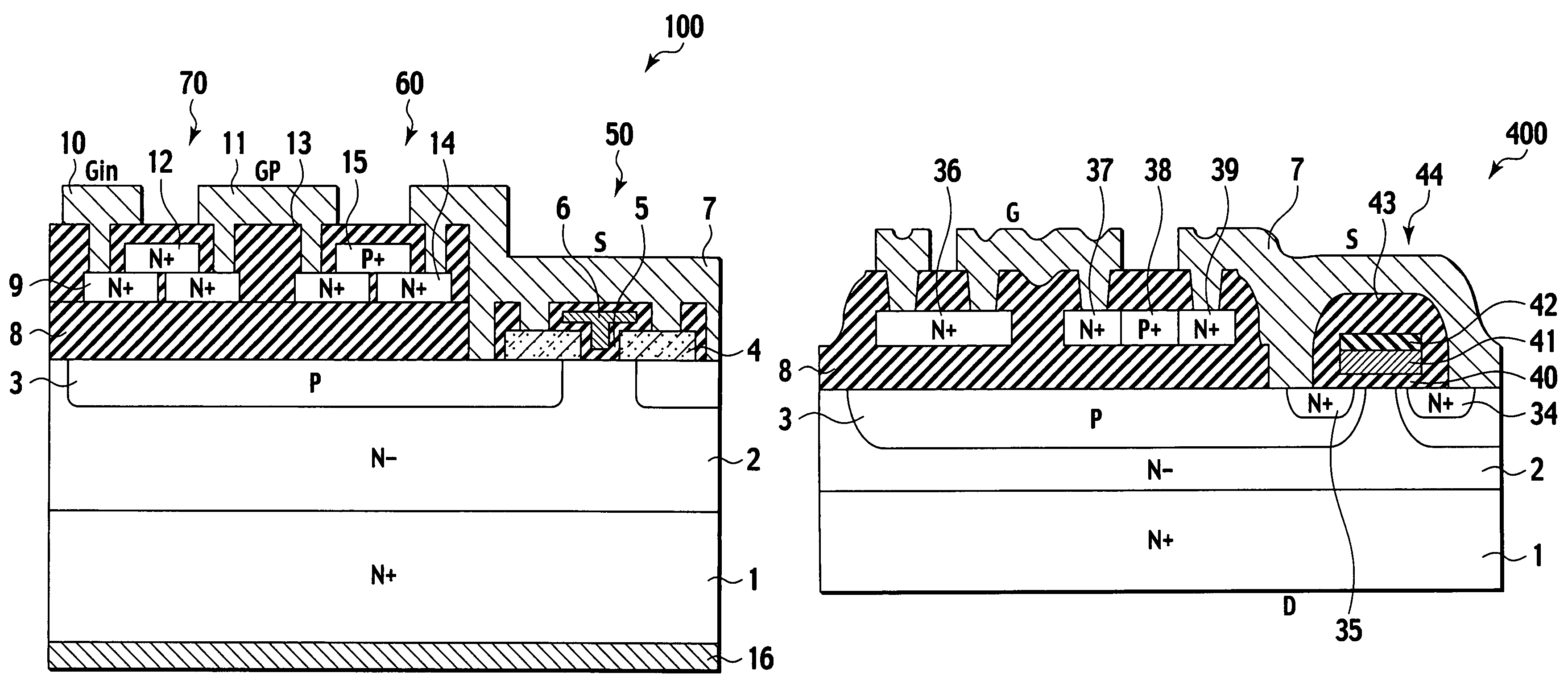

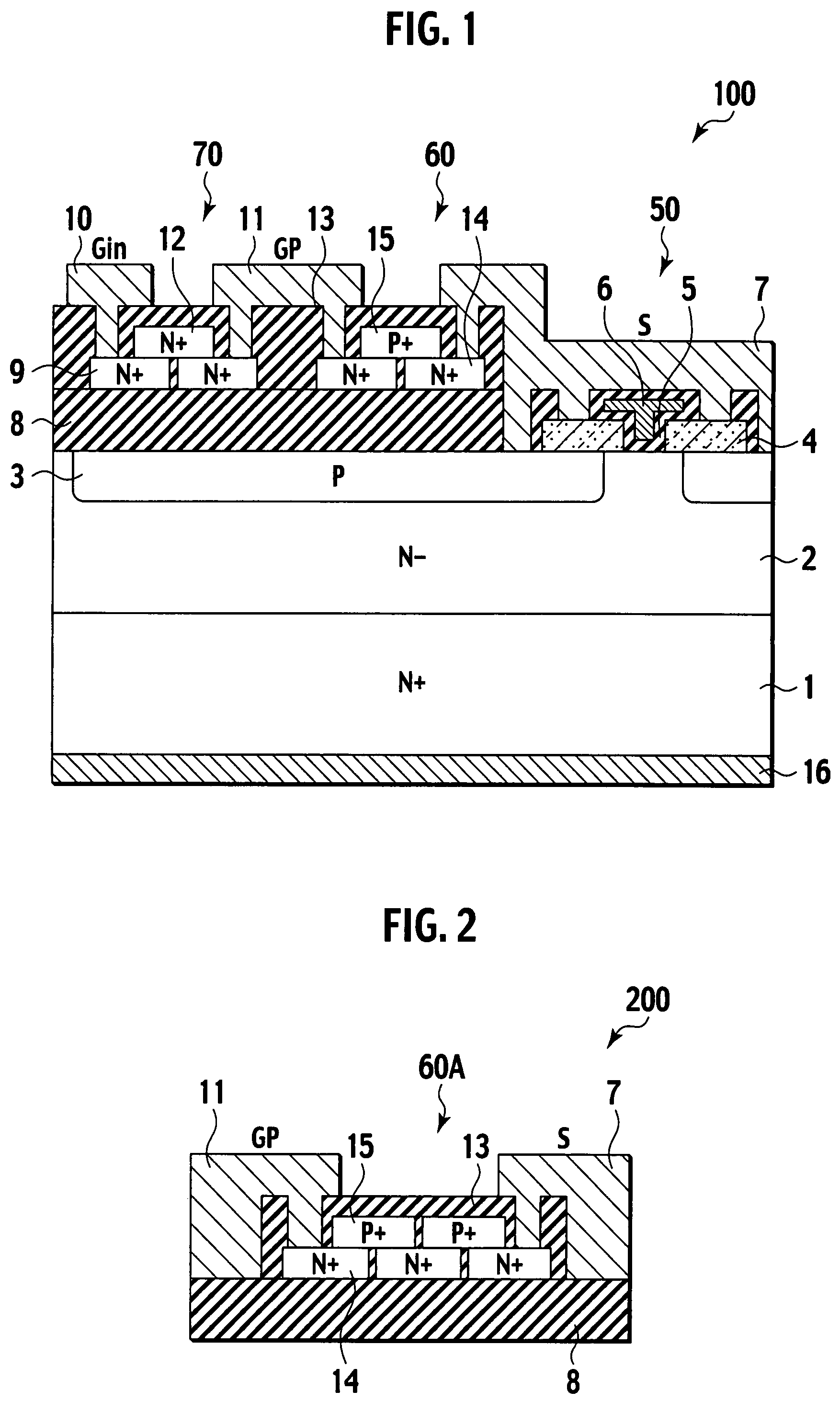

Semiconductor device and manufacturing method thereof

ActiveUS20070252168A1Increase junction areaIncrease the resistance valueThyristorSemiconductor/solid-state device manufacturingZener diodeField-effect transistor

An electrostatic discharge protection element and a protection resistor, which are formed on an N-drain region with a field oxide film interposed therebetween for the purpose of preventing electrical breakdown of a field effect transistor, are composed as a stacked bidirectional Zener diode of one or a plurality of N+ polycrystalline silicon regions of a first layer and a P+ polycrystalline silicon region of a second layer, and a stacked resistor of one or a plurality of N+ resistor layers of the first layer and an N+ resistor layer of the second layer, respectively. One end of the plurality of N+ polycrystalline silicon regions of the first layer is connected to an external gate electrode terminal, and the other end is connected to a source electrode. One end of the plurality of N+ resistor layers of the first layer is connected to a gate electrode, and the other end is connected to the external gate electrode terminal. Semiconductor regions of the first layer and the second layer are formed by using semiconductor films, which form a hetero semiconductor region and the gate electrode, respectively.

Owner:NISSAN MOTOR CO LTD

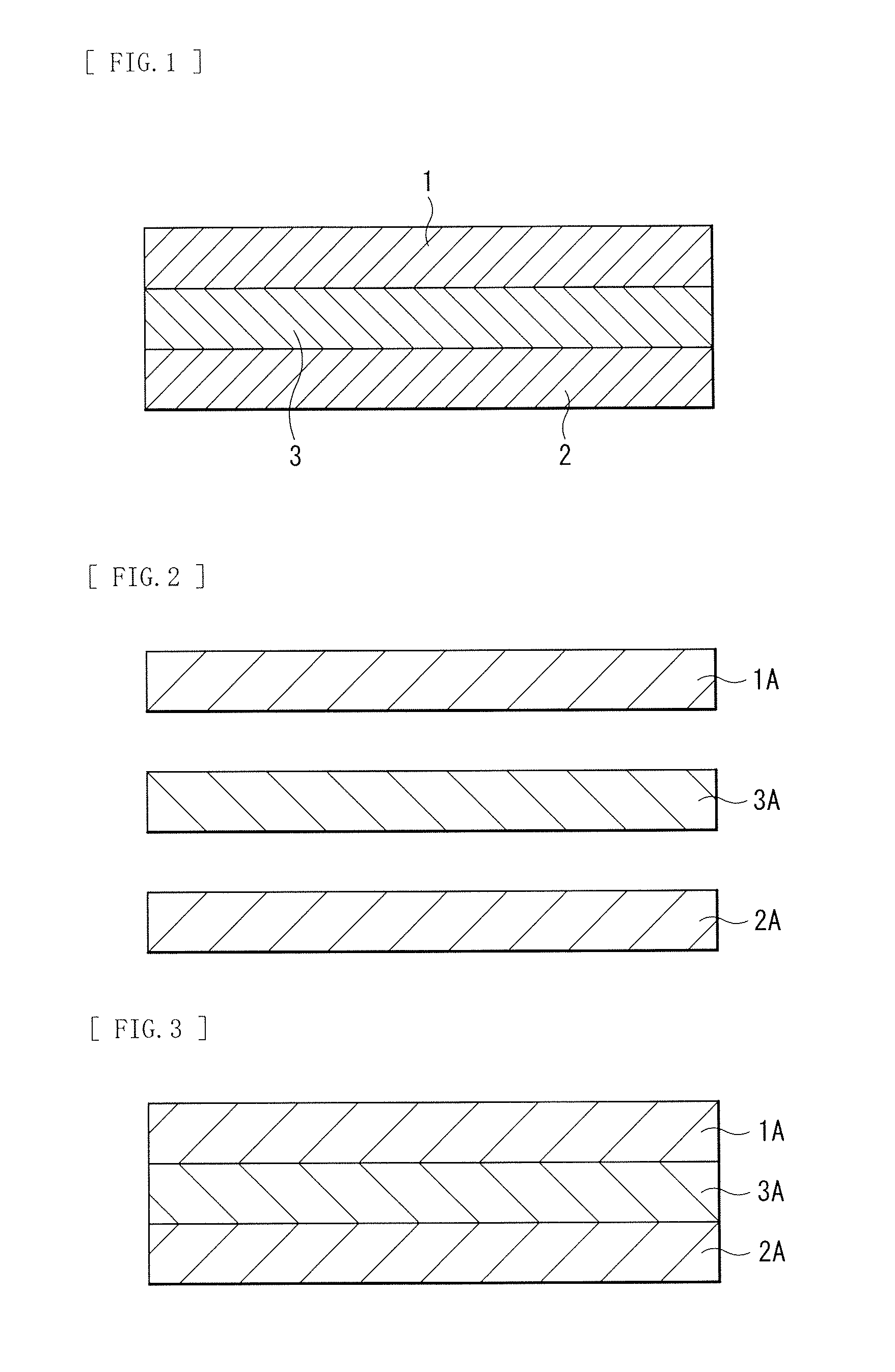

Battery and method of manufacturing the same

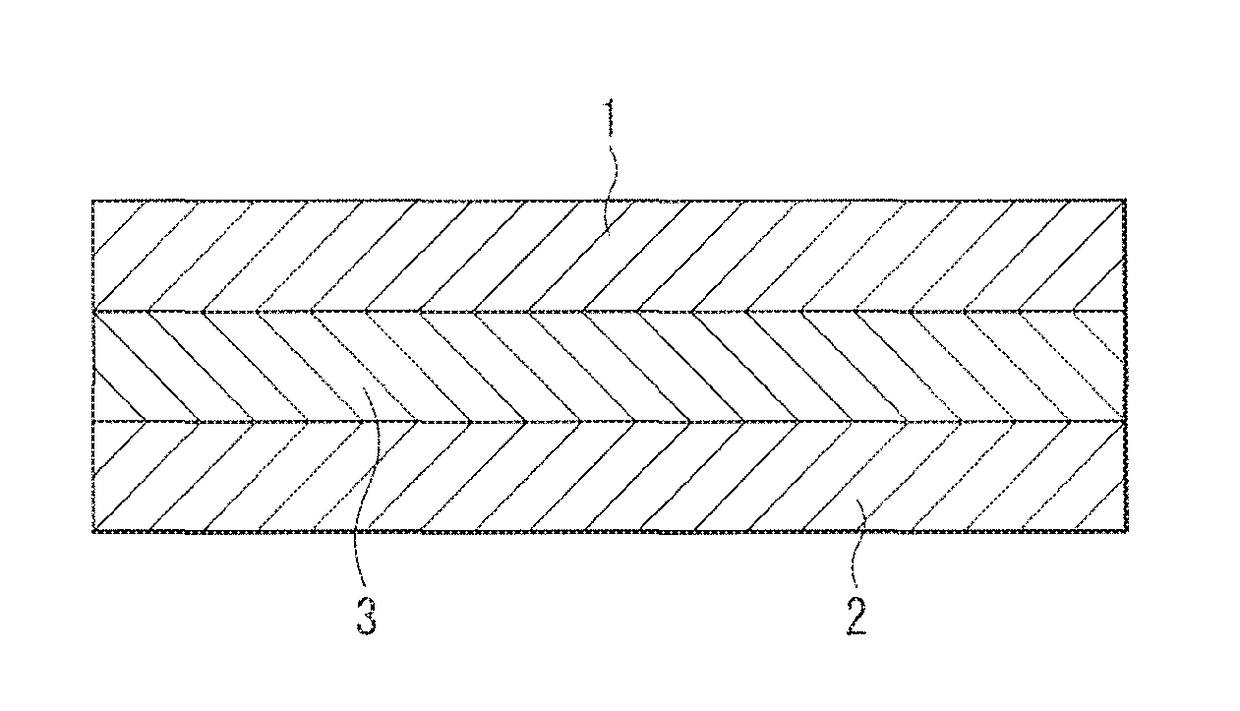

ActiveUS20140220454A1Ionic conduction can be improvedHigh ion conductivitySolid electrolytesFinal product manufactureElectrolyteAnode

A battery capable of improving ionic conduction is provided. The battery includes a cathode, an anode, and a solid electrolyte layer. One or more of the cathode, the anode, and the solid electrolyte layer includes a solid electrolyte binder.

Owner:MURATA MFG CO LTD

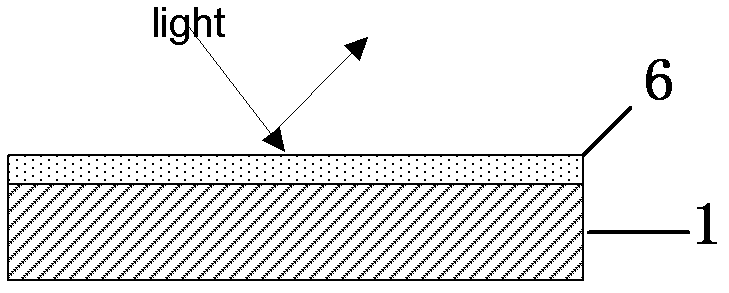

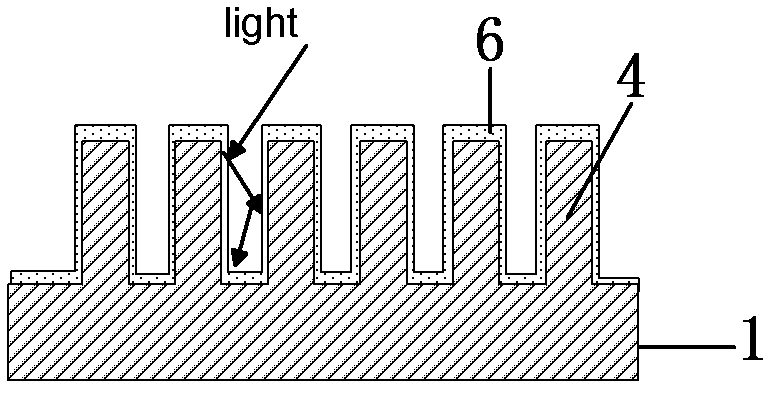

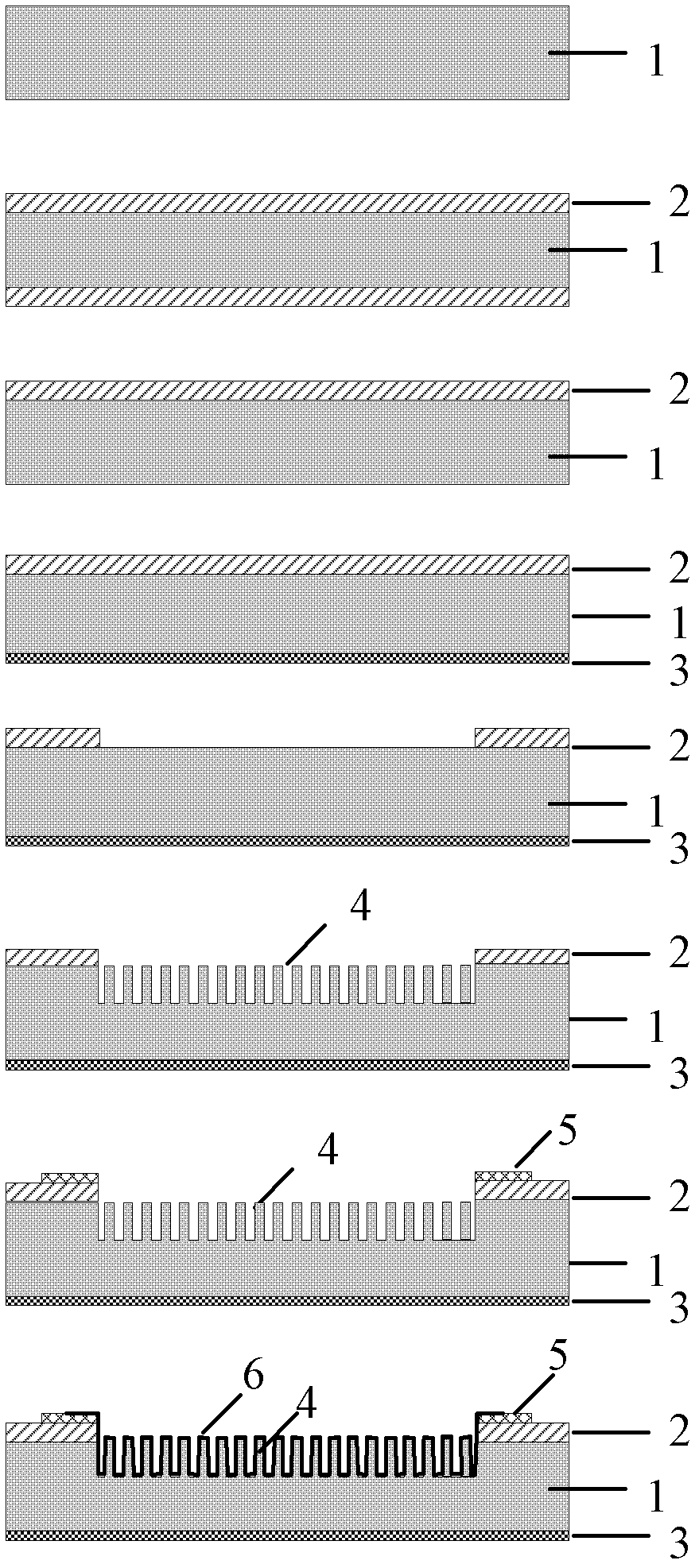

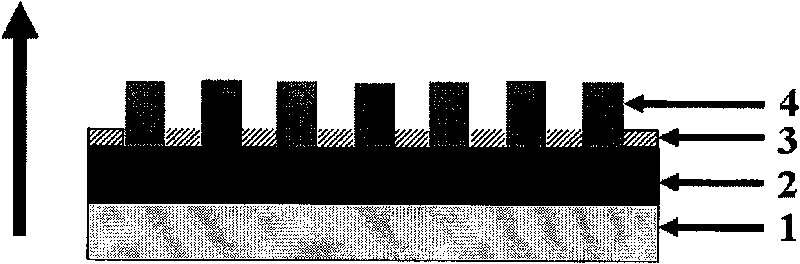

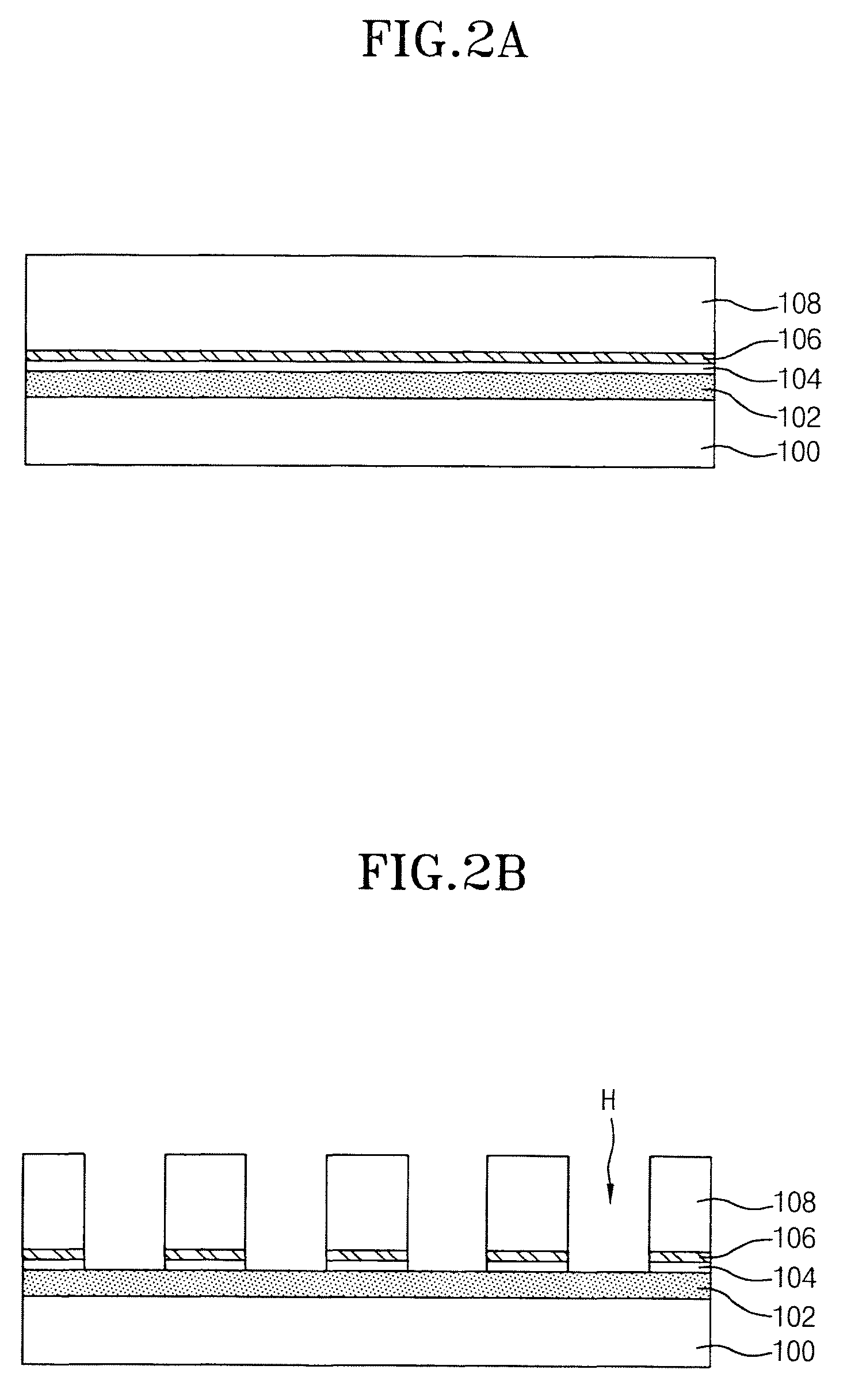

Graphene/silicon pillar array Schottky junction photovoltaic cell and manufacturing method thereof

InactiveCN102254963AReduced reflectance of incident lightIncrease contact areaPhotovoltaic energy generationSemiconductor devicesEvaporationSilicon oxide

The invention discloses a graphene / silicon pillar array Schottky junction photovoltaic cell and a manufacturing method thereof. The method comprises the following steps of: performing thermal oxidation on a monocrystalline semiconductor substrate to form silicon oxide (SiO2) which is used as an isolating layer, eroding the SiO2 isolating layer to form an opening and preparing a silicon pillar array in the opening by photoetching and dry-etching methods, performing evaporation coating on the back of the substrate to form a metal back electrode, preparing a metal front electrode on the isolating layer, and finally transferring or spin-coating graphene onto the silicon pillar array and connecting with the front electrode. The solar cell has a simple structure and is easy to manufacture. Not only can the reflection of incident light be effectively reduced but also the contact area of Schottky junction is increased, as a result, the purpose of increasing conversion efficiency of the solar cell is achieved.

Owner:TSINGHUA UNIV

NAND flash memory cell row and manufacturing method thereof

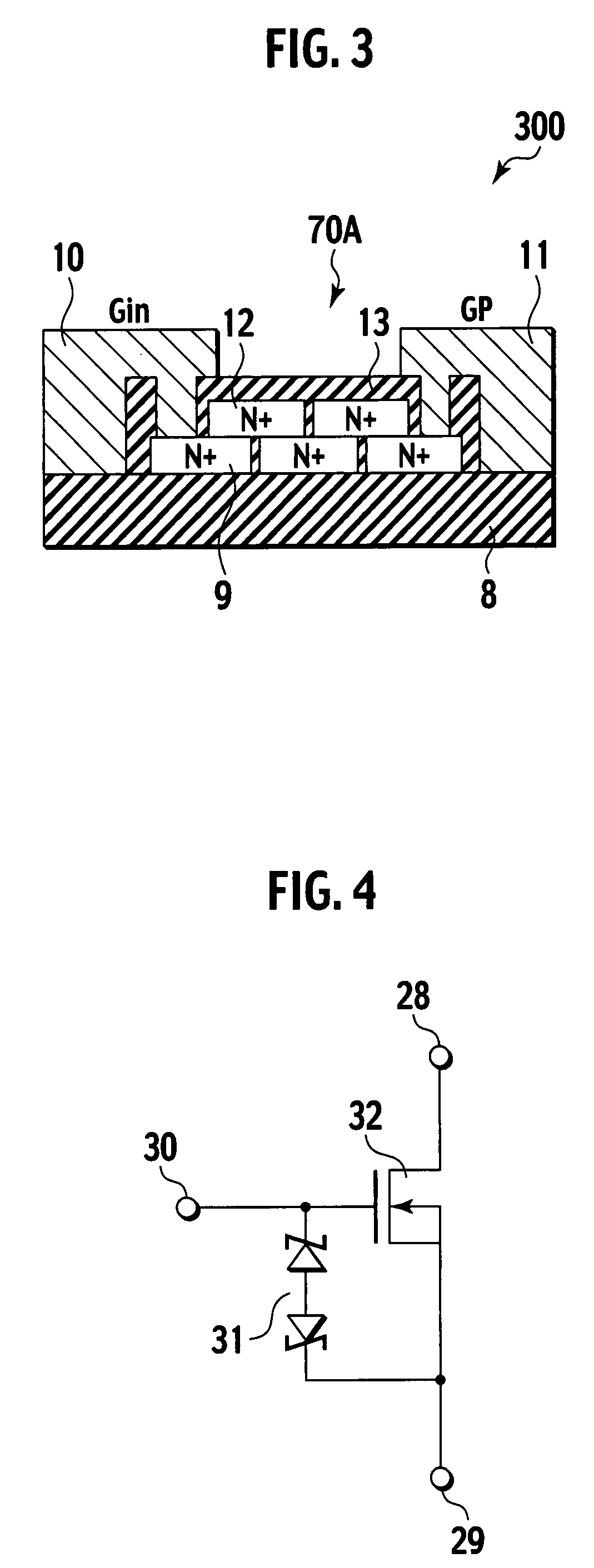

ActiveUS20060040440A1Improve memory performanceIncrease erasing speedSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

A NAND flash memory cell row includes first and second stacked gate structures, control and floating gates, inter-gate dielectric layer, a tunnel oxide layer, doping regions and source / drain regions. The first stacked gate structures has an erase gate dielectric layer, an erase gate and a first cap layer. Each of the second stacked gate structure has a select gate dielectric layer, a select gate and a second cap layer. The control gate is between each of the first stacked gate structures, and between each of the second stacked gate structures and the adjacent first stacked gate structure. The floating gate is between the control gate and substrate. The inter-gate dielectric layer is disposed between the control and floating gates. The tunnel oxide is between the floating gate and substrate. The doping regions are disposed under the first stacked gate structure, and the source / drain regions are in the exposed substrate.

Owner:POWERCHIP SEMICON MFG CORP

Copper-indium-selenium nanowire array and preparation method and application thereof

InactiveCN101700871AWith photoelectric conversion performanceImprove collection efficiencyNanostructure manufactureFinal product manufactureHeterojunctionIndium

The invention discloses a copper-indium-selenium nanowire array and a preparation method thereof. The method comprises the following steps: preparing a metal electrode layer on a glass or silicon slice substrate, using an ordered nano-template as growing mask to prepare the ordered nanowire structure copper-indium-selenium P-type absorbing layer material array on the metal electrode layer of the substrate through electrodeposition, and partly removing the template from top to bottom through chemical corrosion or physical etching method to expose the nanowire array. The array of the invention can be used to prepare the heterojunction solar cell with photoelectric translating performance.

Owner:UNIV OF SCI & TECH OF CHINA

Groove notching and grid burying method for crystalline silicon solar cell

InactiveCN102082199AReduce fragmentation rateEasy alignmentFinal product manufactureSemiconductor devicesPhysicsSilicon chip

The invention relates to a groove notching and grid burying method for a crystalline silicon solar cell. The method comprises the following steps of: depositing a mask layer on the surface of a silicon slice, and etching the mask layer at the corresponding electrode position; then notching a groove by a chemical corrosion method to form an electrode groove with a narrow upper part and a wide lower part; and performing screen printing on the electrode groove. The efficiency of the prepared solar cell is improved obviously. The preparation process is simple, resources are saved, and production cost is greatly reduced; damage to a silicon slice and the defect of the silicon slice are avoided by notching the groove by the method, the fragment percent is low, the grooves can be notched on a large scale and the method is suitable for industrial production.

Owner:山东力诺太阳能电力股份有限公司

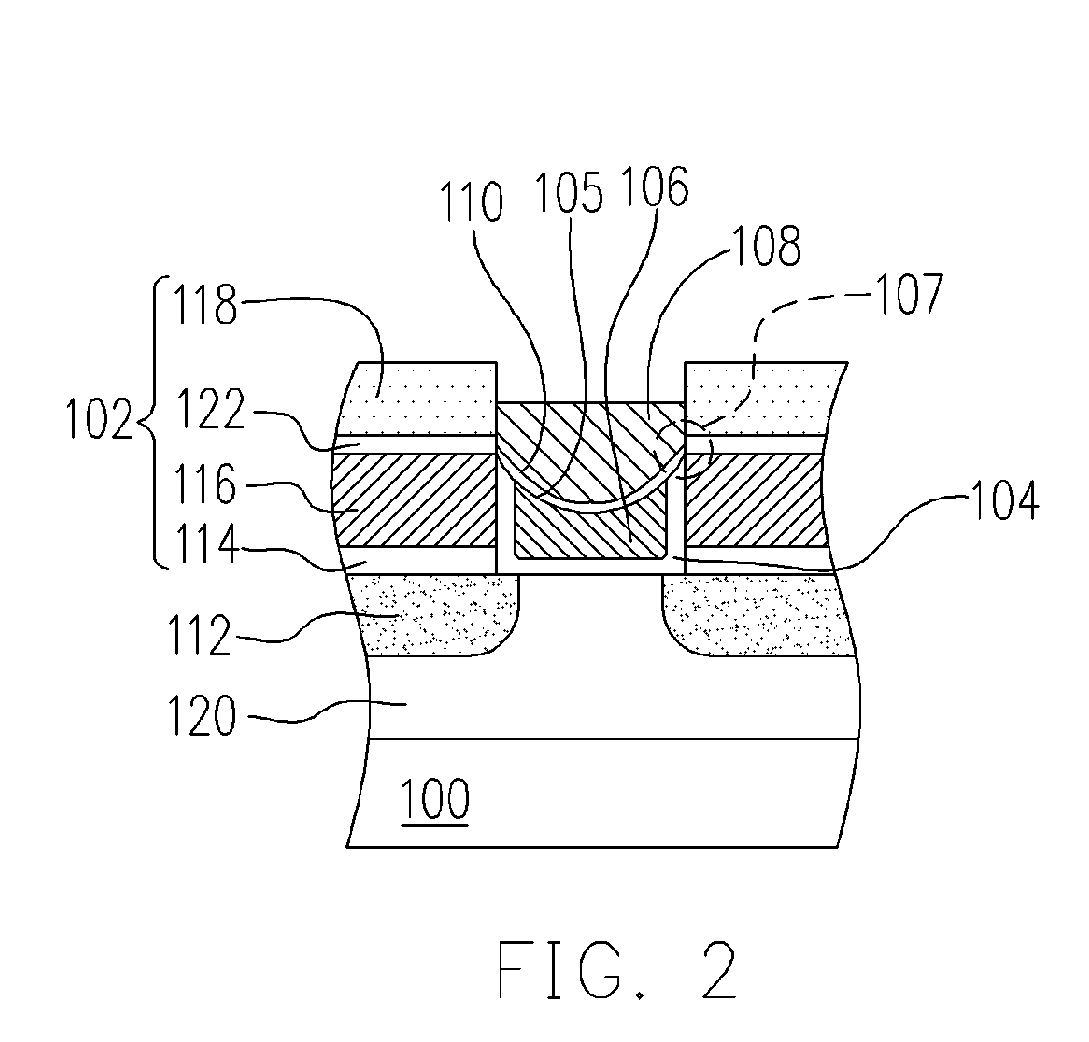

Semiconductor device having a junction extended by a selective epitaxial growth (SEG) layer and method of fabricating the same

ActiveUS7592686B2Improve leakage currentIncrease junction areaTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

In a semiconductor device, and a method of fabricating the same, the semiconductor device includes a protrusion extending from a substrate and a selective epitaxial growth (SEG) layer surrounding an upper portion of the protrusion, the SEG layer exposing sidewalls of a channel region of the protrusion.

Owner:SAMSUNG ELECTRONICS CO LTD

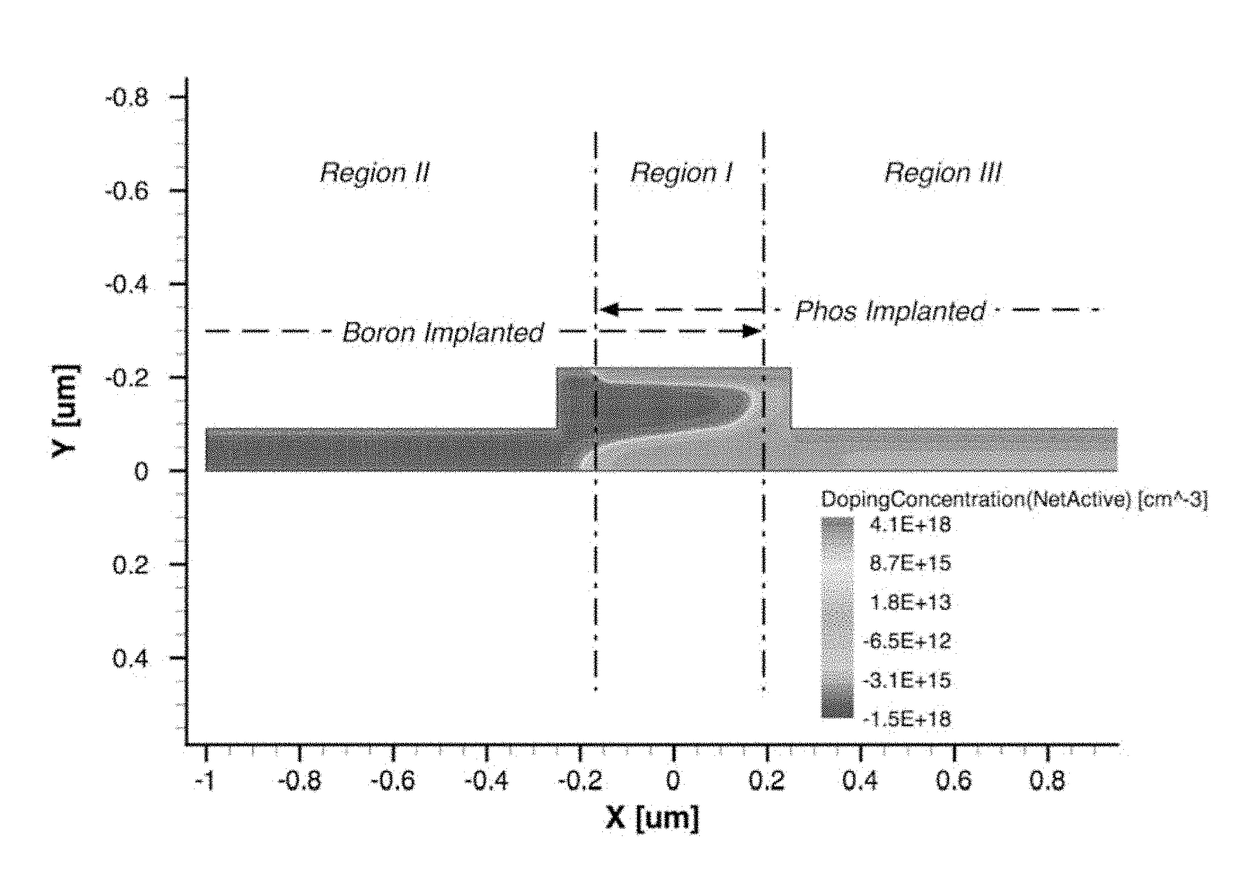

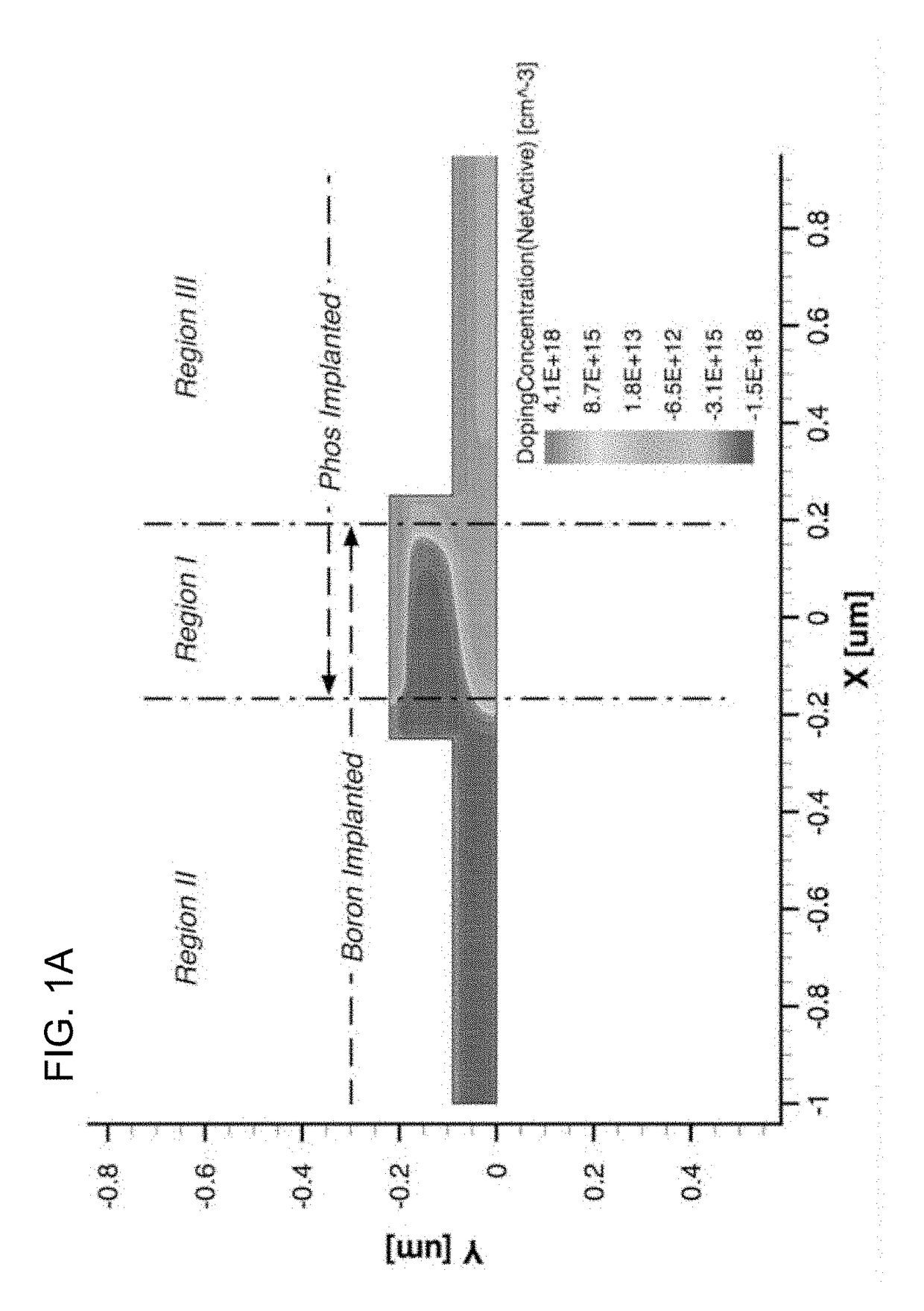

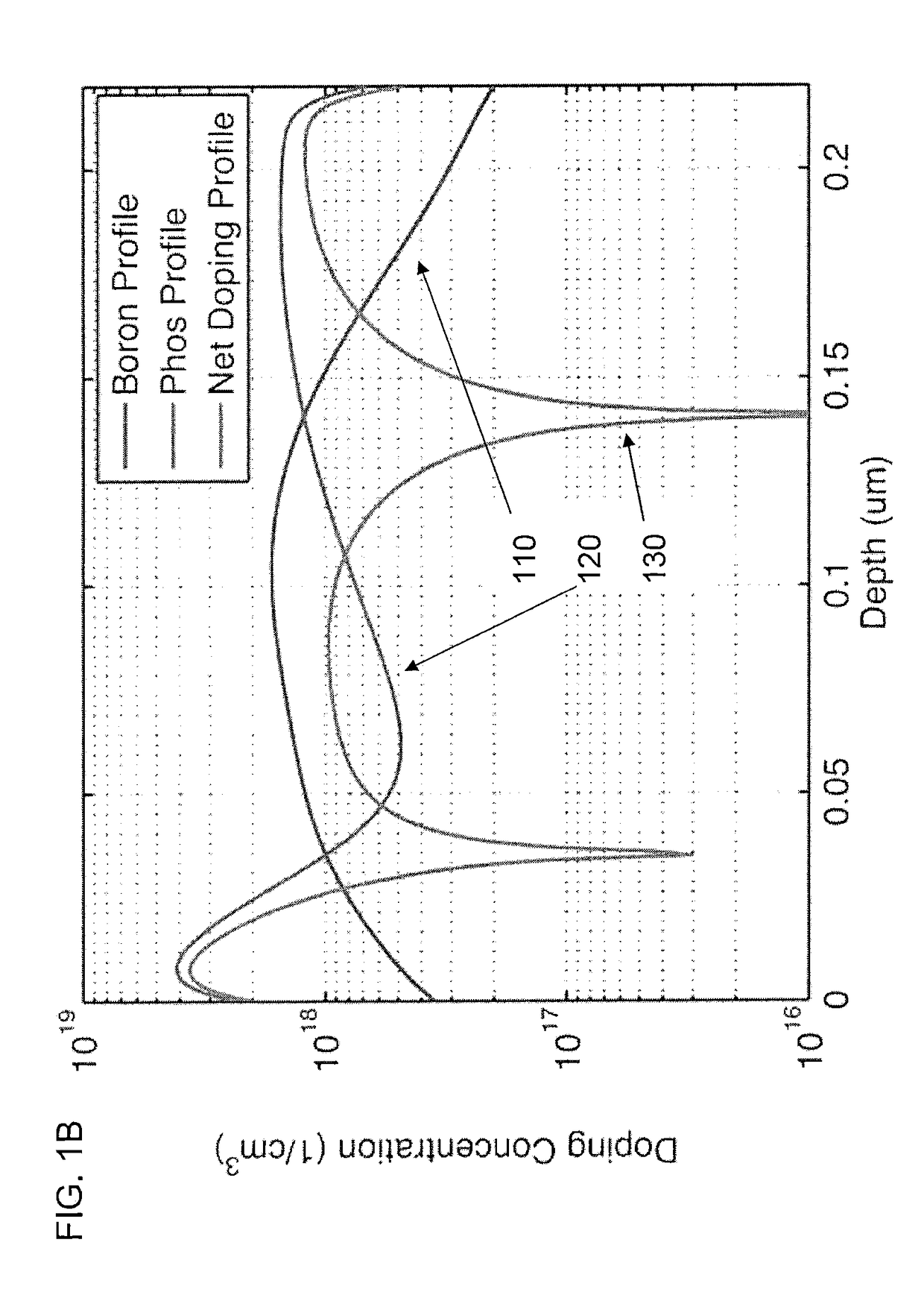

Optical modulator

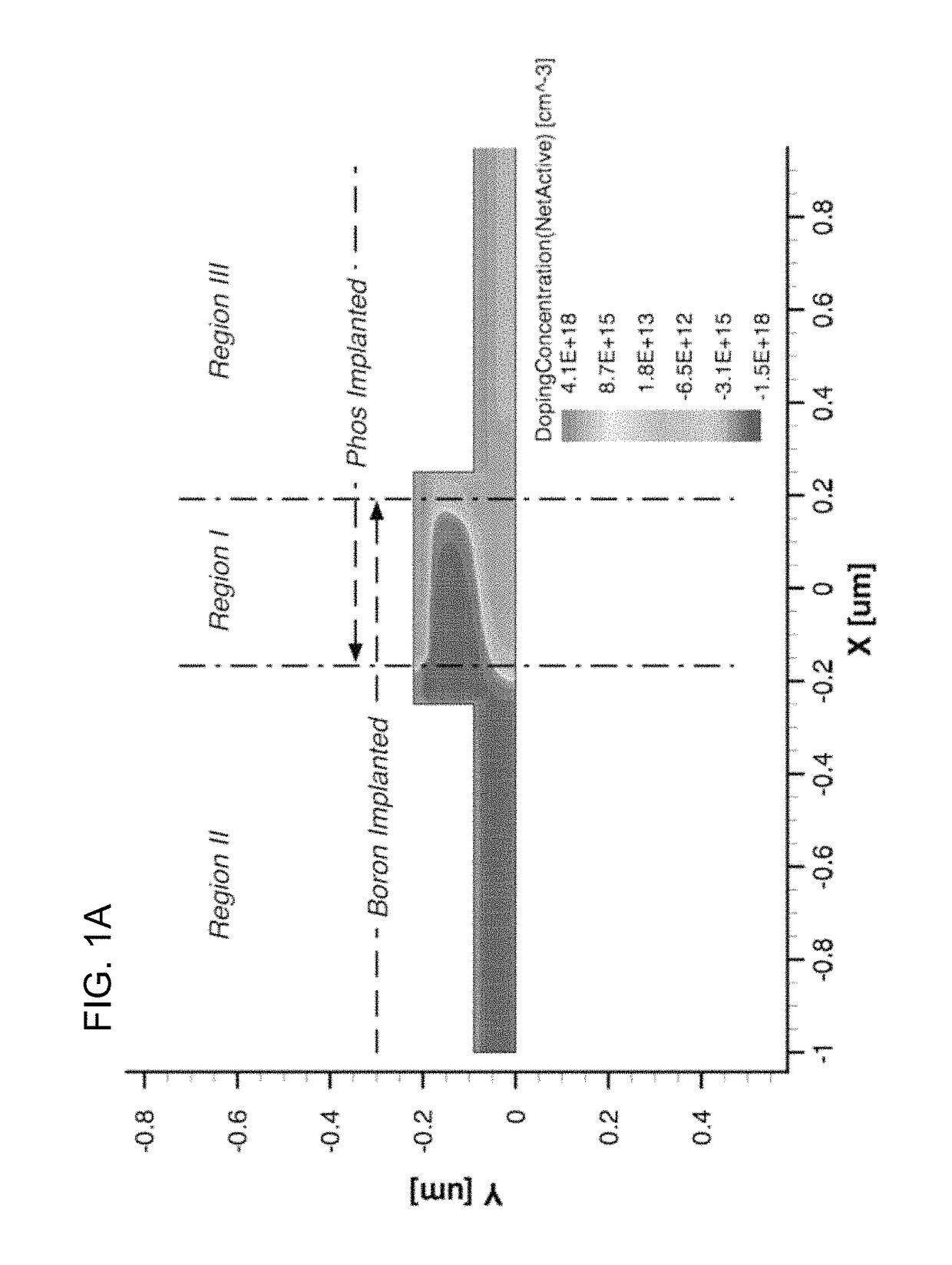

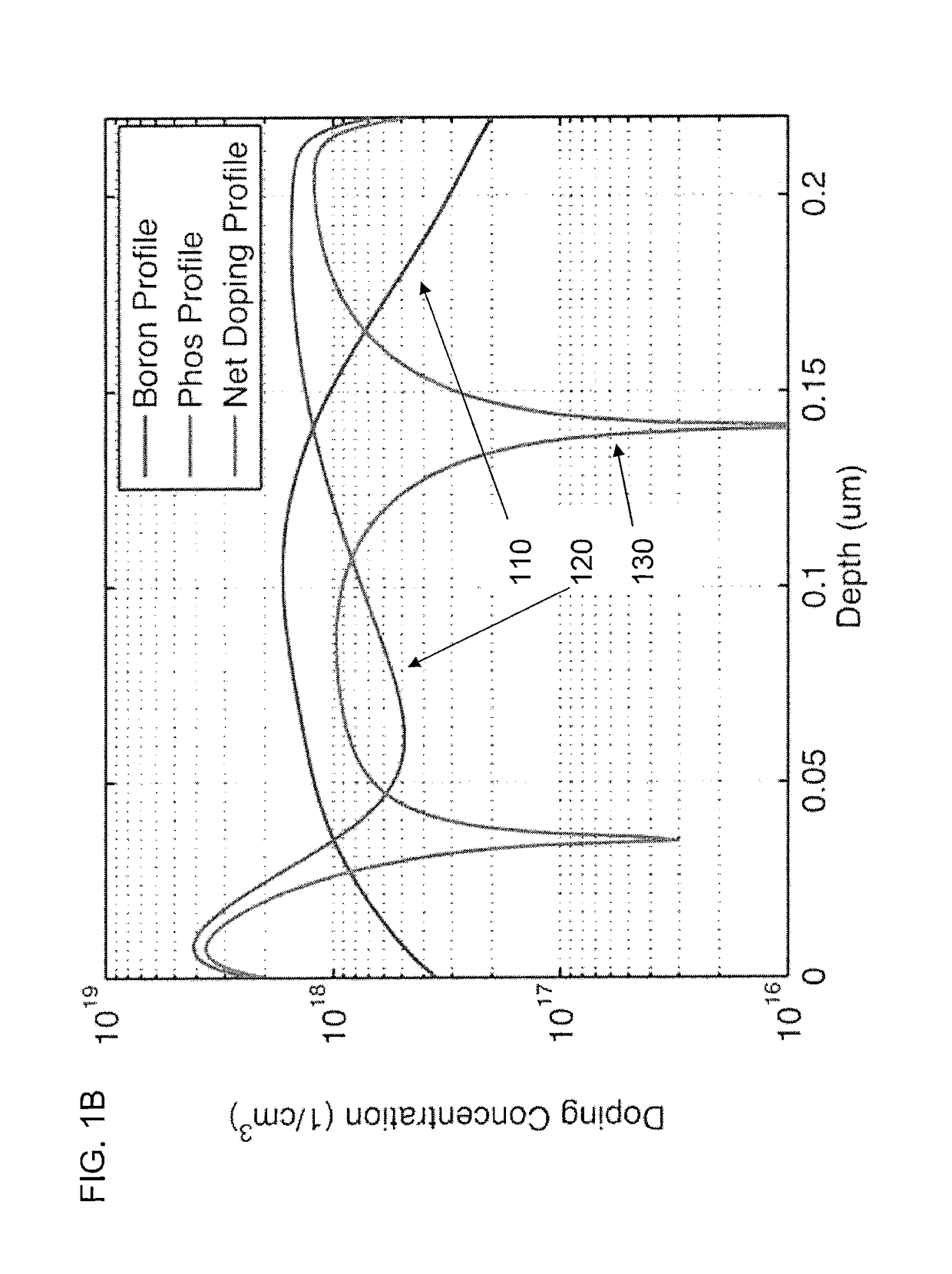

ActiveUS20180210242A1Increase overlapIncrease junction areaNon-linear opticsCapacitanceCharge carrier

A novel phase shifter design for carrier depletion based silicon modulators, based on an experimentally validated model, is described. It is believed that the heretofore neglected effect of incomplete ionization will have a significant impact on ultra-responsive phase shifters. A low VπL product of 0.3 V·cm associated with a low propagation loss of 20 dB / cm is expected to be observed. The phase shifter is based on overlapping implantation steps, where the doses and energies are carefully chosen to utilize counter-doping to produce an S-shaped junction. This junction has a particularly attractive VπL figure of merit, while simultaneously achieving attractively low capacitance and optical loss. This improvement will enable significantly smaller Mach-Zehnder modulators to be constructed that nonetheless would have low drive voltages, with substantial decreases in insertion loss. The described fabrication process is of minimal complexity; in particular, no high-resolution lithographic step is required.

Owner:NOKIA SOLUTIONS & NETWORKS OY

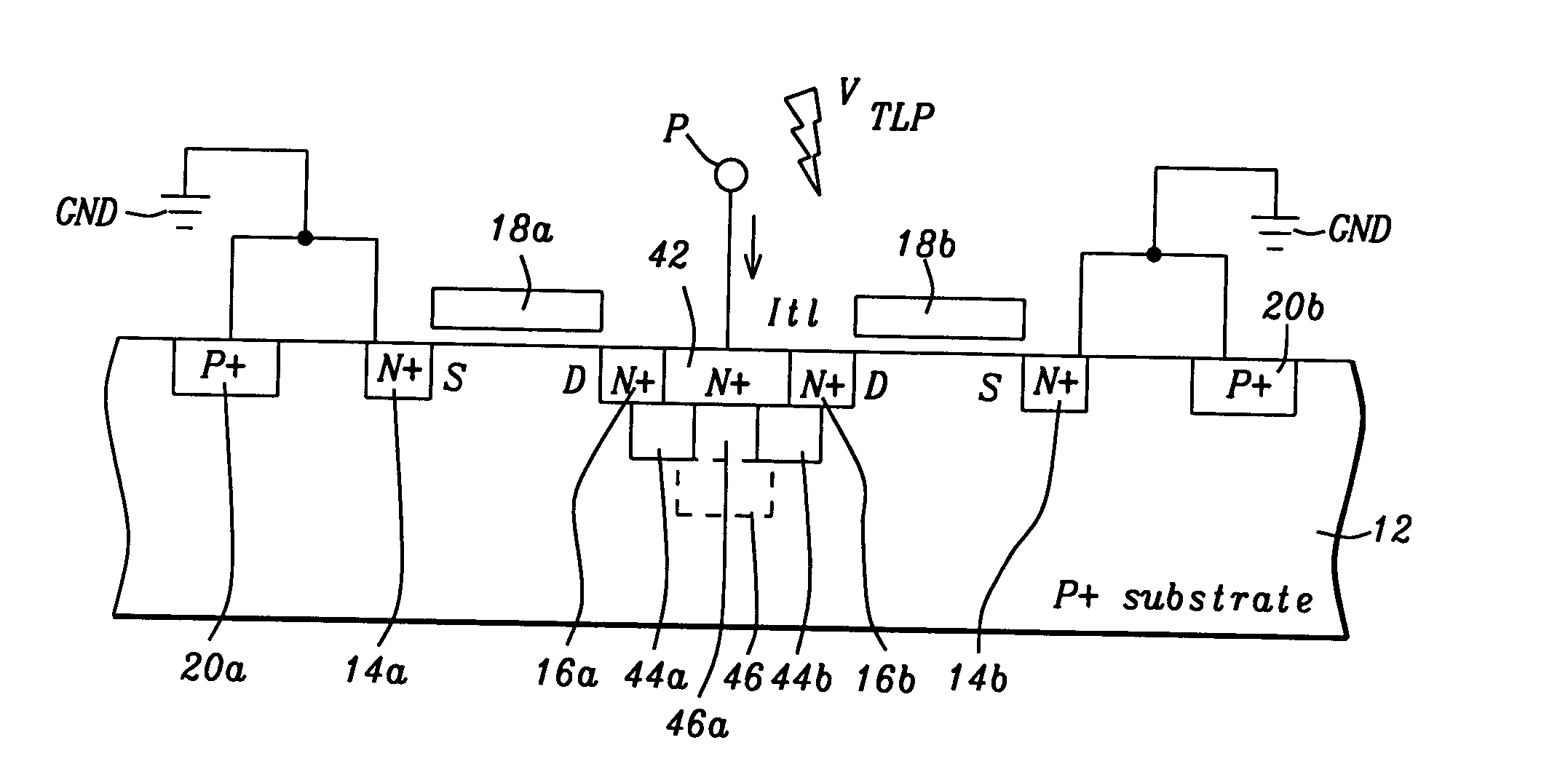

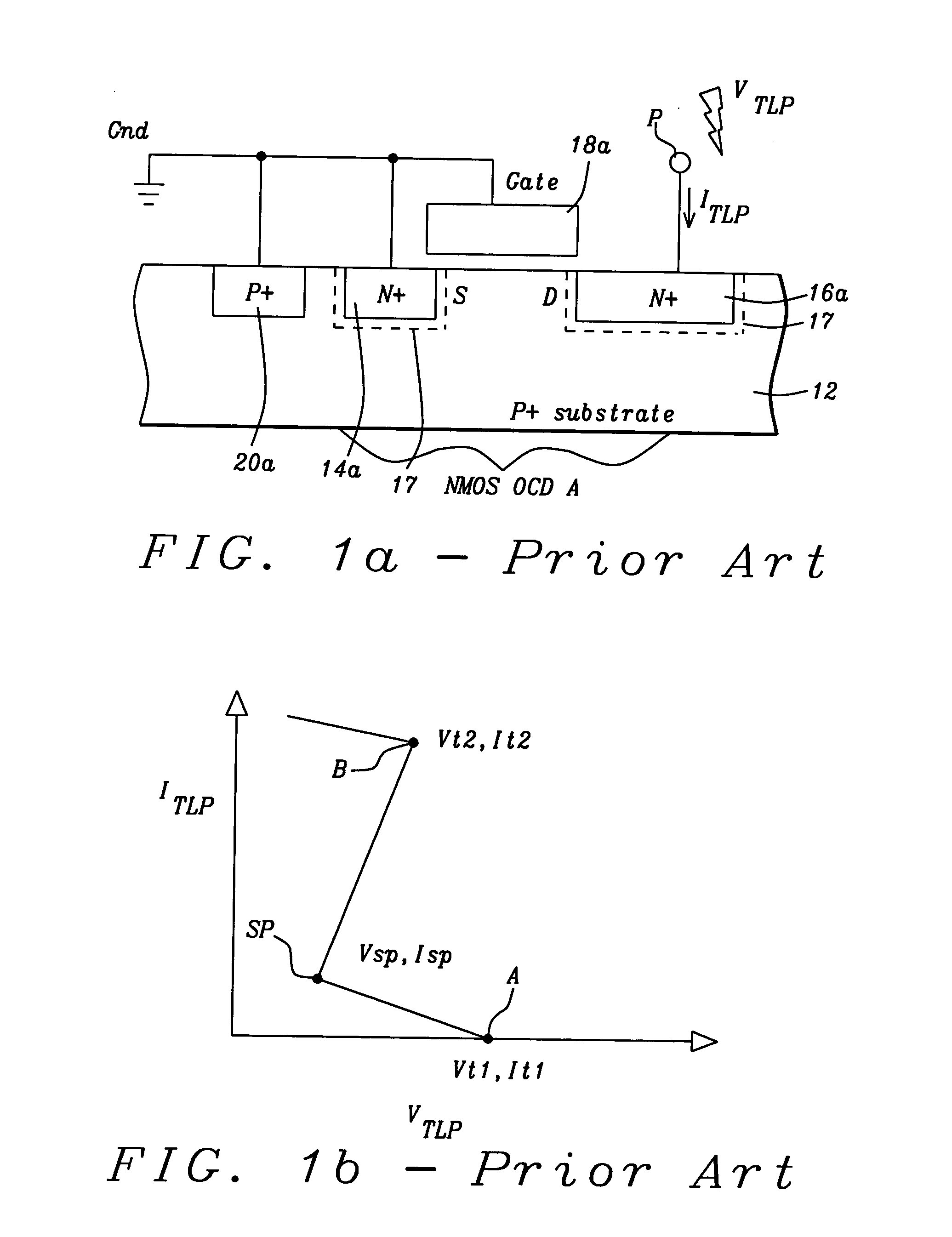

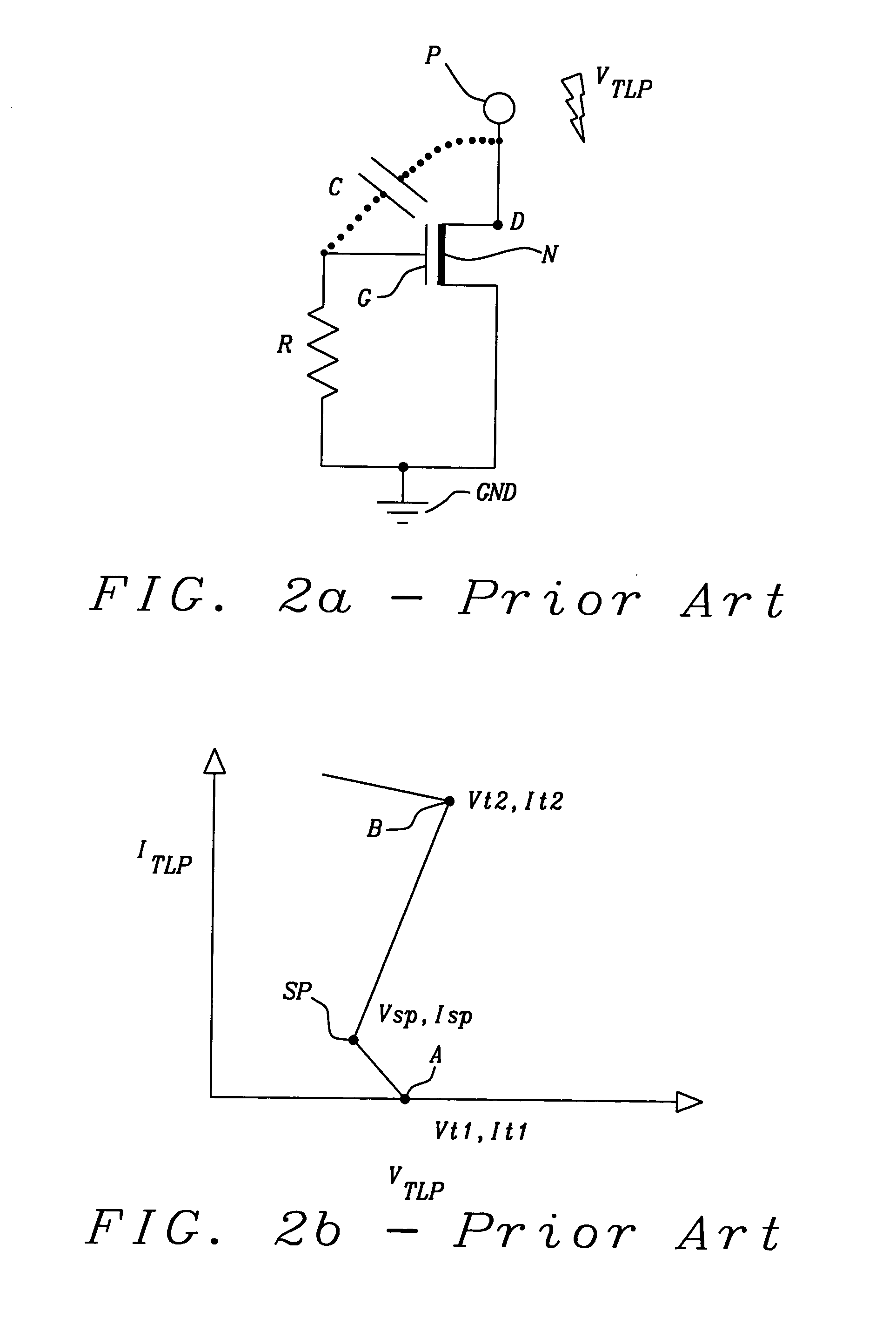

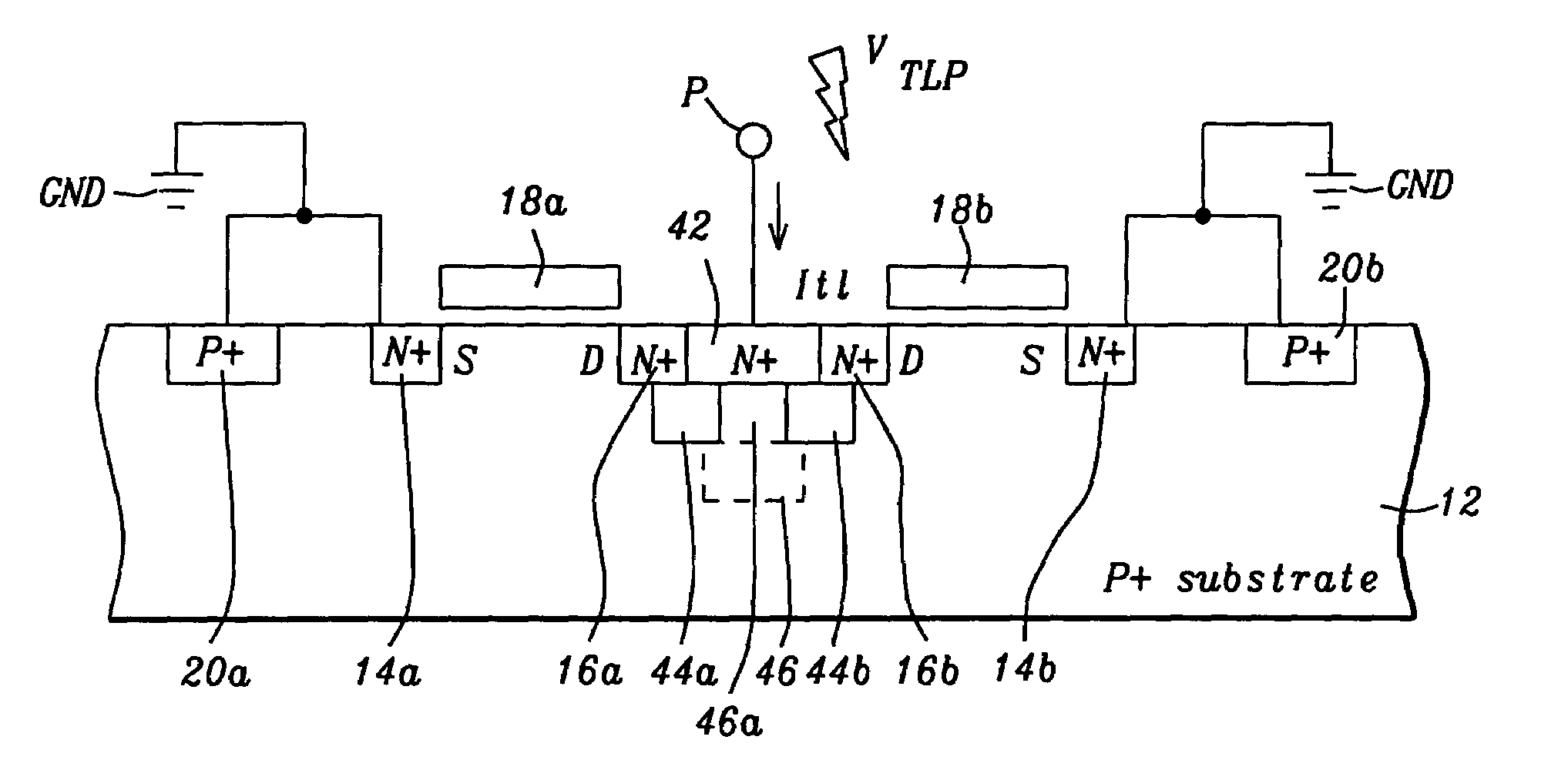

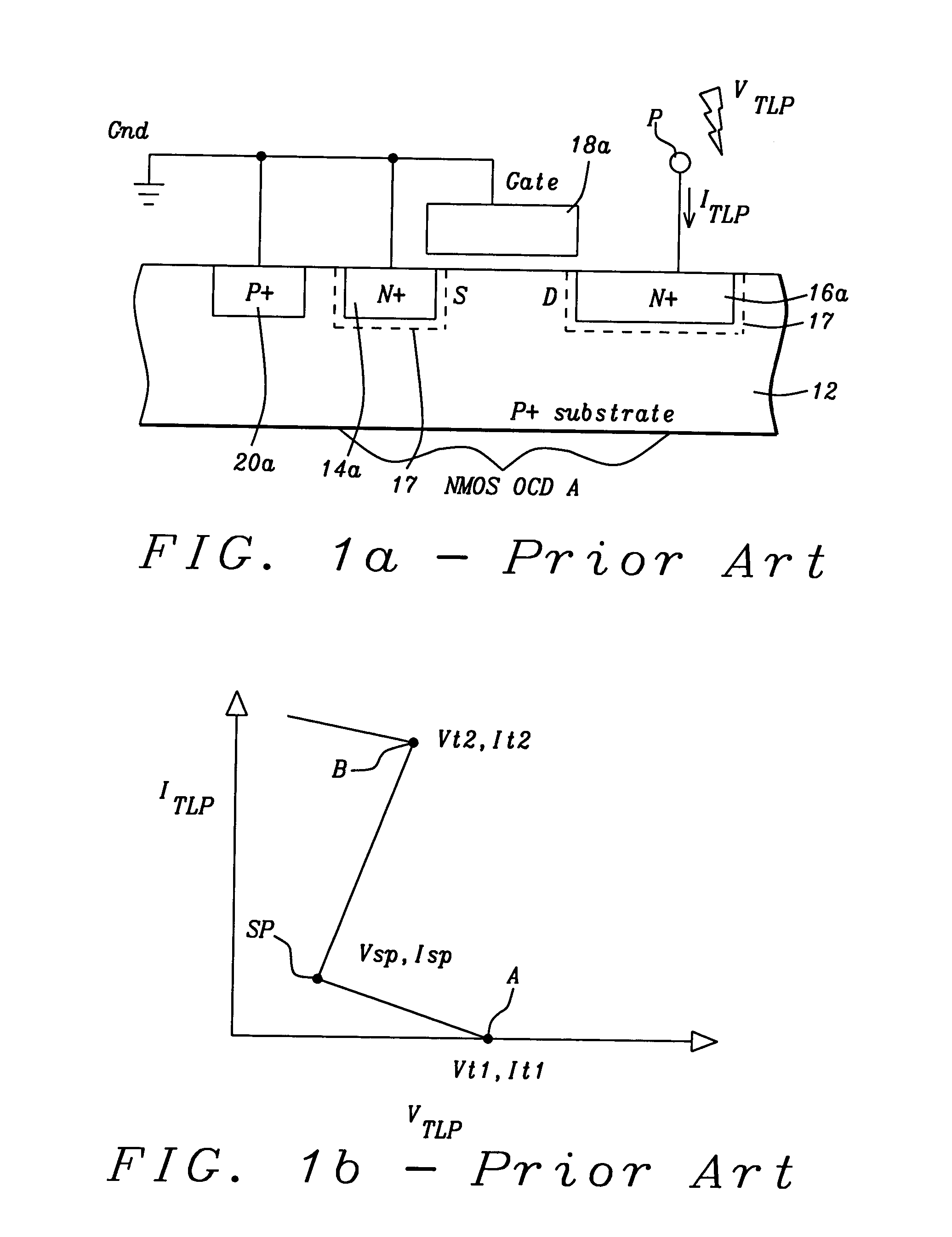

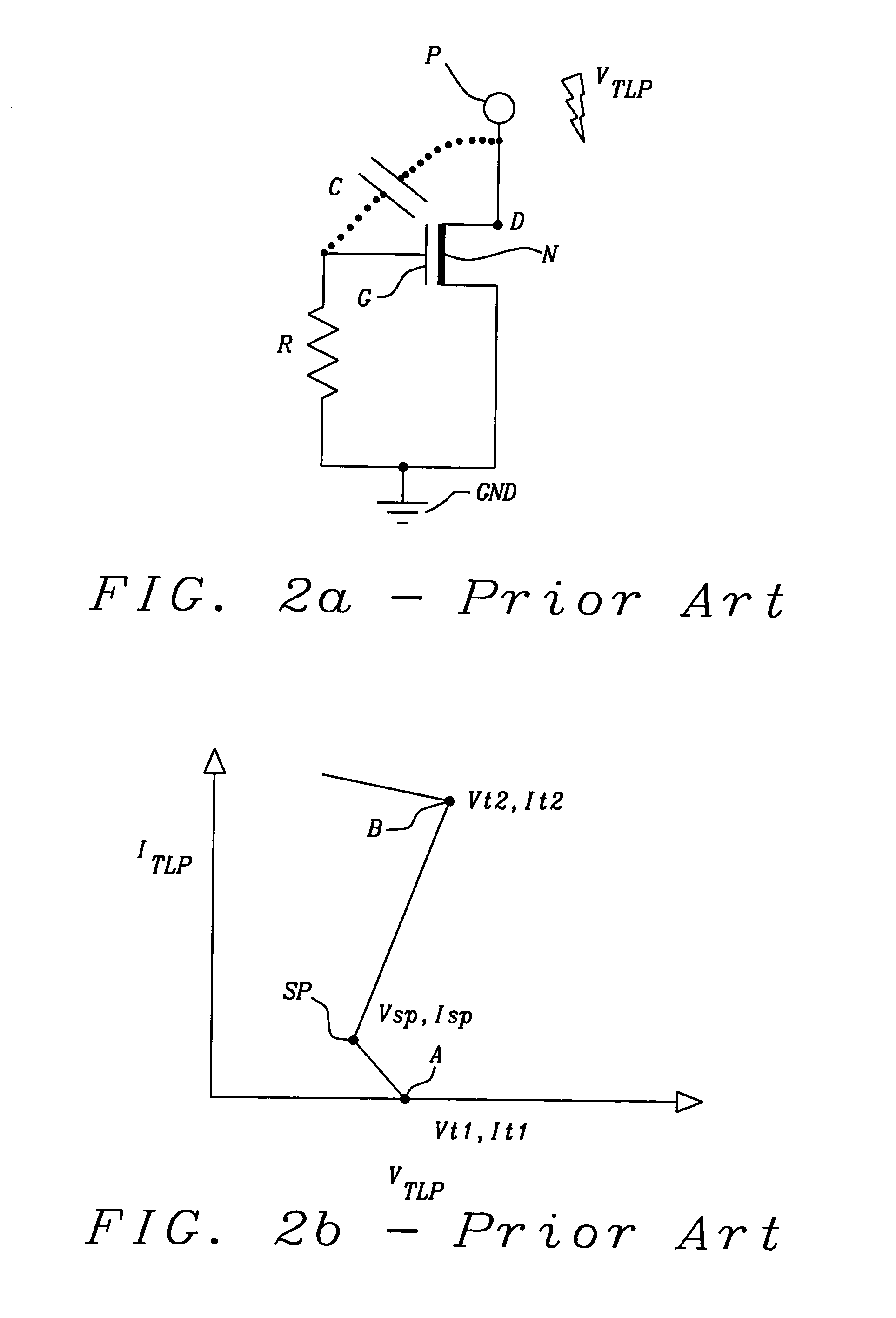

Electrostatic discharge protection device with complementary dual drain implant

ActiveUS20050056896A1Improve protectionReduce voltageTransistorSemiconductor/solid-state device detailsElectrical connectionParasitic bipolar transistor

Off-chip driver (OCD) NMOS transistors with ESD protection are formed by interposing an P-ESD implant between the N+ drain regions of OCD NMOS transistors and the N-well such that the P-ESD surrounds a section of the N-well. The P-ESD implant is dosed less than the N+ source / drain implants but higher than the N-well dose. In another embodiment, N-well doping is used along with P-ESD doping, where the P-ESD doping is chosen such that it counterdopes the N-well underneath the N+ drains. The N-well, however, still maintains electrical connection to the N+ drains. This procedure creates a larger surface under the area where the junction breakdown occurs and an increased radius of curvature of the junction. The P-ESD implant is covered by N-type on three sides creating better parasitic bipolar transistor characteristics.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING +1

Heterojunction and photoelectrochemistry mixed solar cell

InactiveCN101694816ALower internal resistanceIncrease junction areaLight-sensitive devicesPhotovoltaic energy generationHeterojunctionElectrolysis

The invention discloses a heterojunction and photoelectrochemistry mixed solar cell structure which belongs to the technical field of the applications of solar cells and nano materials. The solar cell structure is characterized in that a transparent electrode layer, a semiconductor nano linear array and an electrolytic solution layer are in pairwise contact; the transparent electrode layer and the semiconductor nano linear array form a heterojunction solar cell; and the transparent electrode layer, the semiconductor nano linear array and the electrolytic solution layer together form a photoelectrochemistry solar cell. The solar energy converting device with the novel structure is formed by mixing the heterojunction solar cell and the photoelectrochemistry solar cell, simultaneously has the characteristics of the two cells and has high photoelectric conversion efficiency.

Owner:TSINGHUA UNIV

Electrostatic discharge protection device with complementary dual drain implant

ActiveUS6998685B2Improve protectionLower breakdown voltageTransistorSemiconductor/solid-state device detailsElectrical connectionParasitic bipolar transistor

Off-chip driver (OCD) NMOS transistors with ESD protection are formed by interposing an P-ESD implant between the N+ drain regions of OCD NMOS transistors and the N-well such that the P-ESD surrounds a section of the N-well. The P-ESD implant is dosed less than the N+ source / drain implants but higher than the N-well dose. In another embodiment, N-well doping is used along with P-ESD doping, where the P-ESD doping is chosen such that it counterdopes the N-well underneath the N+ drains. The N-well, however, still maintains electrical connection to the N+ drains. This procedure creates a larger surface under the area where the junction breakdown occurs and an increased radius of curvature of the junction. The P-ESD implant is covered by N-type on three sides creating better parasitic bipolar transistor characteristics.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING +1

Cuprous oxide-based PIN-junction solar battery of nano structure and preparation method thereof

ActiveCN102569480AIncrease junction areaImprove photoelectric conversion efficiencyPolycrystalline material growthFinal product manufactureNano structuringInsulation layer

The invention relates to a cuprous oxide-based PIN-junction solar battery of a nano structure and a preparation method thereof. The solar battery comprises a substrate, a P-type cuprous-oxide nano-wire array, an insulation layer, an N-type layer, an N-type ohm electrode and a P-type ohm electrode, wherein the P-type cuprous-oxide nano-wire array is grown on the substrate; the insulation layer is deposited on the surface of the P-type cuprous-oxide nano-wire array; the N-type layer is filled outside the insulation layer to form a film layer; the N-type ohm electrode is arranged on the N-type layer; and the P-type ohm electrode is arranged on the P-type cuprous-oxide nano-wire array layer. Due to the adoption of the nano-wire array structure, the junction area of the battery can be improved, the dispersion distance of a carrier can be reduced, the width of a use-up layer can be effectively increased through the PIN structure, and the separation and collection efficiency of the carrier can be greatly improved, so the energy conversion efficiency of the solar battery can be improved. Adopted raw materials are abundant, inexpensive and pollution-free. An electrochemical deposition method, a magnetron sputtering method and an electron beam evaporation method are adopted by the preparation method and can be widely applied to the industrial production, and a promising development prospect can be realized.

Owner:ZHEJIANG UNIV

Transient voltage suppressor and its manufacturing method

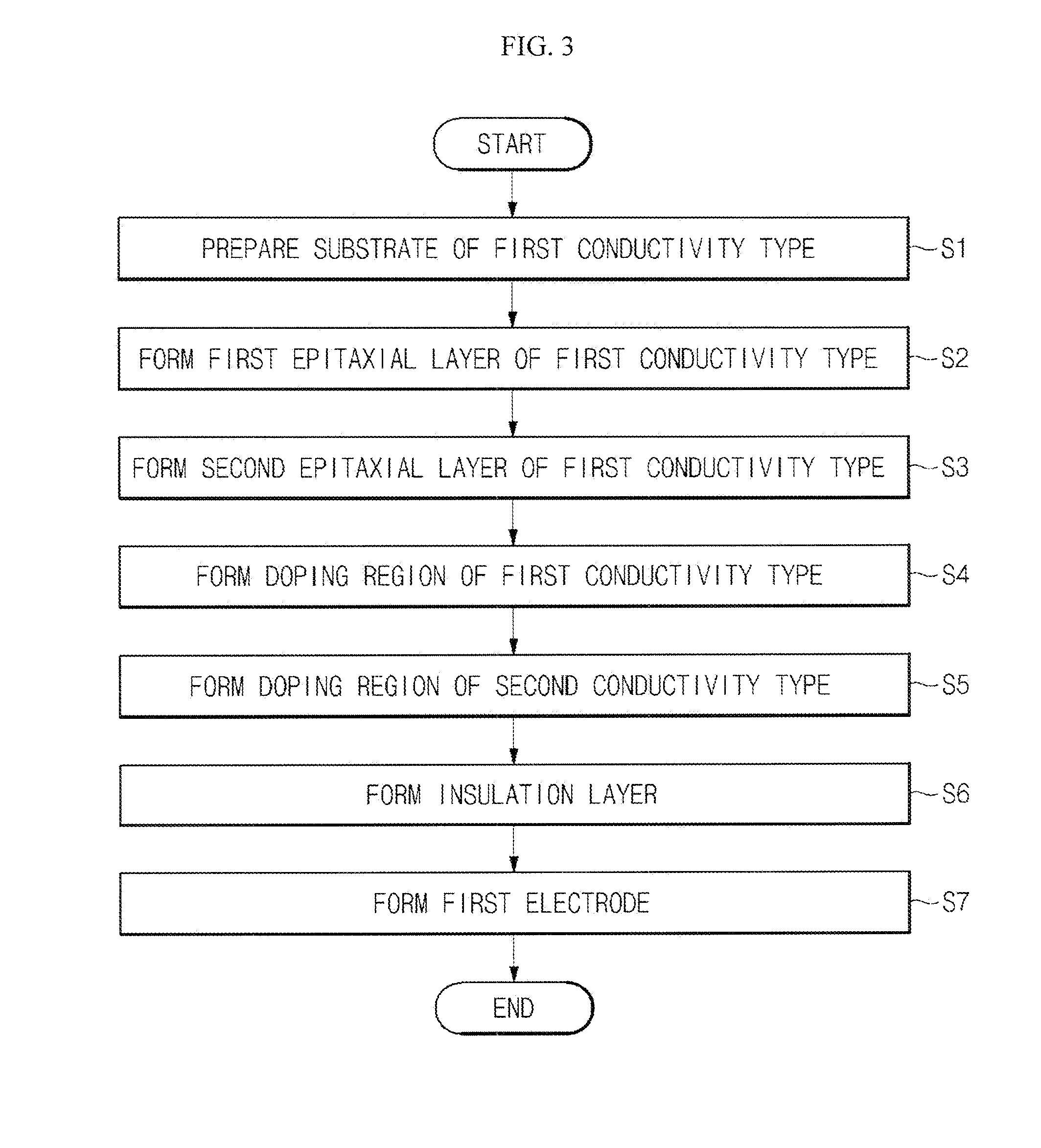

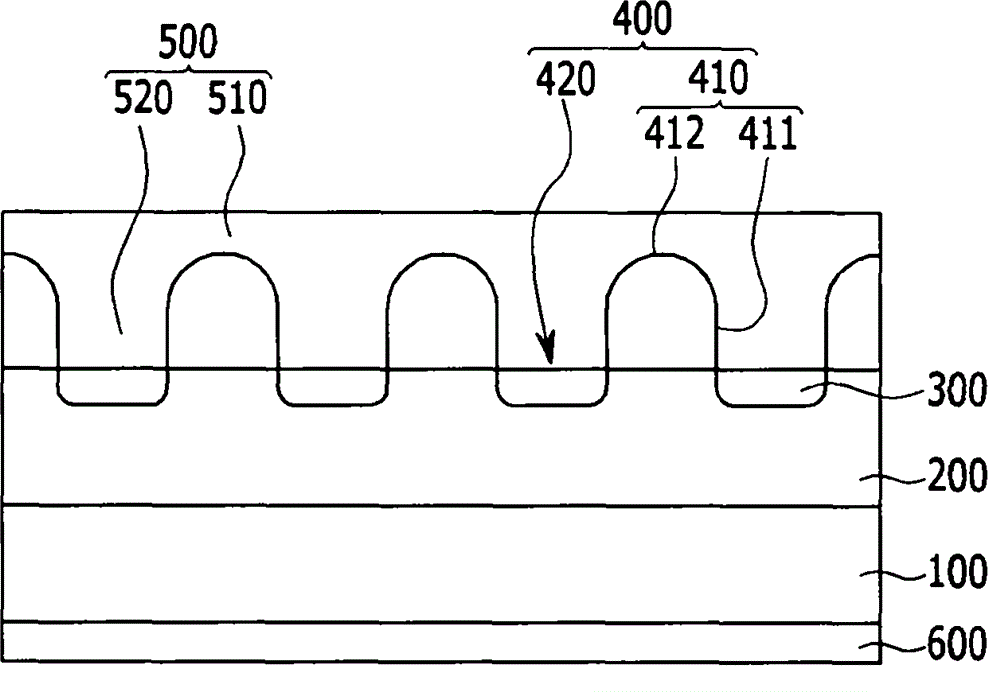

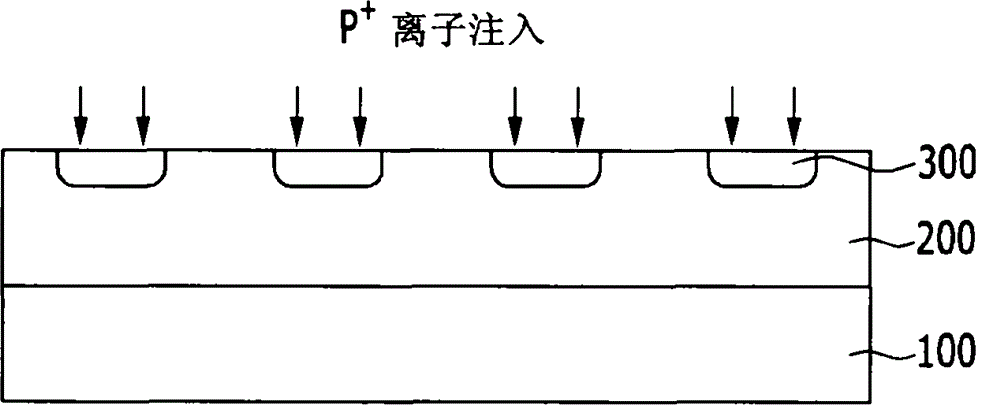

ActiveUS20150115390A1Control voltage withstanding characteristicIncrease junction areaSolid-state devicesSemiconductor/solid-state device manufacturingCurrent distributionZener diode

A transient voltage suppressor and its manufacturing method are provided, which can easily control voltage withstanding characteristics of a Zener diode by analogizing growth of a buried layer by forming a portion of the buried layer by performing ion implantation on a first epitaxial layer and then forming the other portion of the buried layer while depositing a second epitaxial layer having the same impurity concentration with the first epitaxial layer, and which can improve a current distribution characteristic by forming a doping region in a ring shape to increase a current pass region by increasing a PN junction area of a Zener diode in a small area.

Owner:KEC

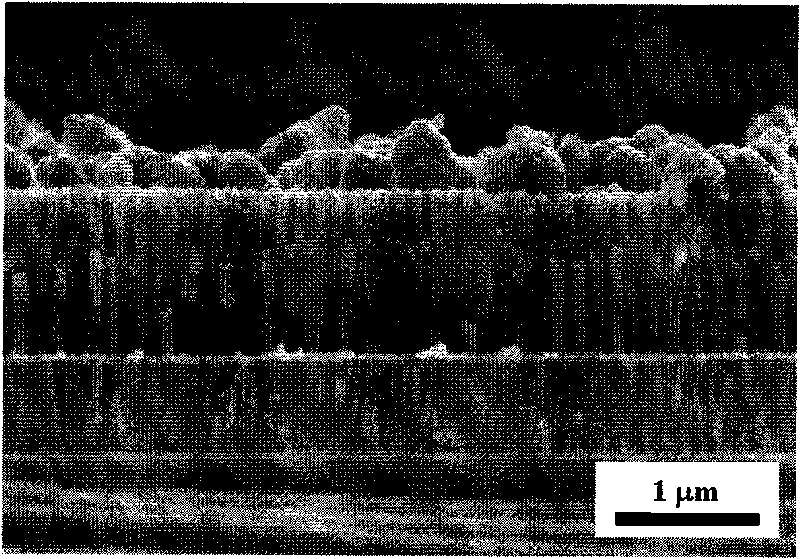

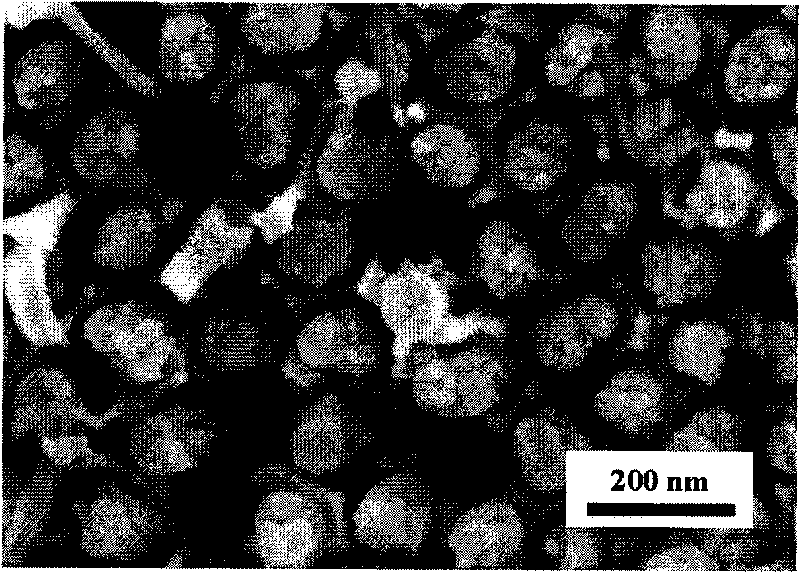

Schottky barrier diode and method for manufacturing schottky barrier diode

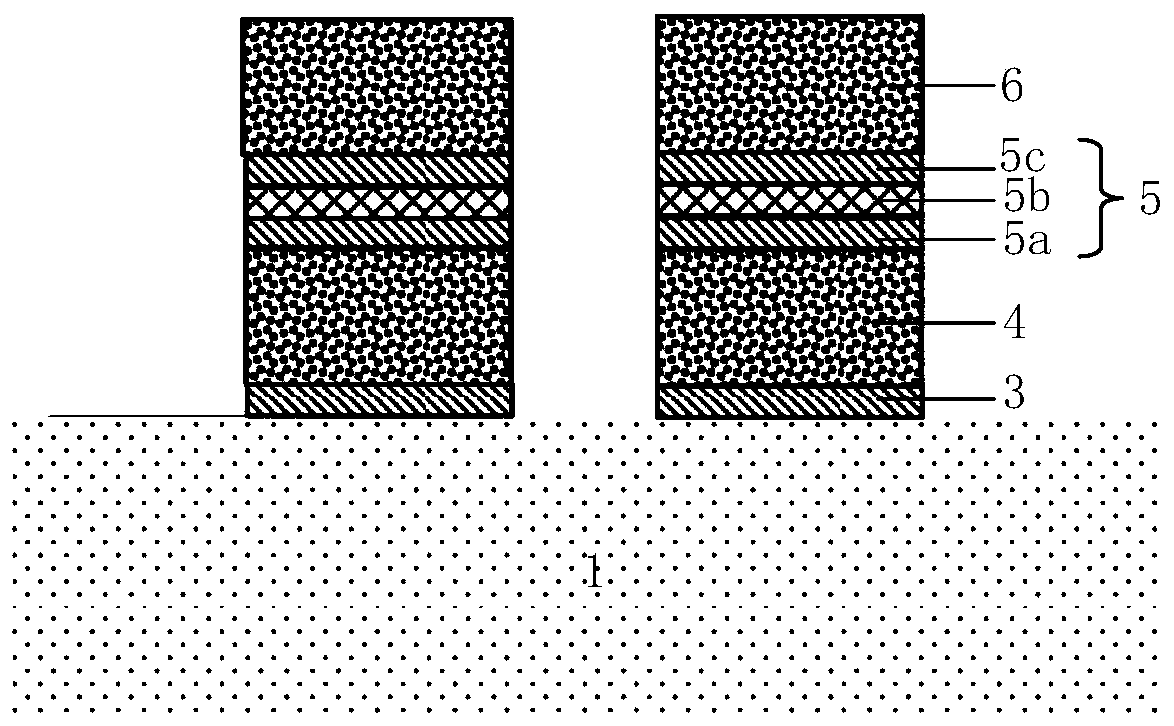

ActiveCN104465793AIncrease junction areaIncrease current densitySemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconSchottky barrier

A Schottky barrier diode and a method of manufacturing the diode are provided. The diode includes an n- type epitaxial layer disposed on a first surface of an n+ type silicon carbide substrate and a plurality of p+ regions disposed within the n- type epitaxial layer. An n+ type epitaxial layer is disposed on the n- type epitaxial layer, a Schottky electrode is disposed on the n+ type epitaxial layer, and an ohmic electrode is disposed on a second surface of the n+ type silicon carbide substrate. The n+ type epitaxial layer includes a plurality of pillar parts disposed on the n- type epitaxial layer and a plurality of openings disposed between the pillar parts and that expose the p+ regions. Each of the pillar parts includes substantially straight parts that contact the n- type epitaxial layer and substantially curved parts that extend from the substantially straight parts.

Owner:HYUNDAI MOTOR CO LTD

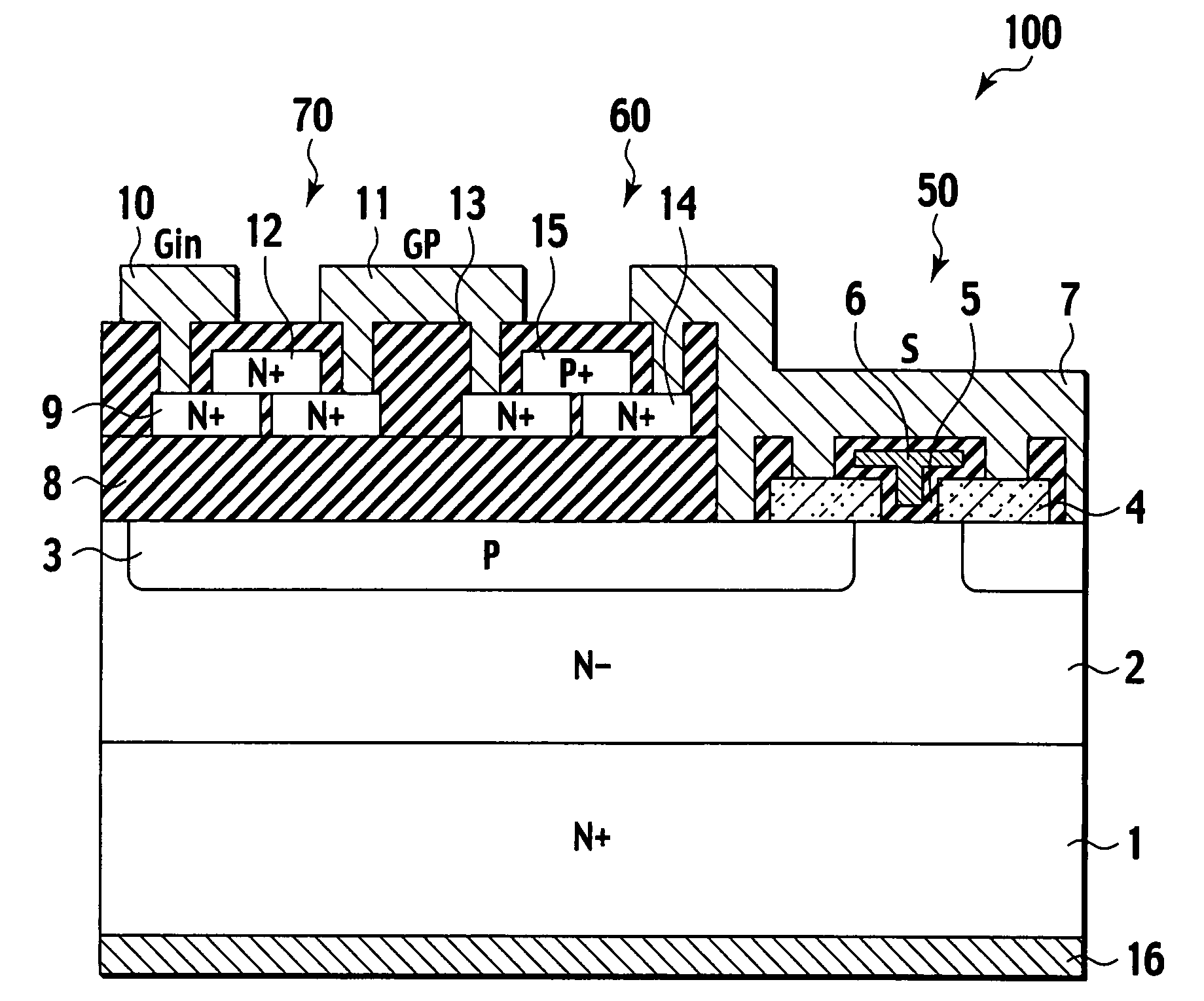

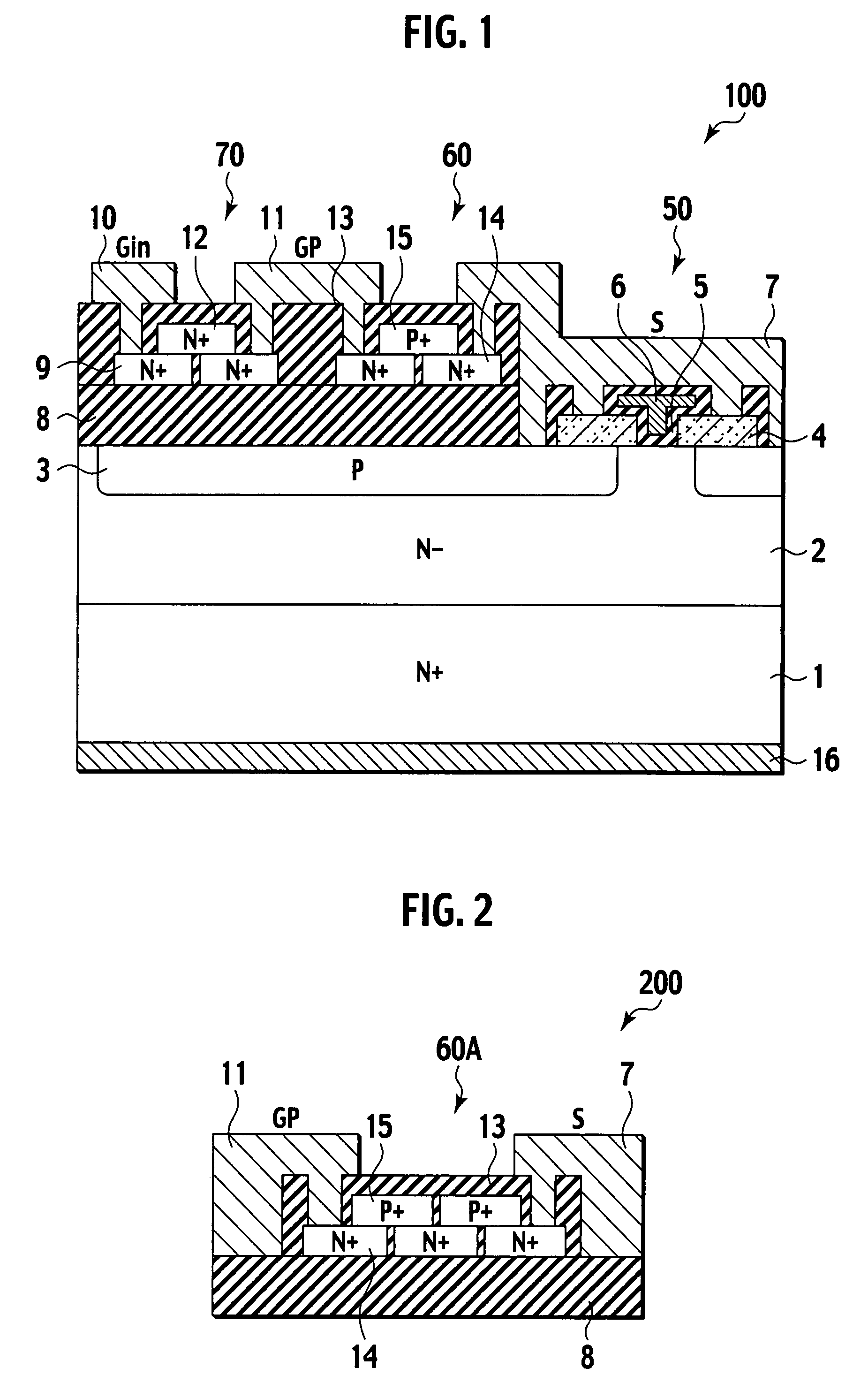

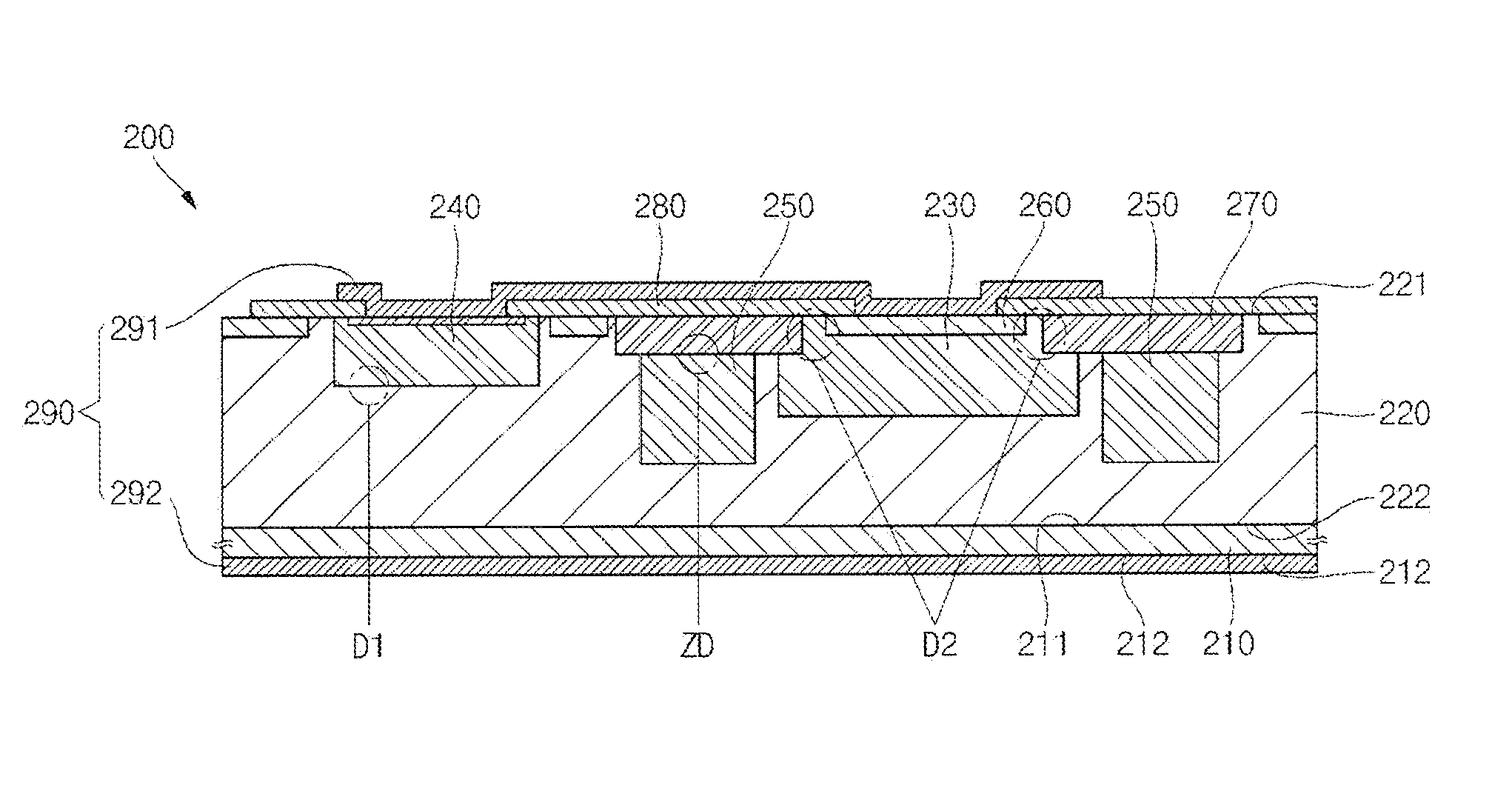

Semiconductor device and manufacturing method thereof

ActiveUS7695997B2Increase junction areaIncrease the resistance valueSemiconductor/solid-state device manufacturingDiodeZener diodeField-effect transistor

An electrostatic discharge protection element and a protection resistor, which are formed on an N− drain region with a field oxide film interposed therebetween for the purpose of preventing electrical breakdown of a field effect transistor, are composed as a stacked bidirectional Zener diode of one or a plurality of N+ polycrystalline silicon regions of a first layer and a P+ polycrystalline silicon region of a second layer, and a stacked resistor of one or a plurality of N+ resistor layers of the first layer and an N+ resistor layer of the second layer, respectively. One end of the plurality of N+ polycrystalline silicon regions of the first layer is connected to an external gate electrode terminal, and the other end is connected to a source electrode. One end of the plurality of N+ resistor layers of the first layer is connected to a gate electrode, and the other end is connected to the external gate electrode terminal. Semiconductor regions of the first layer and the second layer are formed by using semiconductor films, which form a hetero semiconductor region and the gate electrode, respectively.

Owner:NISSAN MOTOR CO LTD

Optical modulator

A novel phase shifter design for carrier depletion based silicon modulators, based on an experimentally validated model, is described. It is believed that the heretofore neglected effect of incomplete ionization will have a significant impact on ultra-responsive phase shifters. A low VπL product of 0.3V·cm associated with a low propagation loss of 20 dB / cm is expected to be observed. The phase shifter is based on overlapping implantation steps, where the doses and energies are carefully chosen to utilize counter-doping to produce an S-shaped junction. This junction has a particularly attractive VπL figure of merit, while simultaneously achieving attractively low capacitance and optical loss. This improvement will enable significantly smaller Mach-Zehnder modulators to be constructed that nonetheless would have low drive voltages, with substantial decreases in insertion loss. The described fabrication process is of minimal complexity; in particular, no high-resolution lithographic step is required.

Owner:NOKIA SOLUTIONS & NETWORKS OY

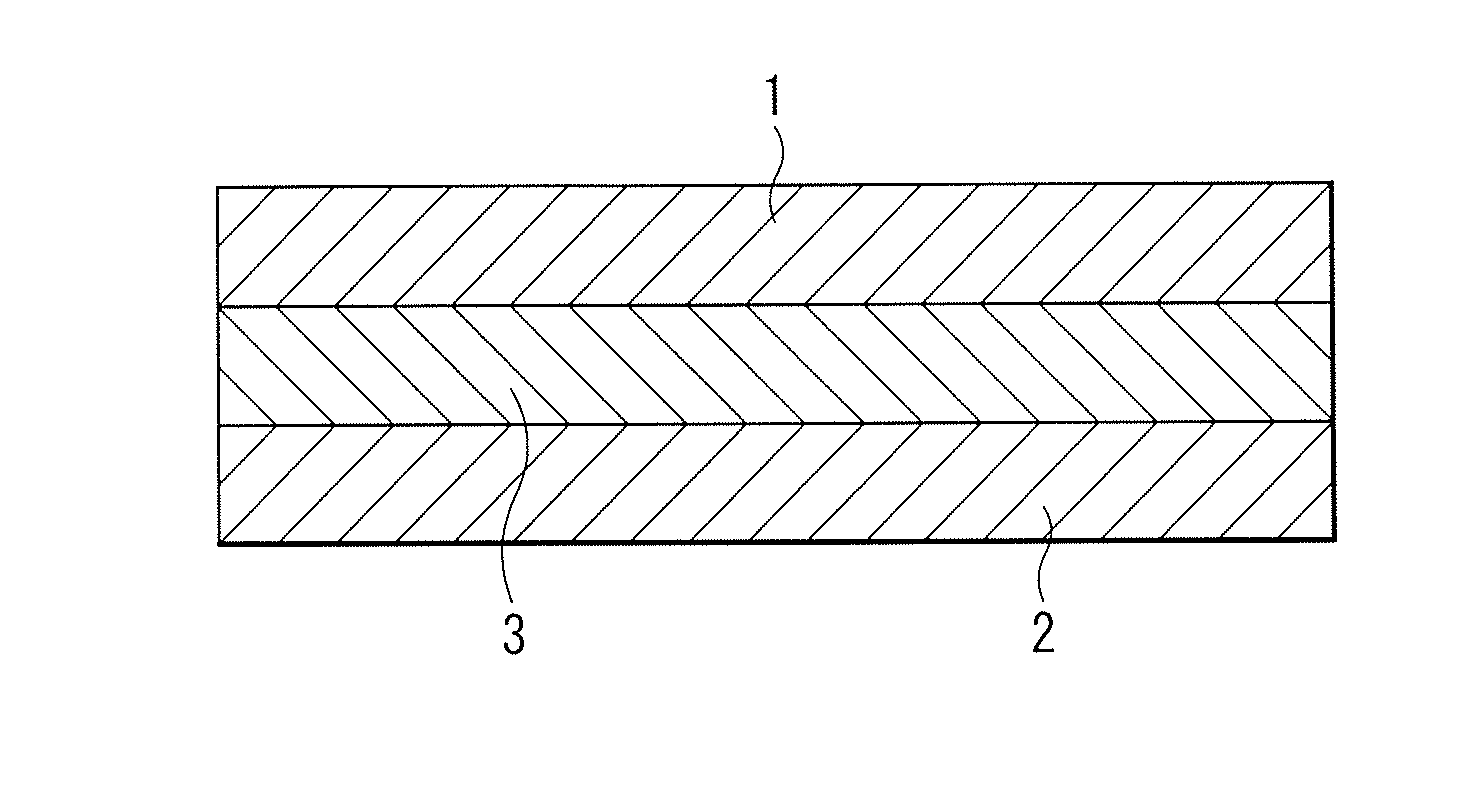

Electro-static discharge (ESD) protective circuit

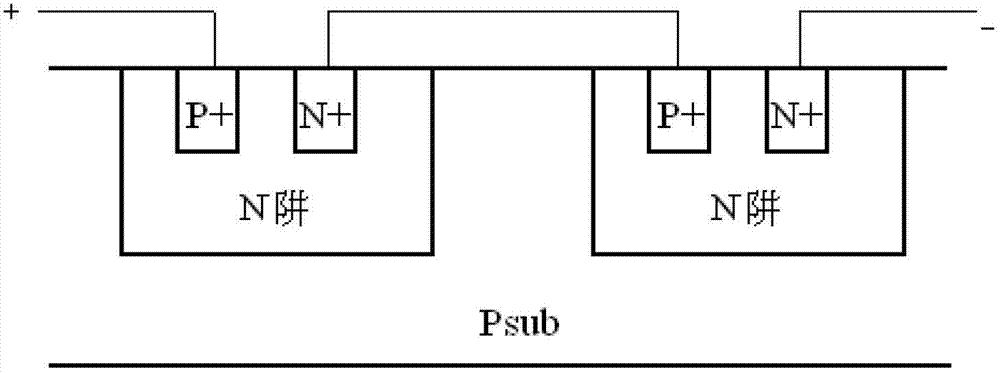

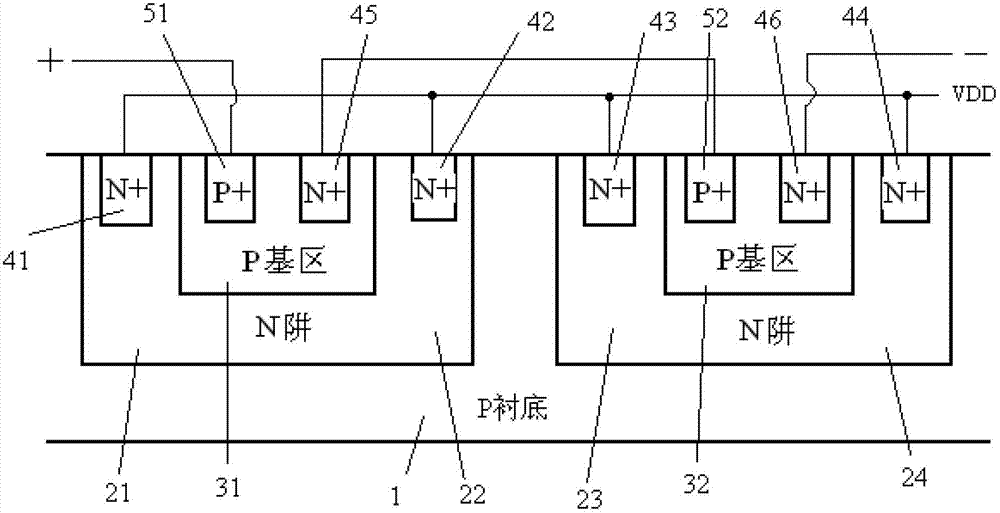

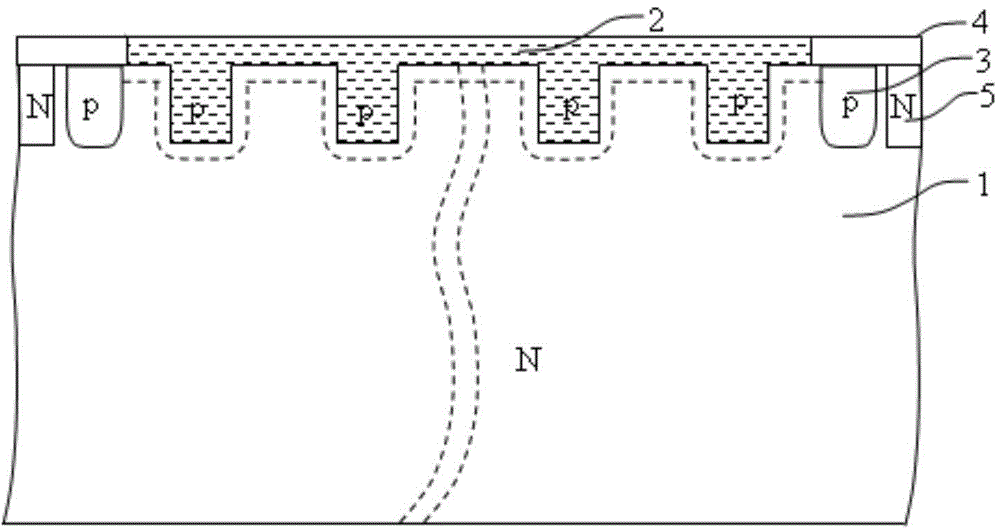

ActiveCN103165600AInhibition byIncrease junction areaSolid-state devicesSemiconductor devicesElectricityEngineering

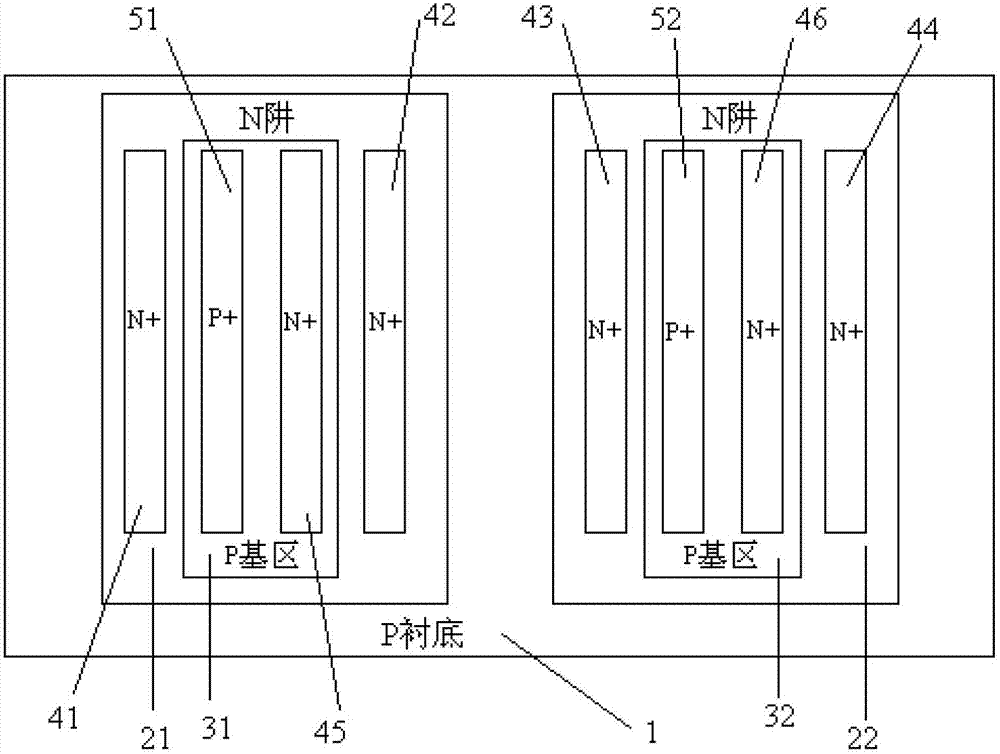

The invention relates to an electro-static discharge (ESD) protective circuit. The ESD protective circuit is in a diode series structure which is capable of restraining a Darlington effect. According to the ESD protective circuit, two ends of a P substrate are respectively provided with two N traps, wherein the bottoms of each two traps are connected into a whole. A P base region is arranged between each two N traps. Each N trap of four N traps is provided with an N+ diffusion active region. Each P base region is provided with a P+ diffusion active region and an N+ diffusion active region. Four of N+ diffusion active regions are connected through wires, and then are connected with power source potential voltage drain drain (VDD). A first P+ diffusion active region is connected with an electricity positive electrode. A fifth N+ diffusion active region is connected with a second P+ diffusion active region through wires. A sixth N+ diffusion active region is connected with an electricity negative electrode. The ESD protective circuit has the advantages of greatly reducing currents flowing to the P substrate, and being capable of effectively restraining the Darlington effect, good in clamping capacity, small in leakage current, good in ESD resistant capacity of unit area, and capable of effectively restraining occurrence of a latch-up effect.

Owner:BEIJING MXTRONICS CORP +1

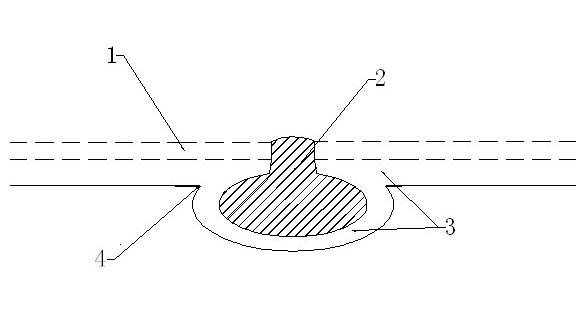

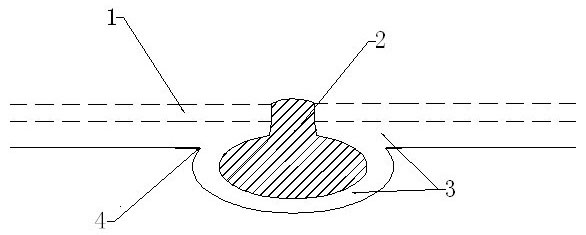

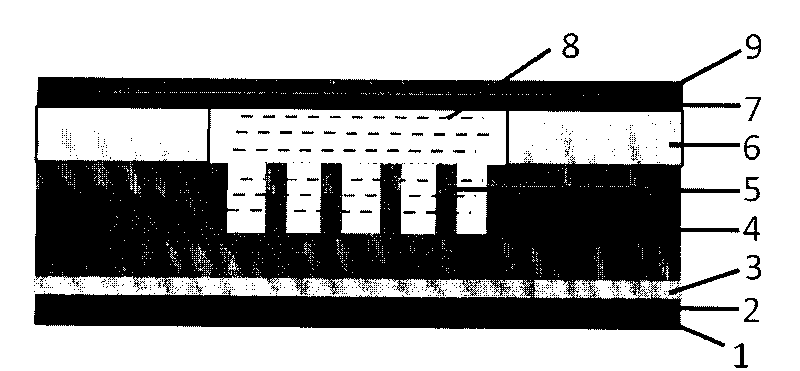

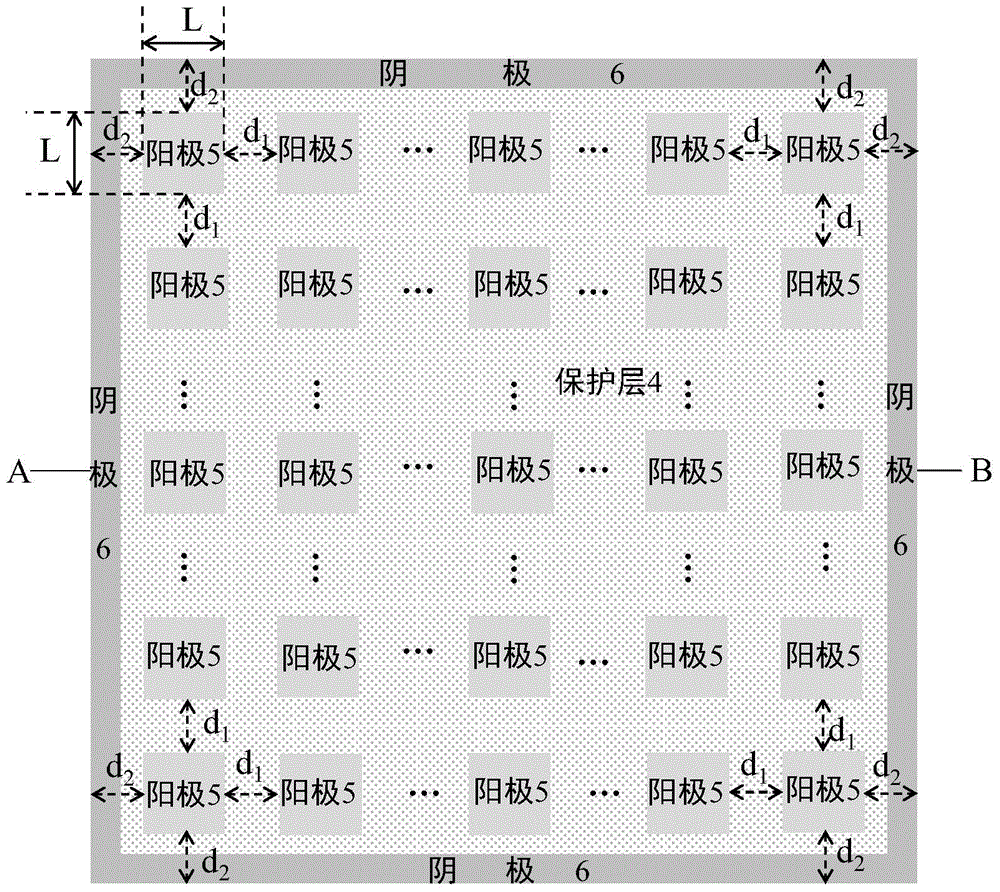

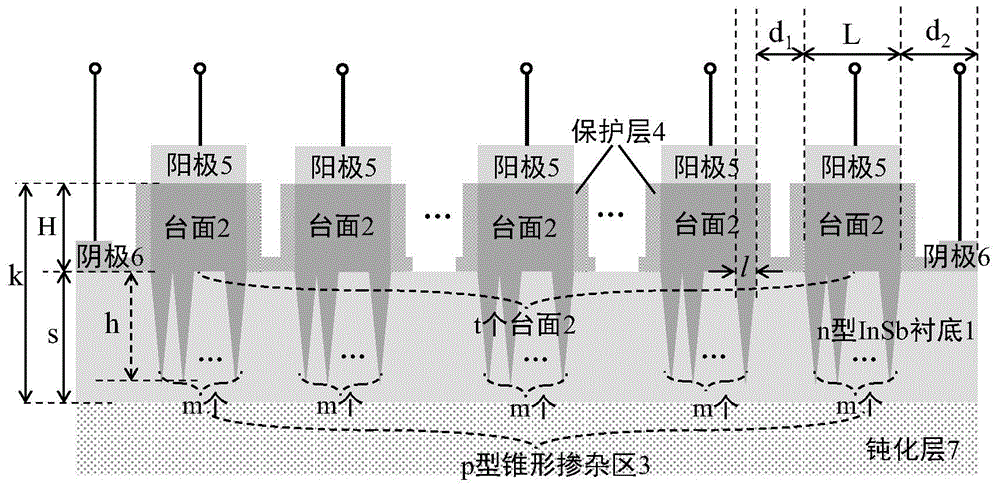

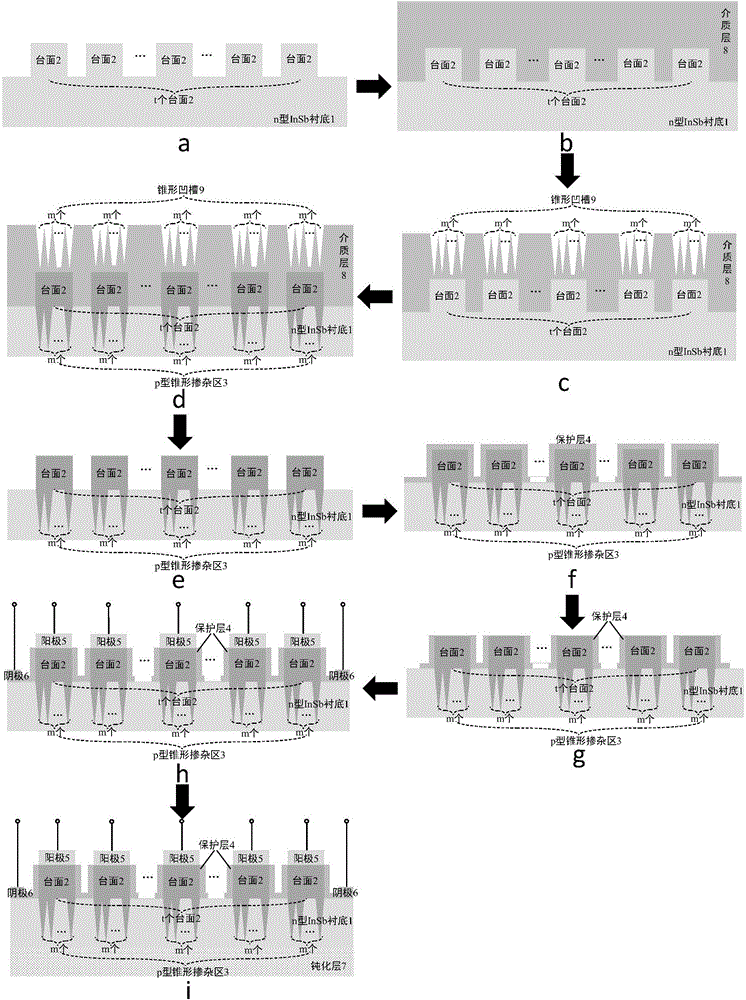

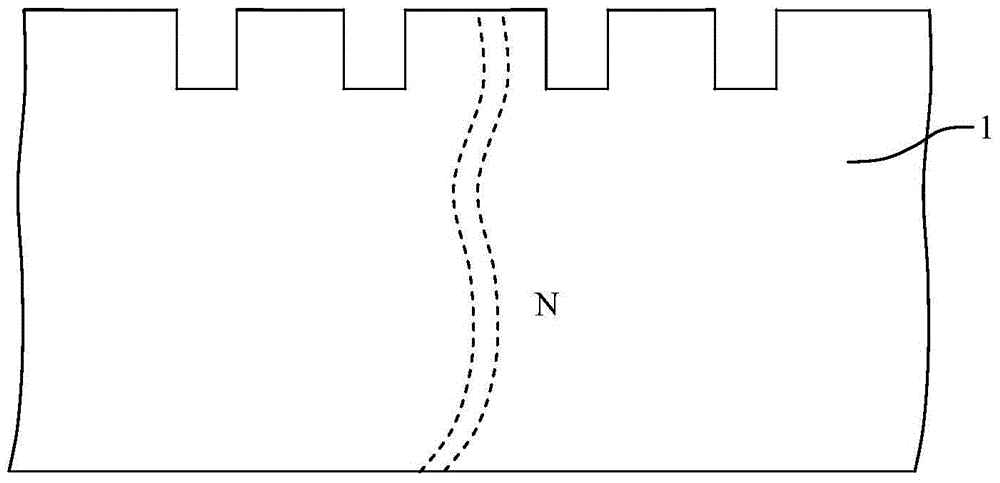

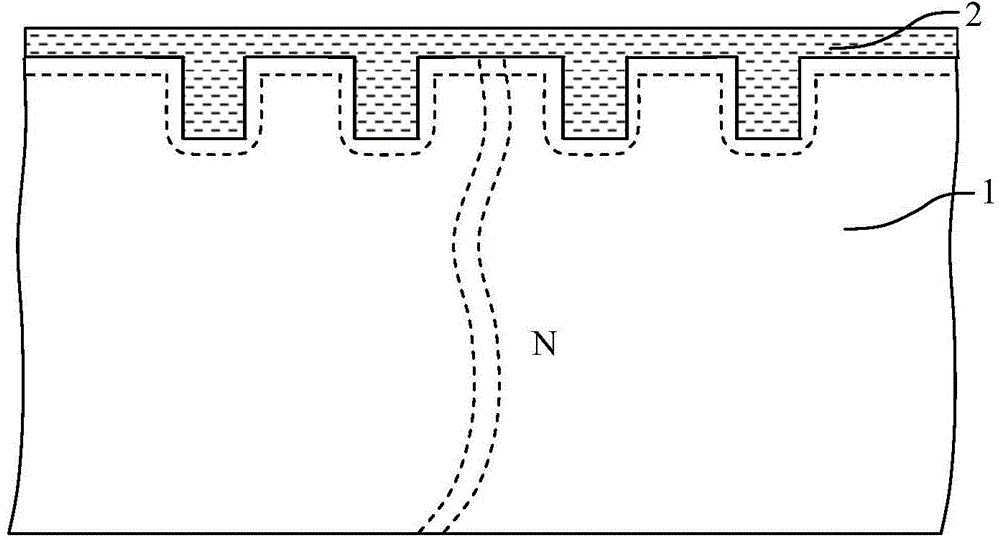

Infrared detector array and manufacturing method thereof

InactiveCN104465686AReduce distanceReduce crosstalkFinal product manufactureRadiation controlled devicesQuantum efficiencyChinese characters

The invention discloses an infrared detector array and a manufacturing method of the infrared detector array. The detector array comprises an n-type InSb substrate (1) and a passivation layer (7), t*t tabletops (2) are etched on the n-type InSb substrate (1), wherein t is an integer and is greater than or equal to one; an anode (5) is deposited on each tabletop (2), and an cathode (6) shaped like the Chinese character 'hui' is deposited on the upper portion of the edge of the n-type InSb substrate (1); the upper portion of the n-type InSb substrate (1) and the side face of each tabletop (2) are each provided with a protection layer (4) in a deposited mode; m*m identical p-type conical doping areas (3) are arranged in the positions, under each tabletop (2), of the n-type InSb substrate (1) to from a p-type conical doping area array, and one pn junction is formed between each p-type conical doping area (3) and the n-type InSb substrate (1), wherein m is an integer and is greater than or equal to one. The infrared detector array has the advantages of being simple in process, high in quantum efficiency and low in crosstalk, and can be used for the fields of infrared investigation and infrared medical treatment.

Owner:XIDIAN UNIV

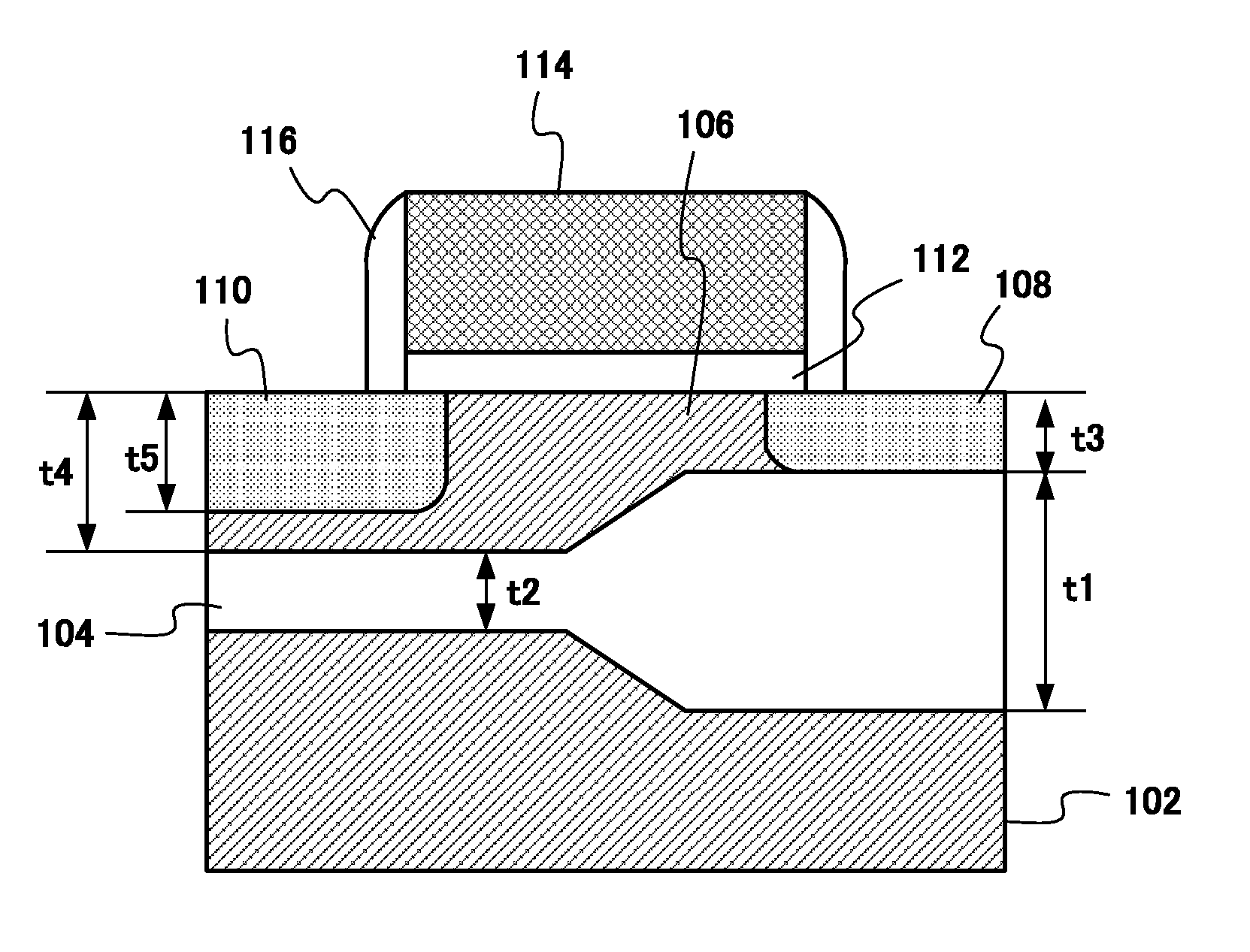

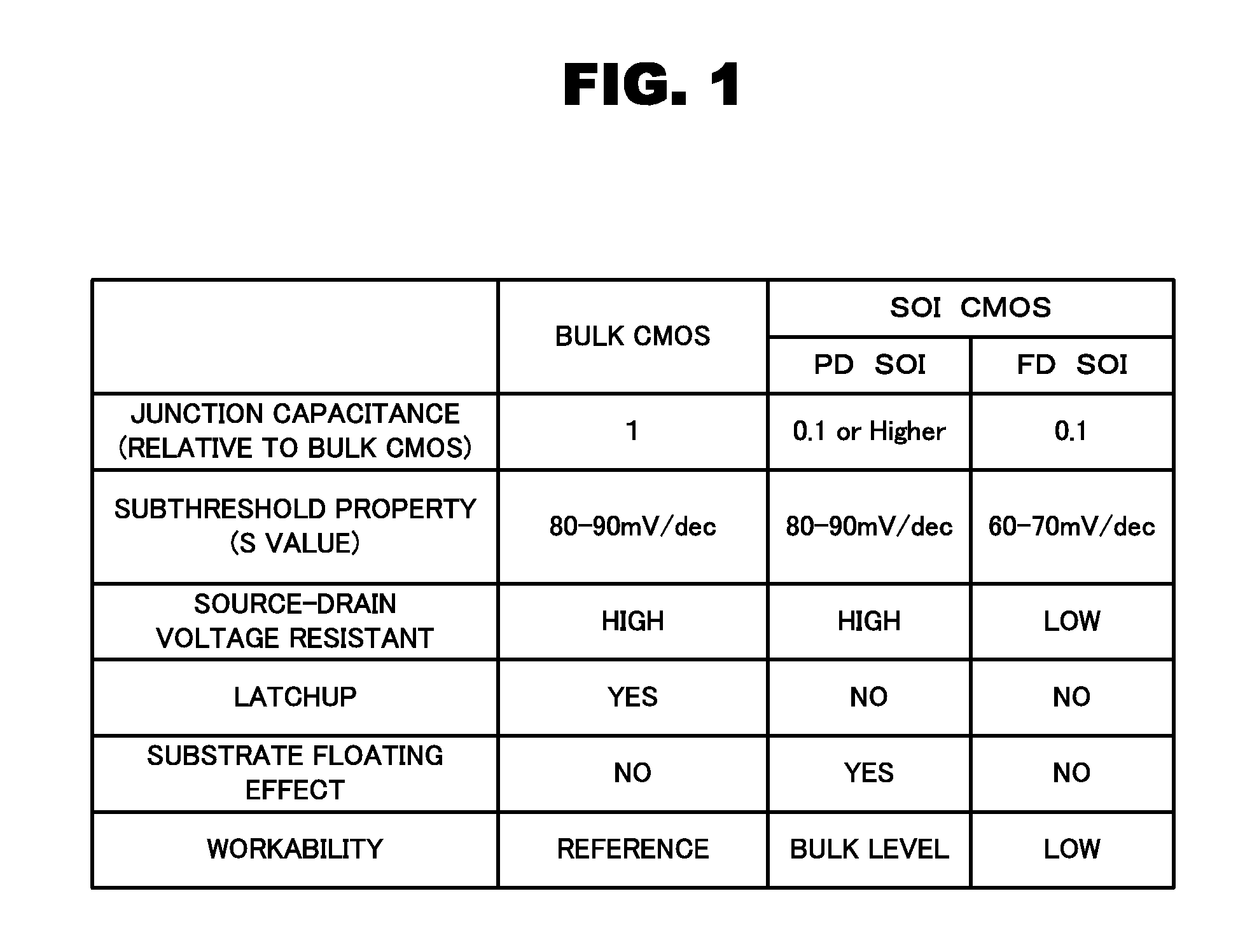

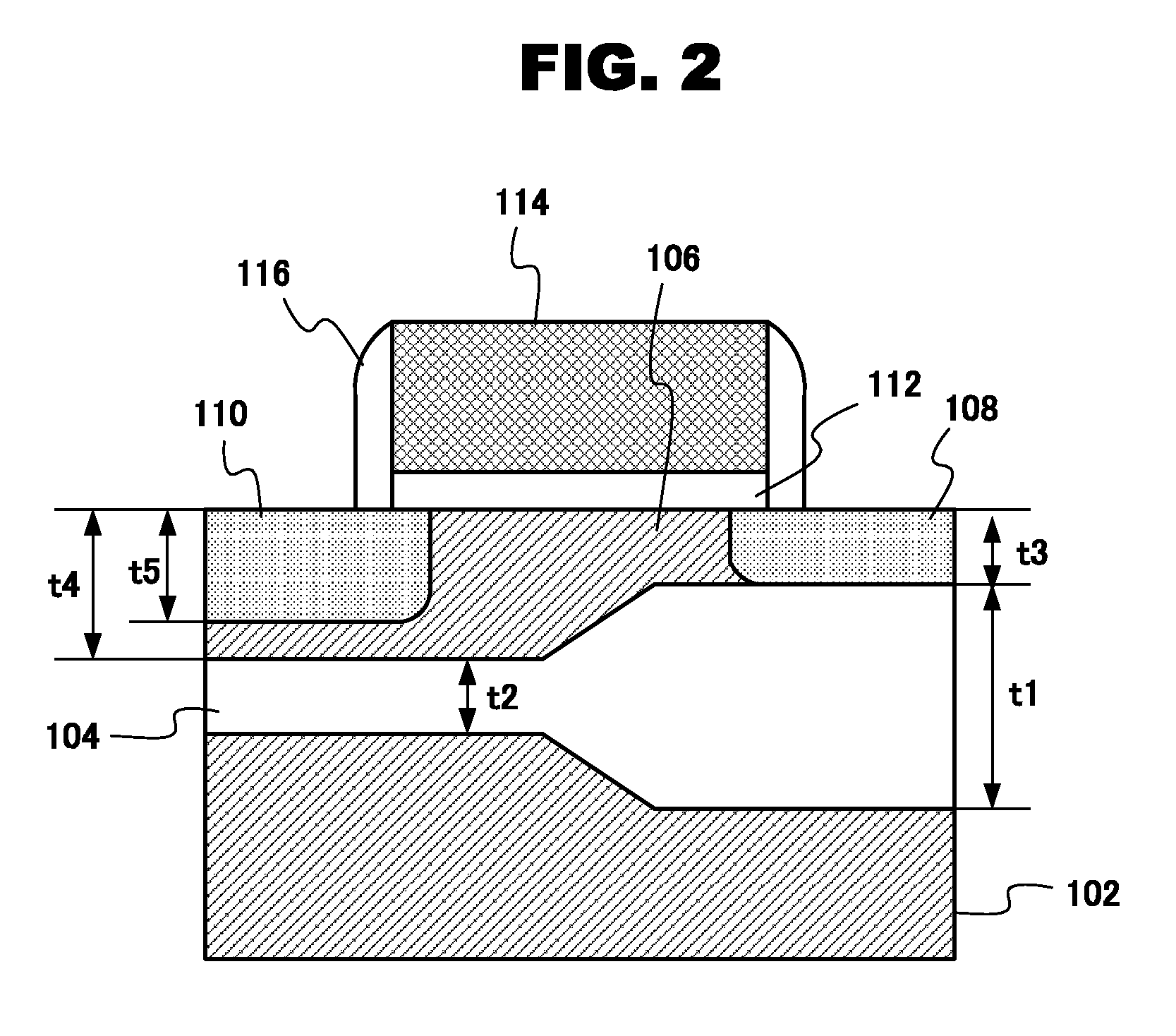

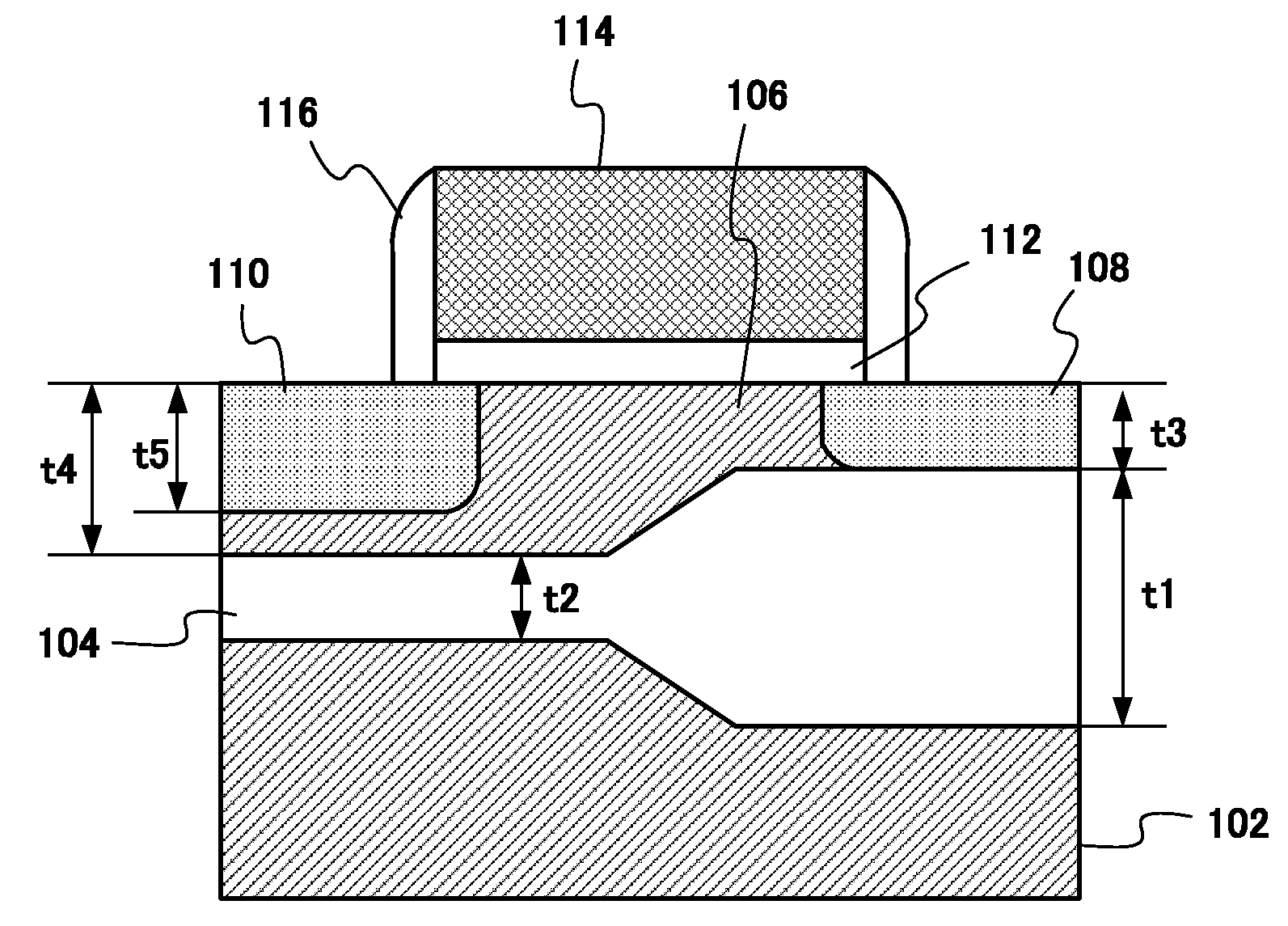

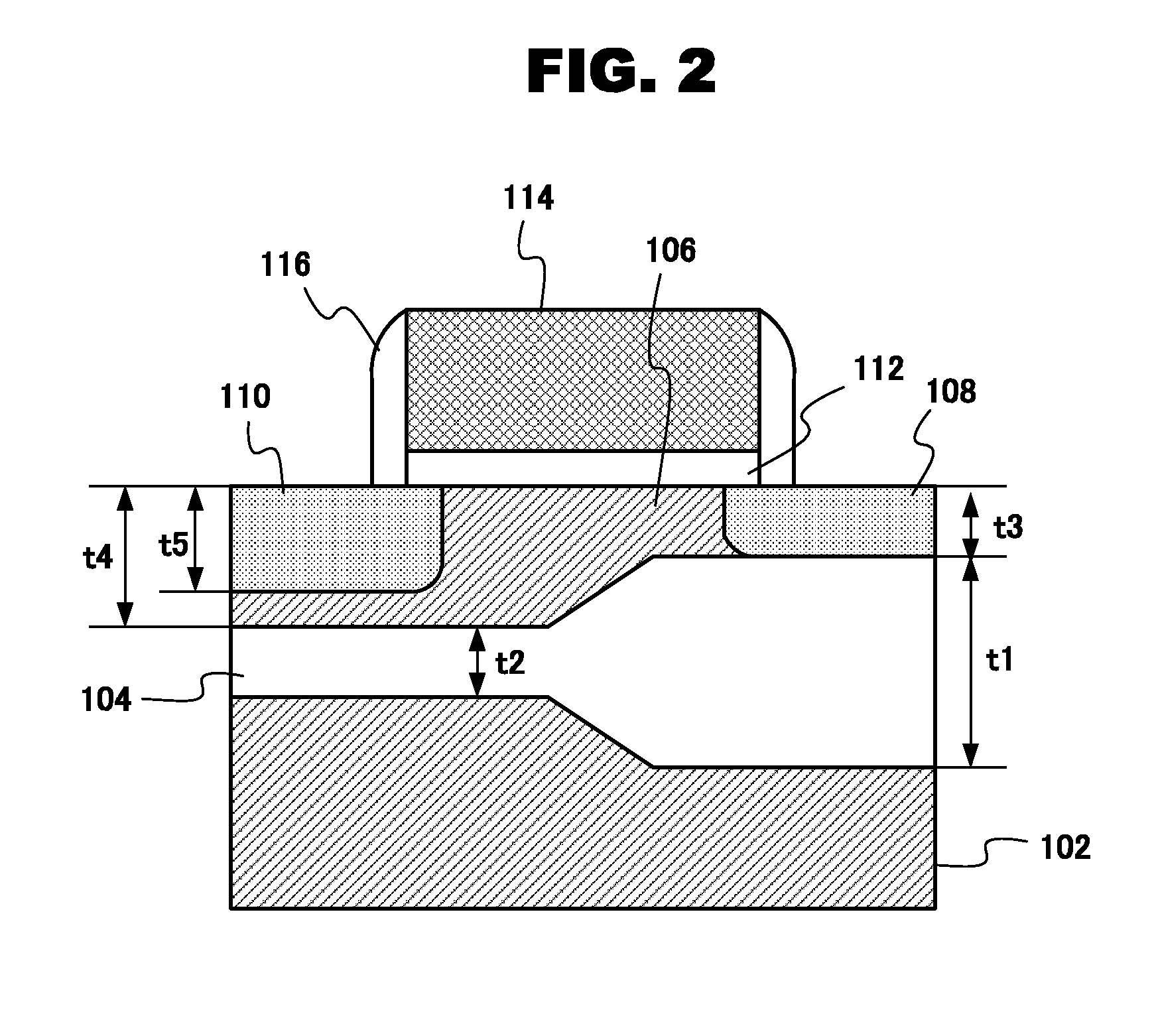

Semiconductor device using SOI-substrate

ActiveUS7859063B2Improve powerImprove pressure resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateSilicon

According to a feature of the present invention, a semiconductor device includes a SOI substrate, including a semiconductor substrate; an insulating layer formed on the semiconductor substrate and a silicon layer formed on the insulating layer. A drain region and a source region are formed in the silicon layer so that the source region is in contact with the insulating layer but the drain region is not in contact with the insulating layer.

Owner:LAPIS SEMICON CO LTD

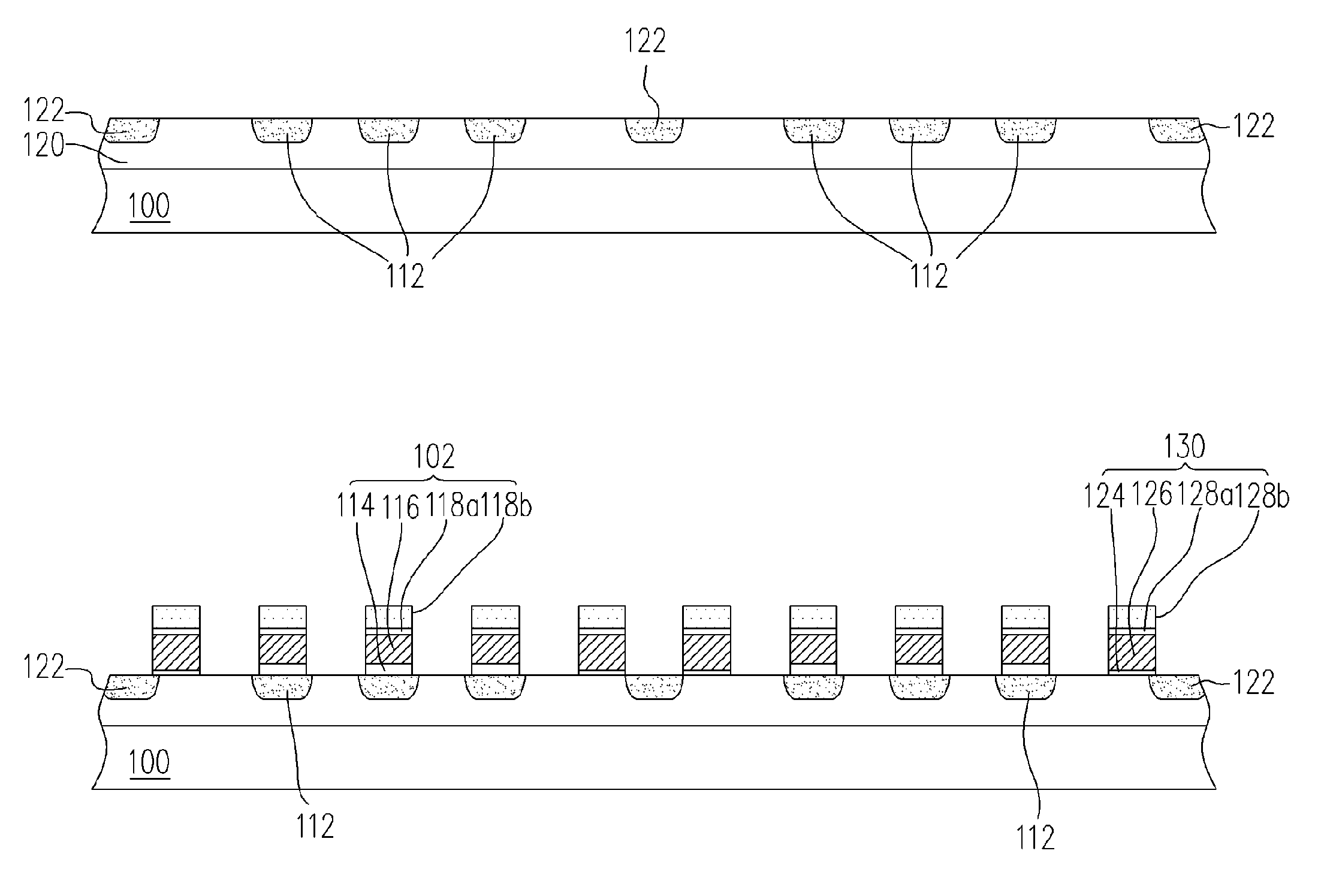

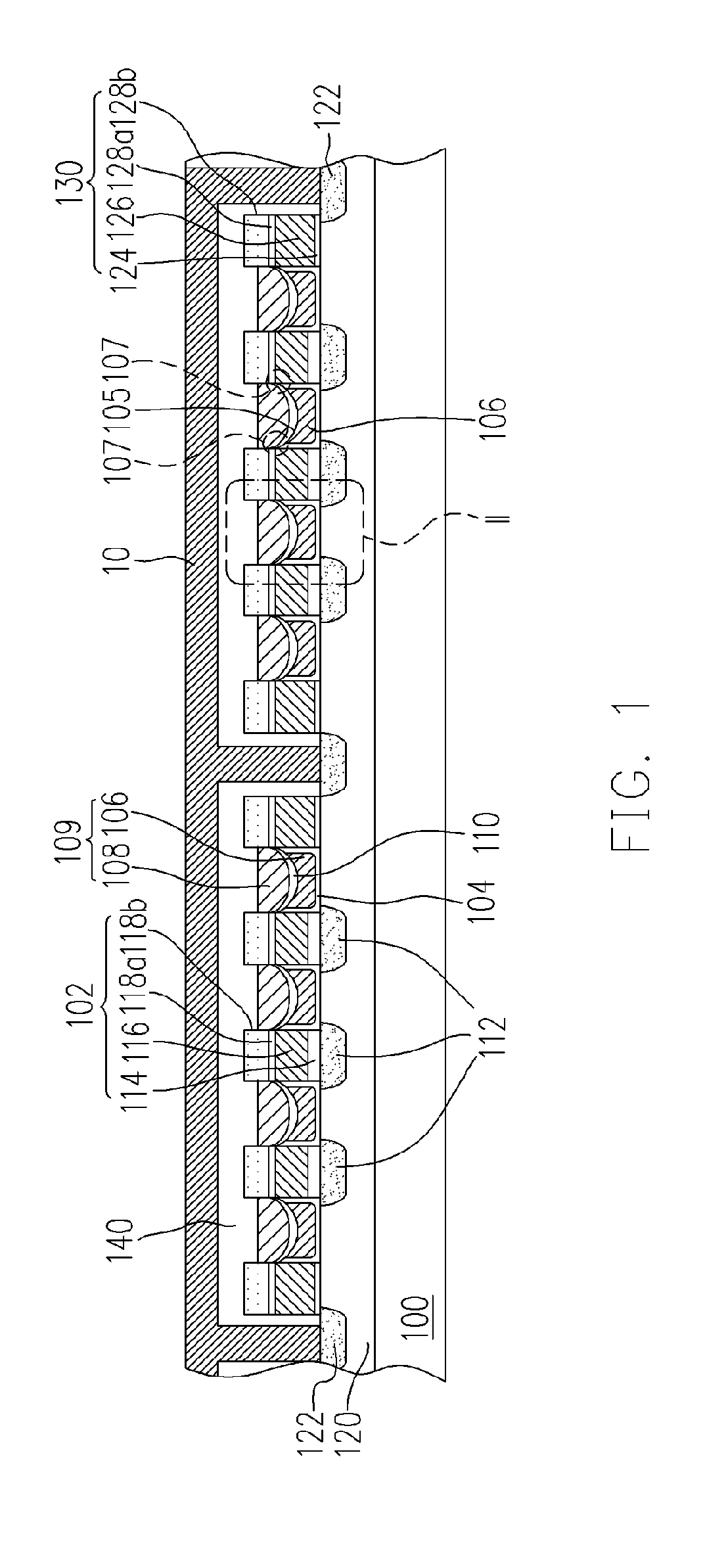

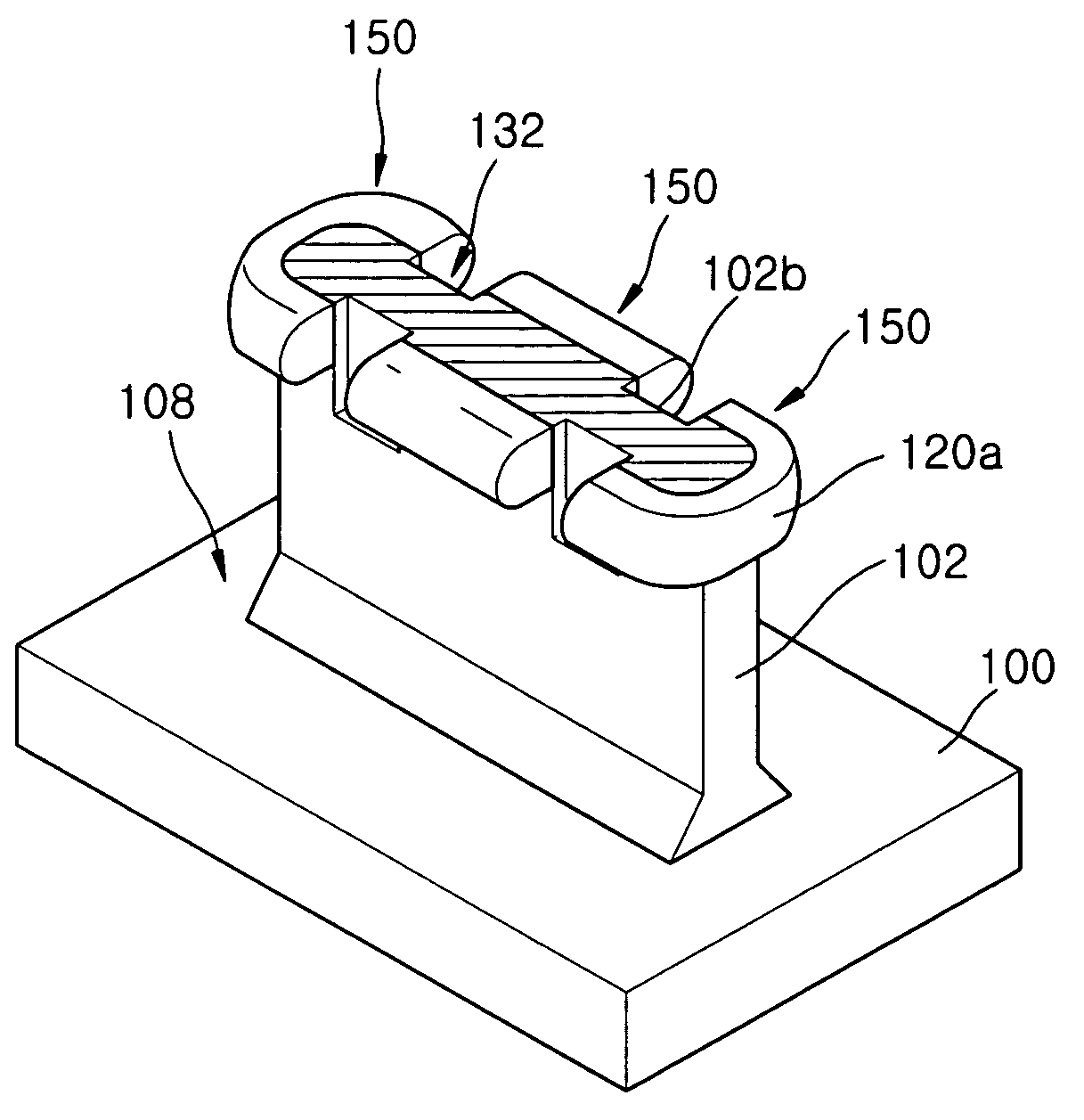

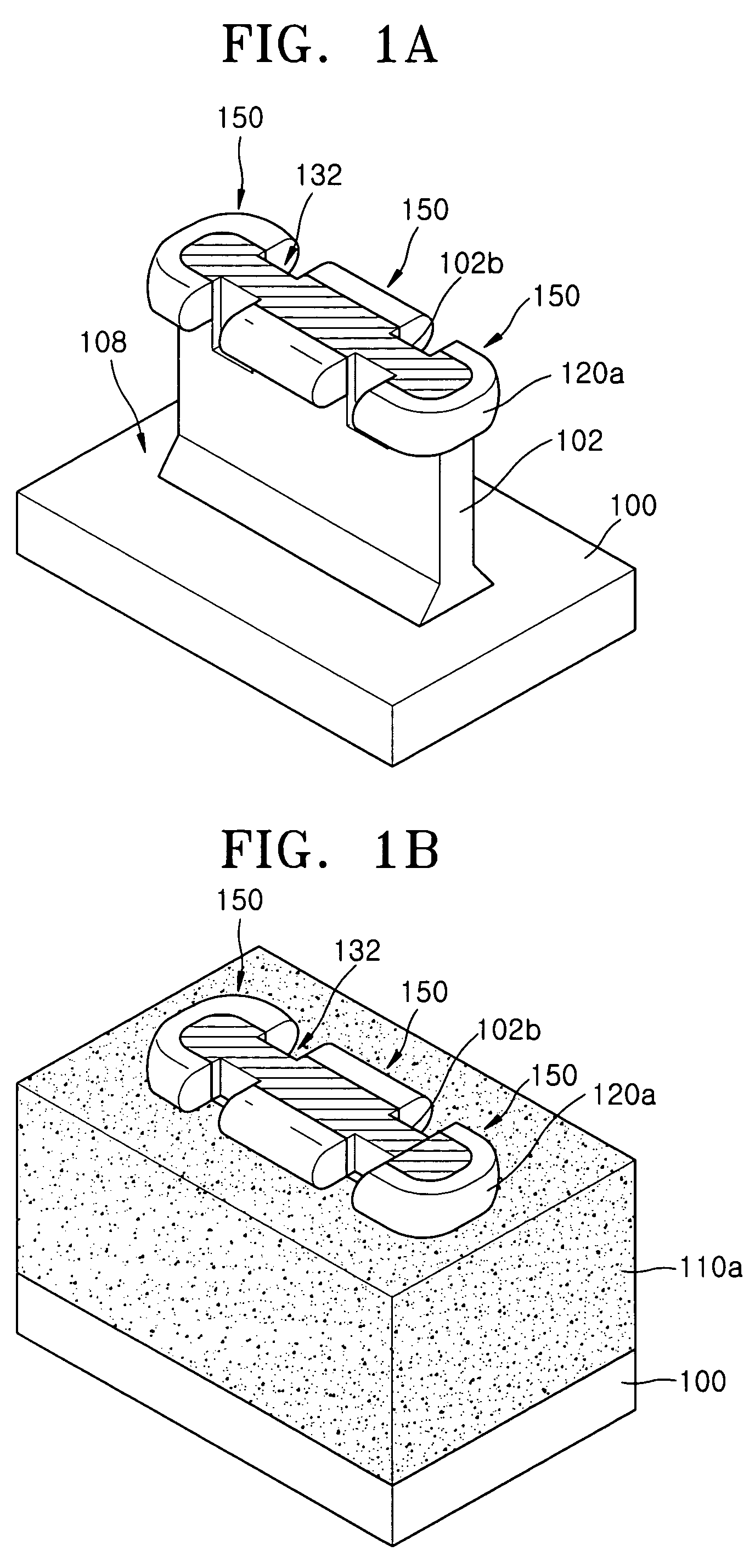

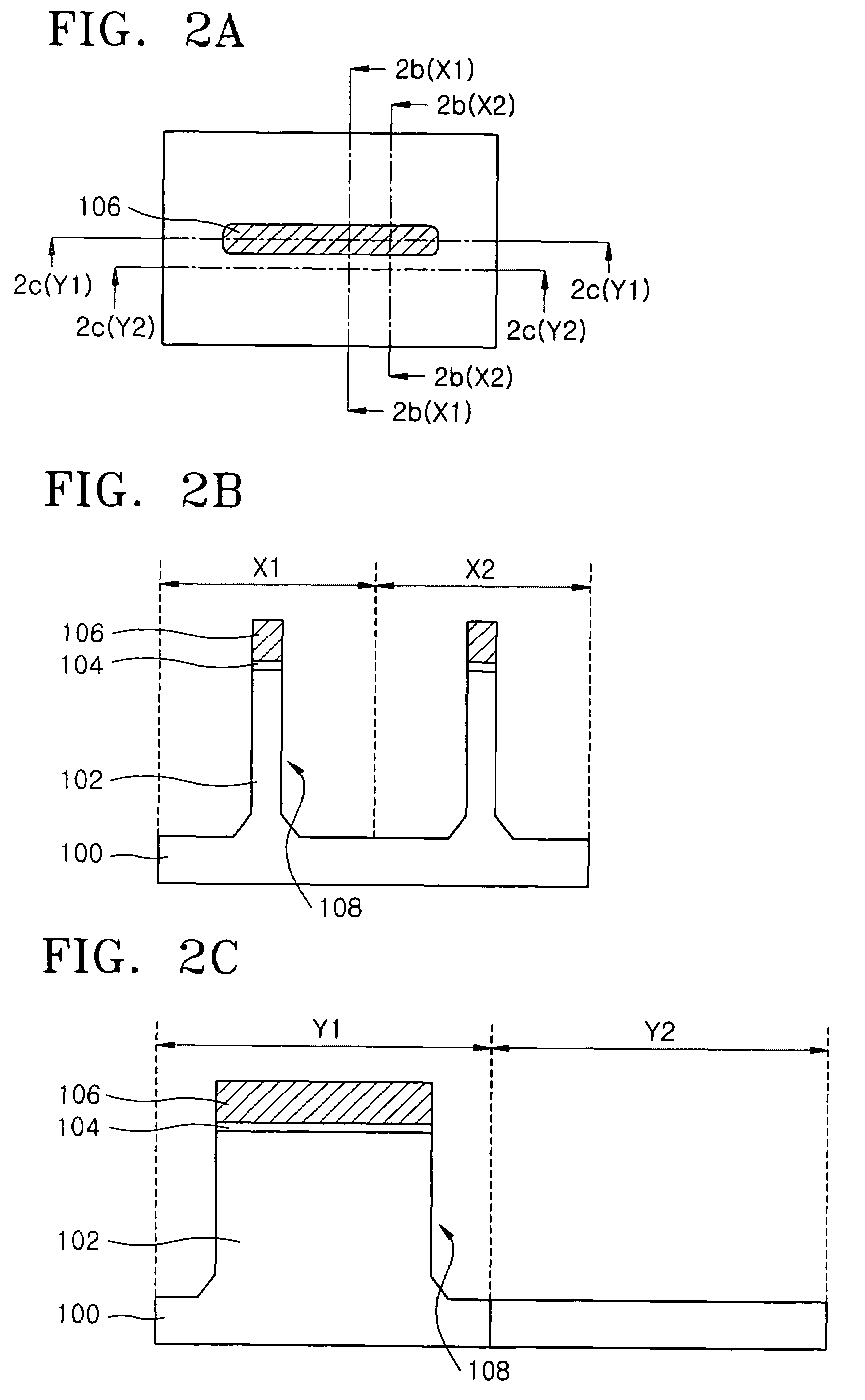

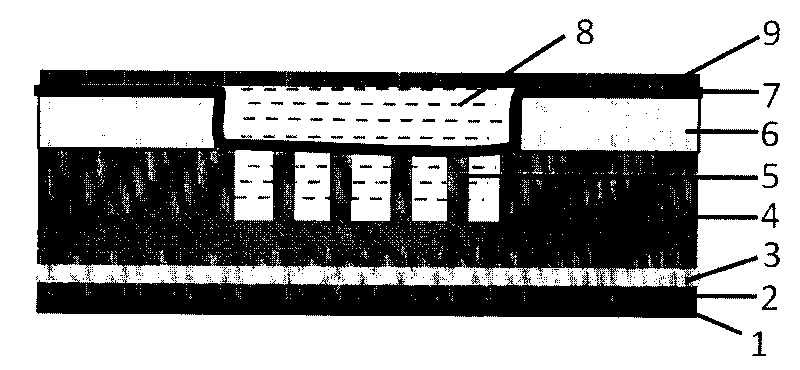

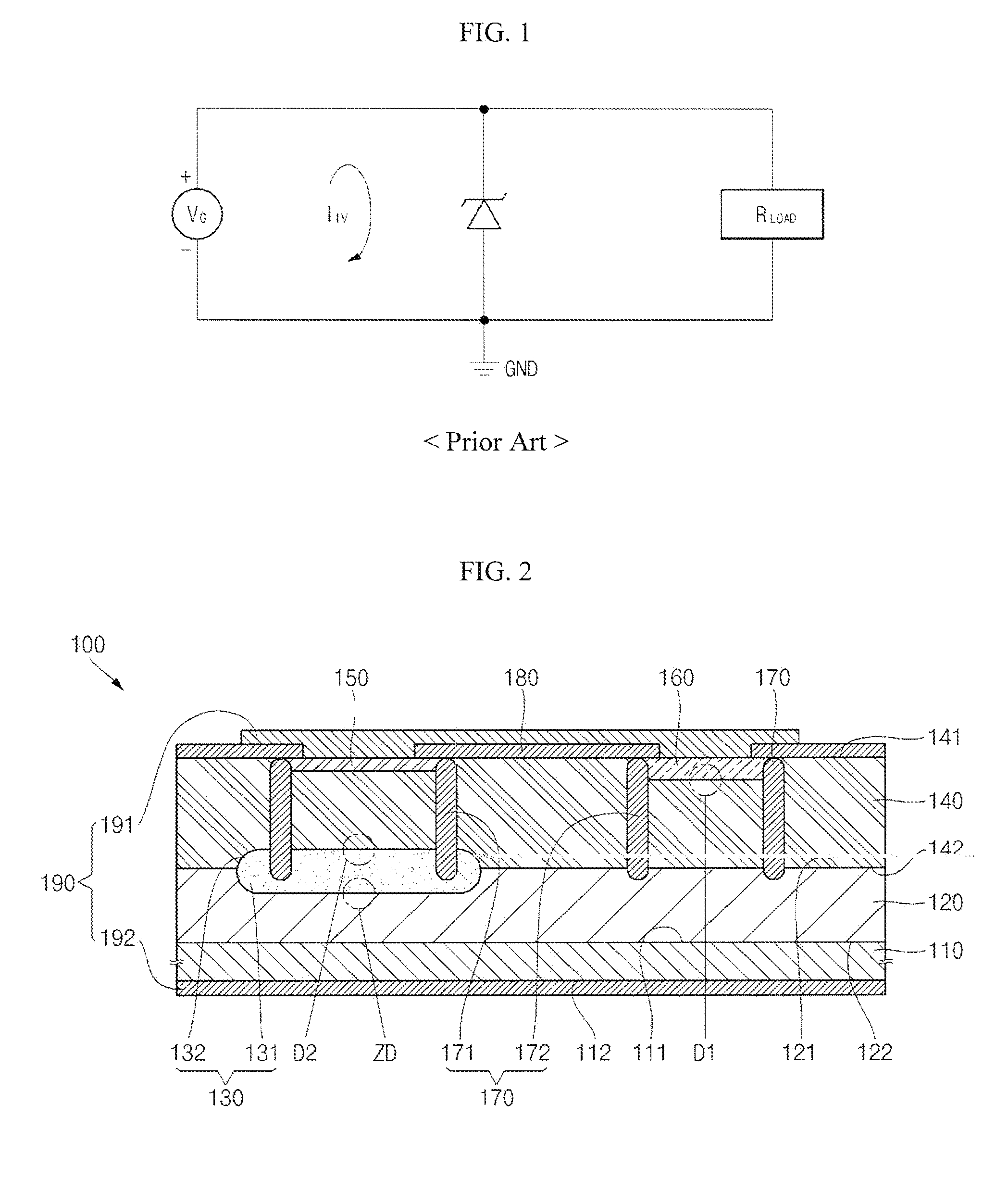

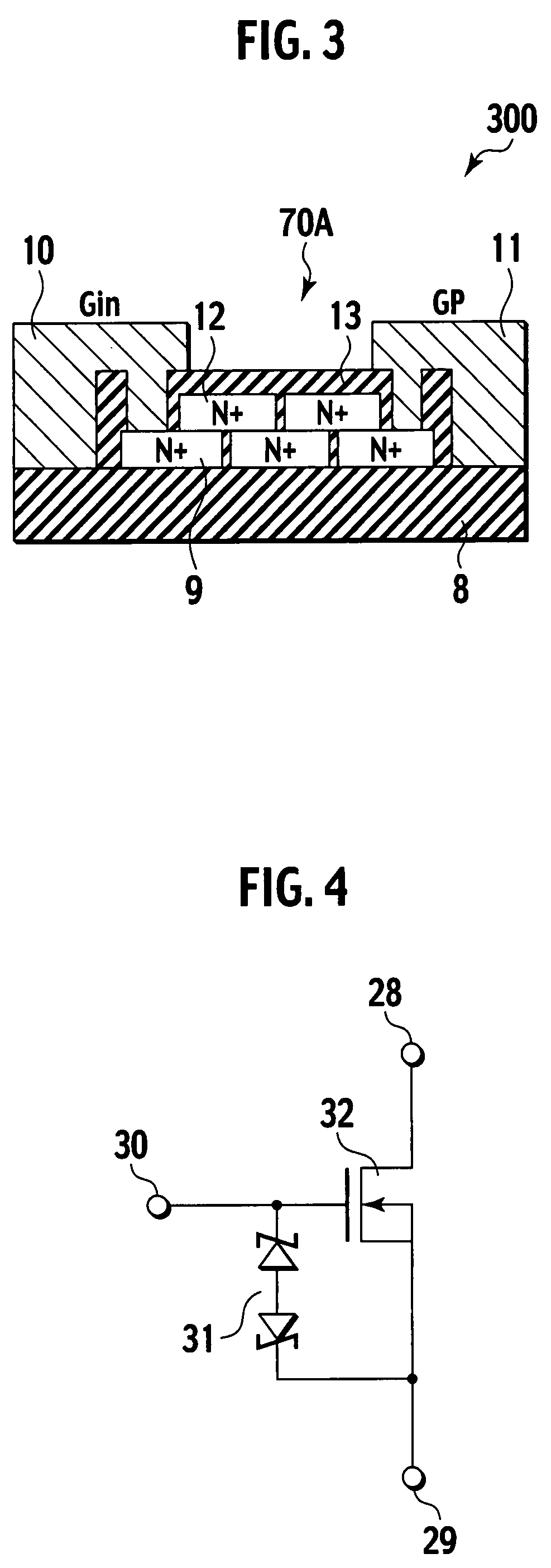

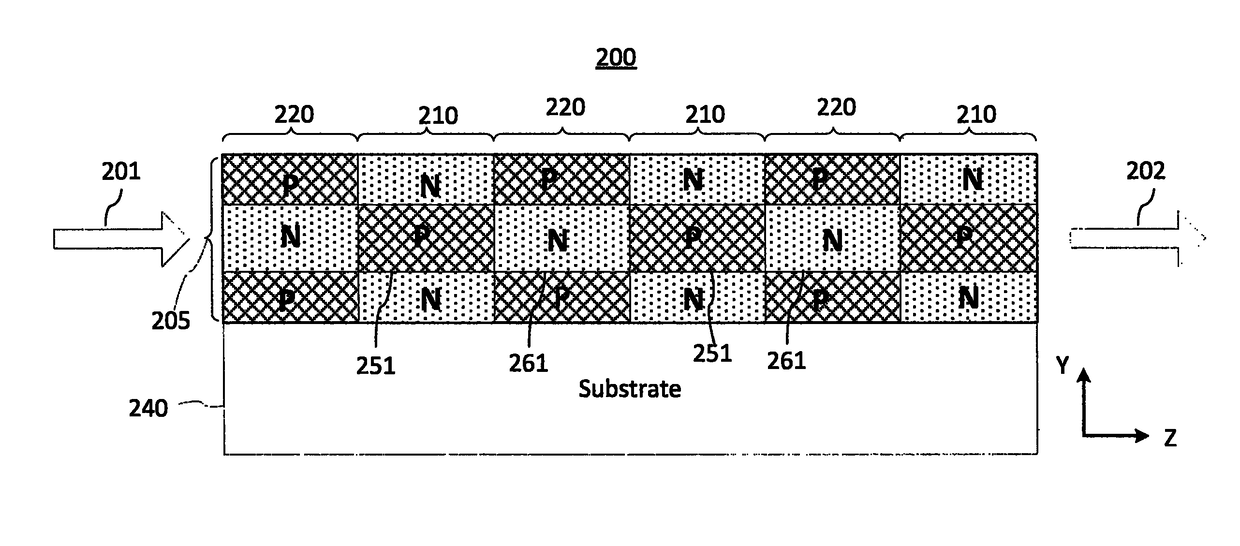

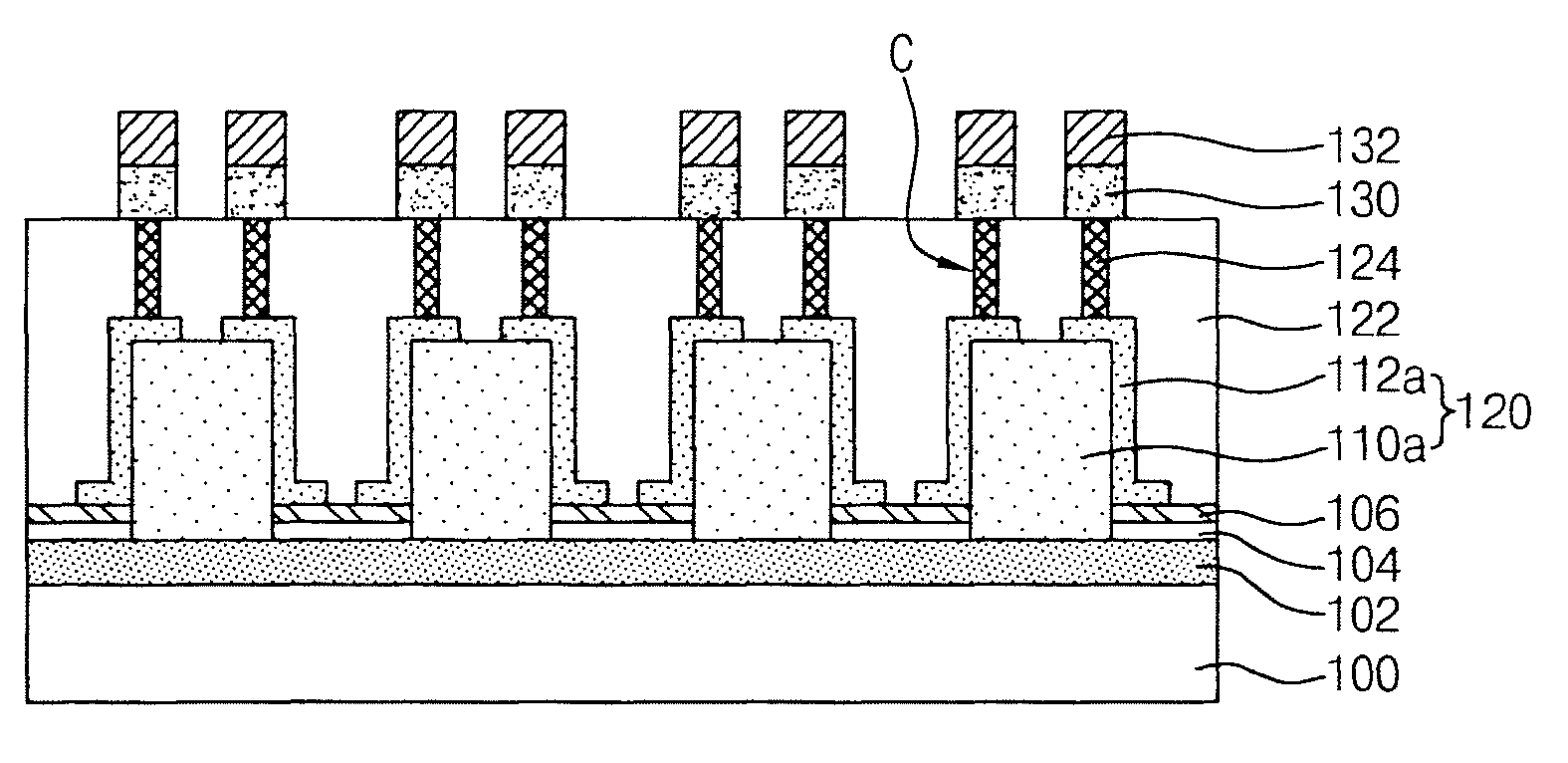

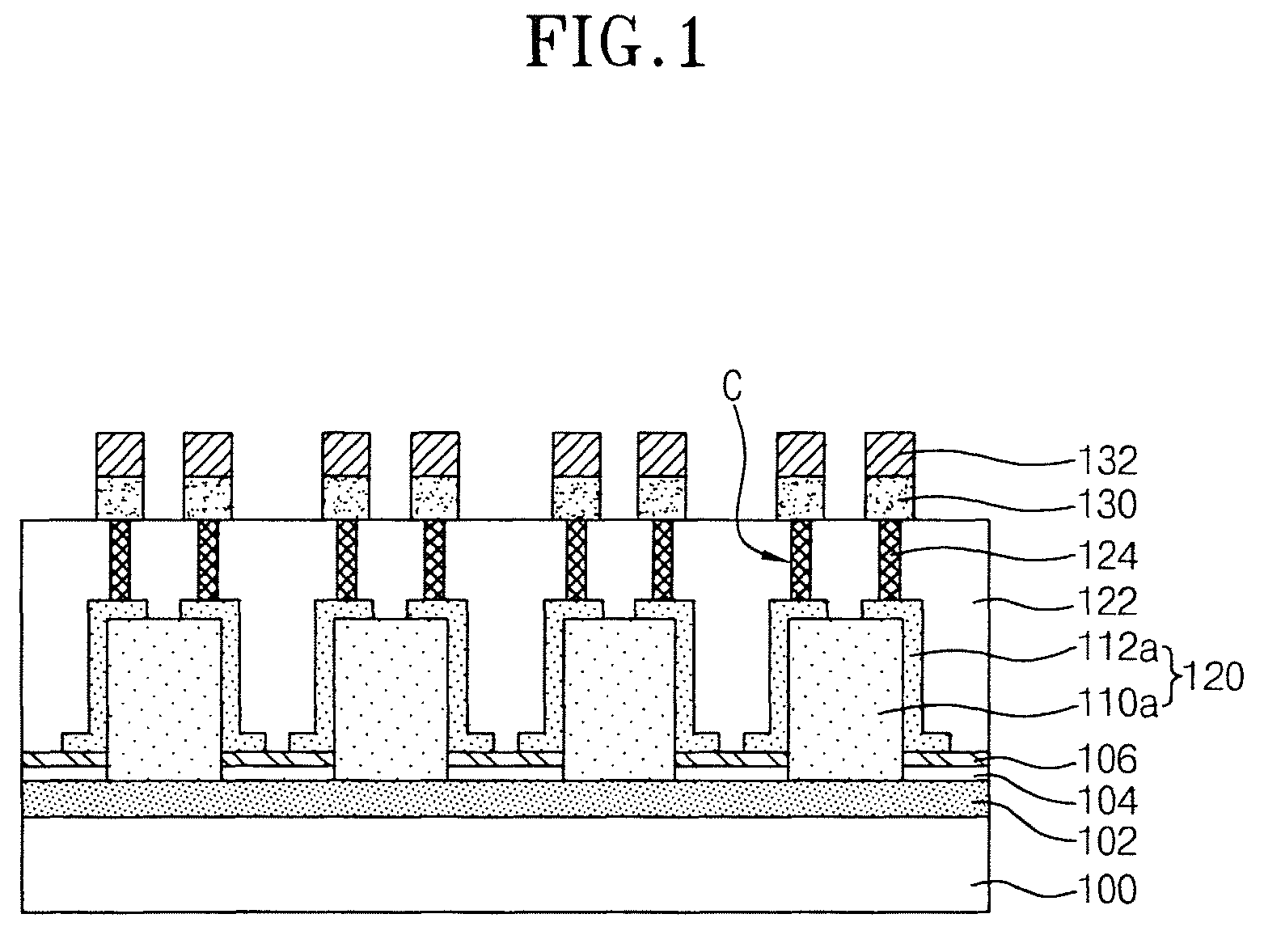

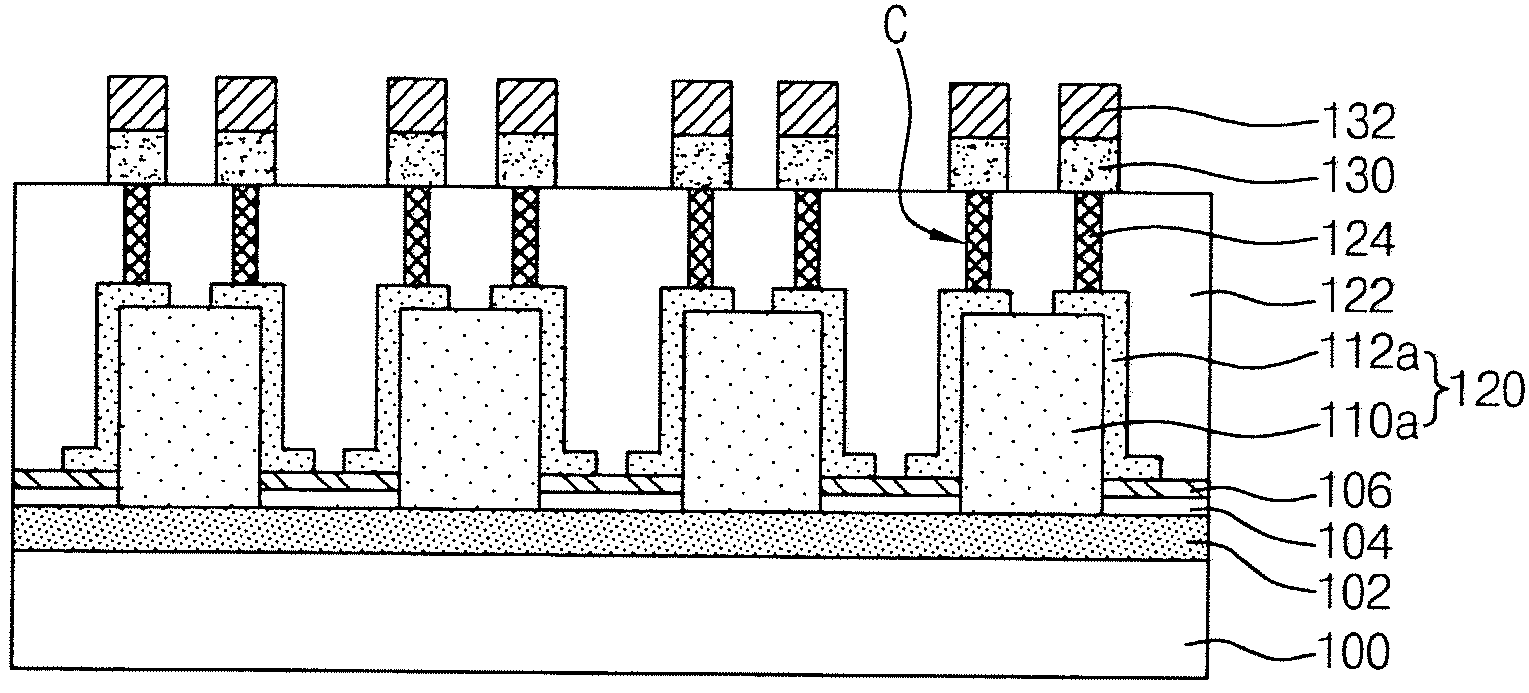

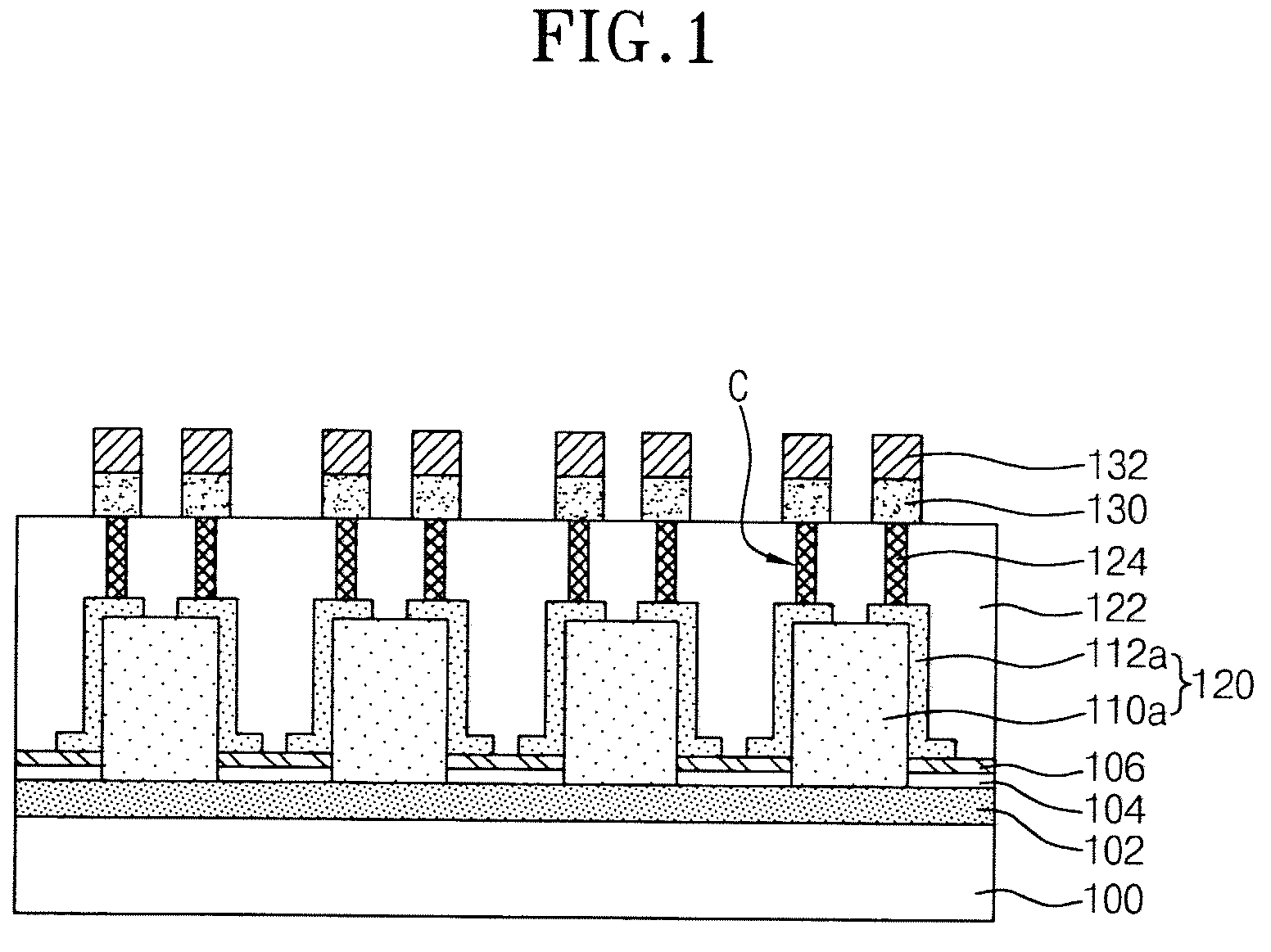

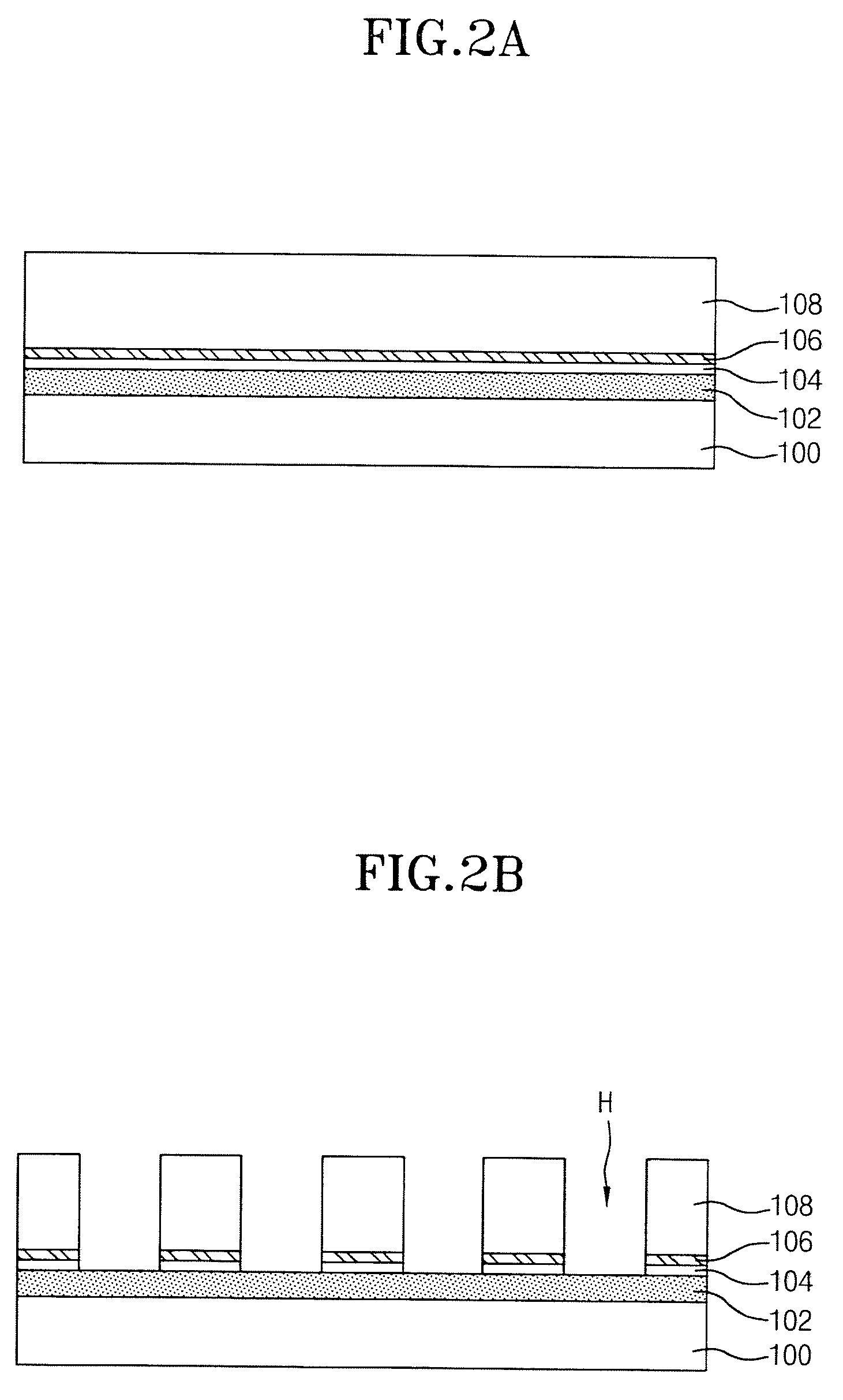

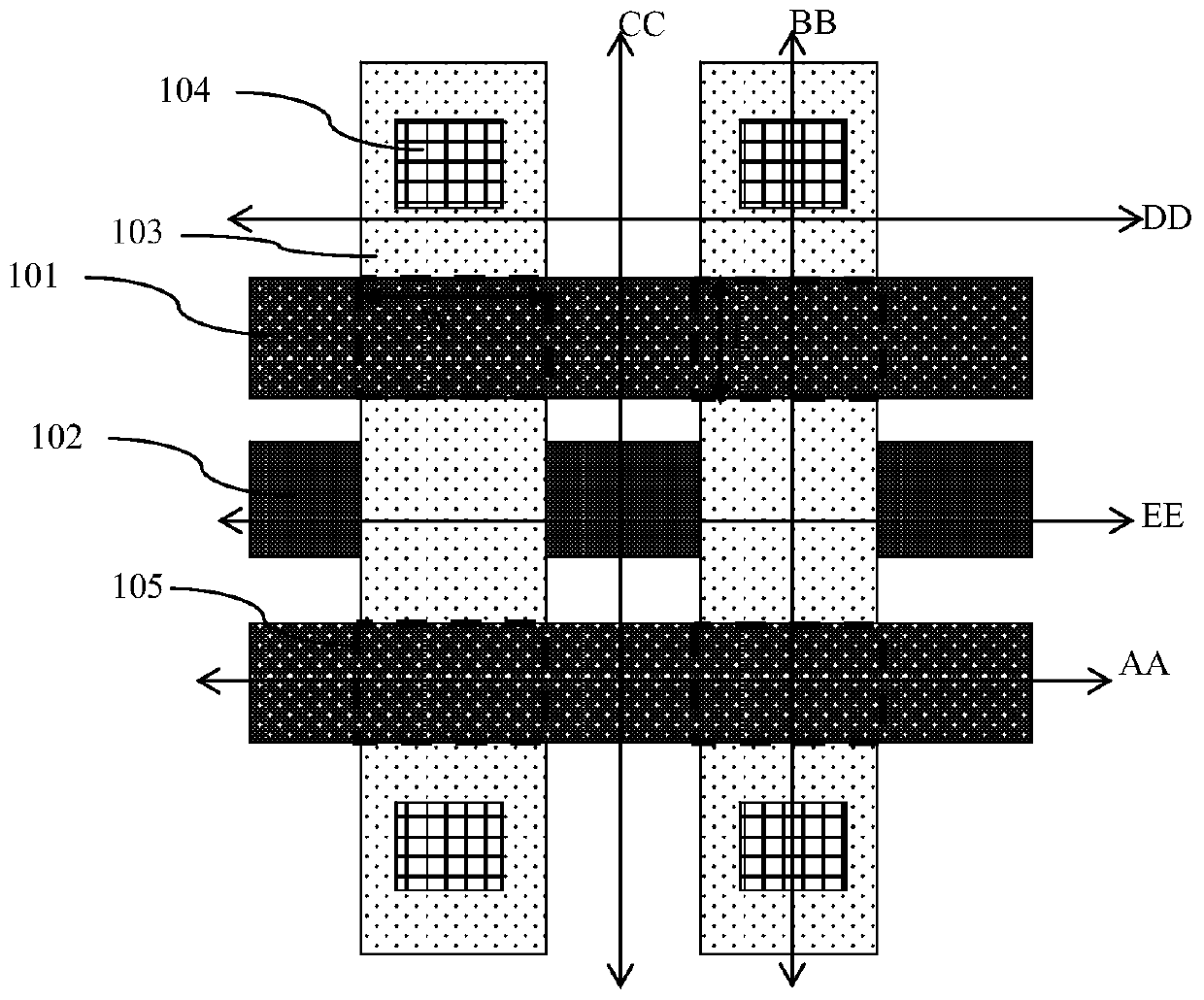

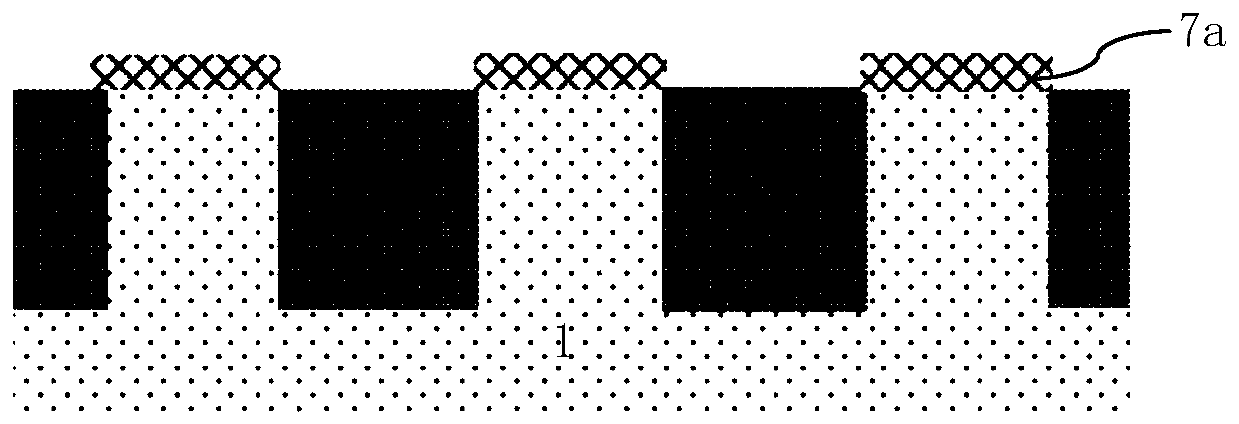

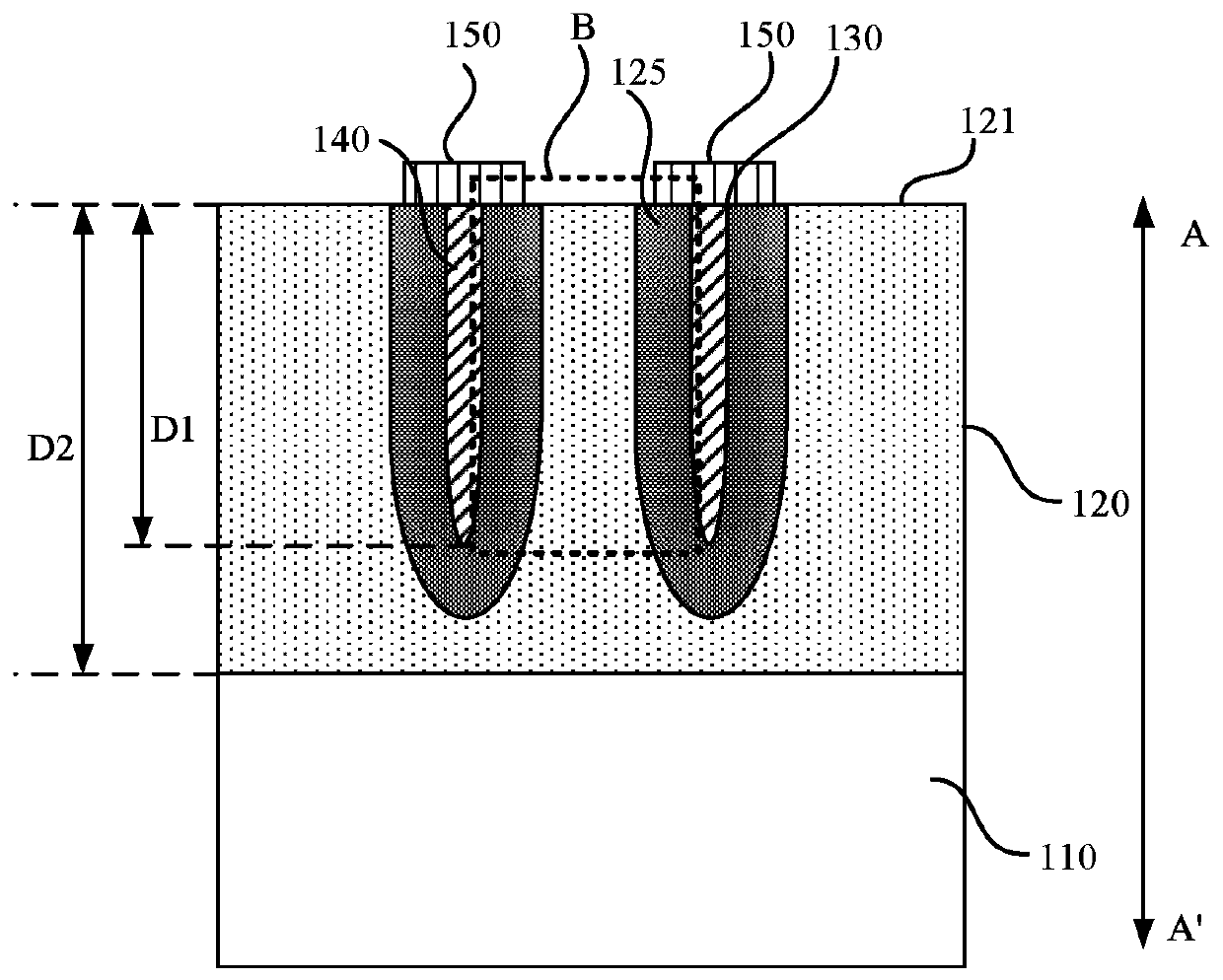

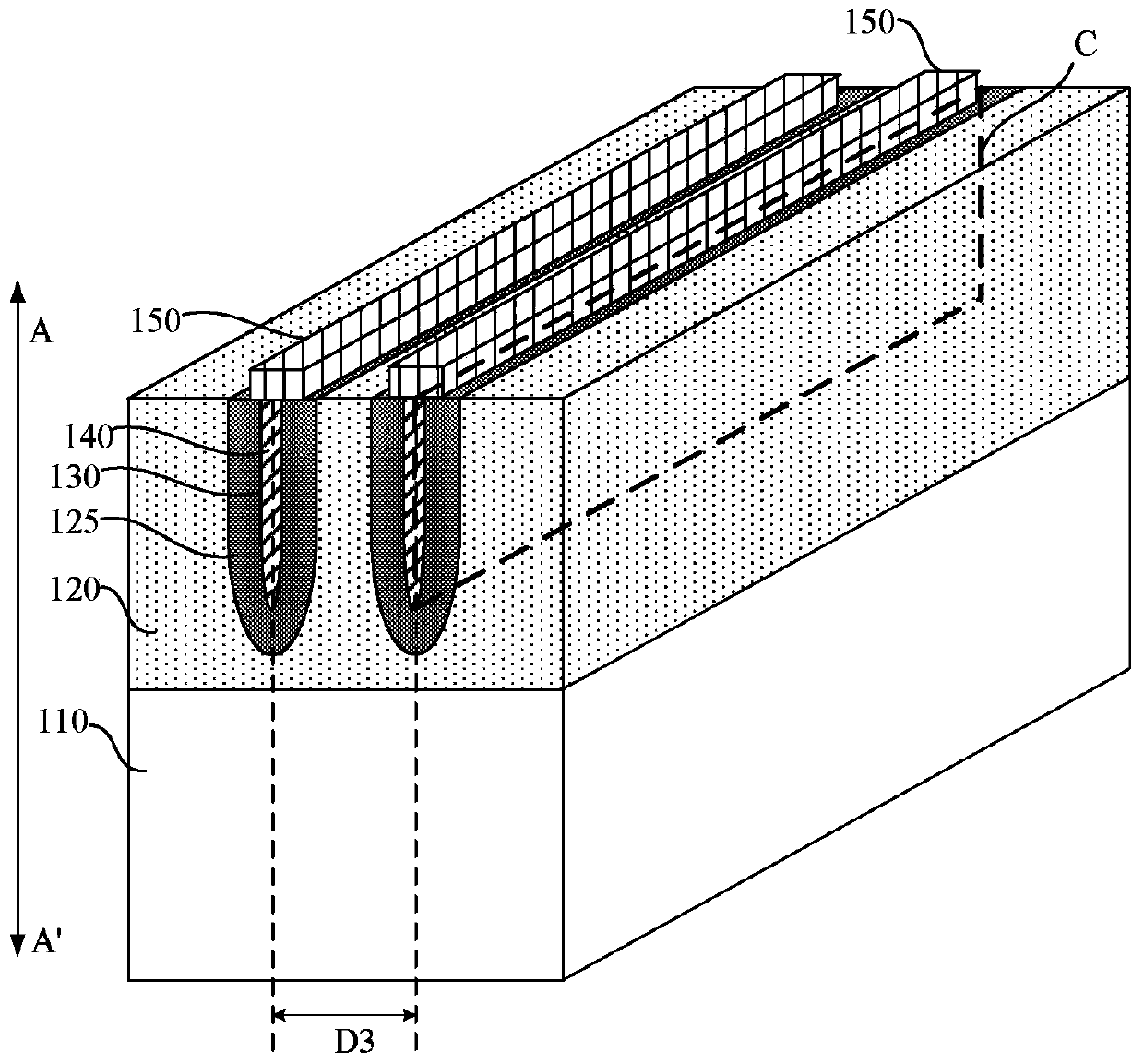

High level integration phase change memory device having an increased diode junction area and method for manufacturing the same

ActiveUS7843037B2Increase junction areaIncrease currentSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memorySilicon

A phase change memory device includes a semiconductor substrate active region, a plurality of first conductivity type silicon pillars, and a plurality of second conductivity type silicon patterns. The plurality of first conductivity type silicon pillars is formed on the semiconductor active region such that each first conductivity type silicon pillar is provided for two adjoining cells. The plurality of second conductivity type silicon patterns is formed on the plurality of first conductivity type silicon pillars such that two second conductivity type silicon patterns are formed on opposite sidewalls of each first conductivity type silicon pillars. Two adjoining cells together share only one first conductivity type silicon pillar and each adjoining cell is connected to only one second conductivity type silicon pattern which constitutes a PN diode which serves as a single switching element for each corresponding cell.

Owner:SK HYNIX INC

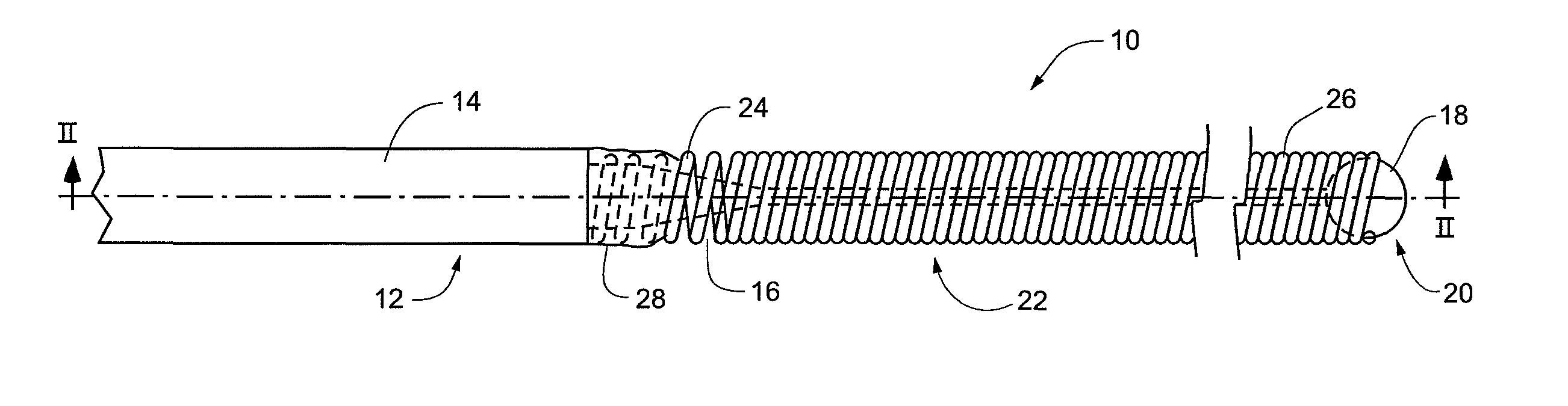

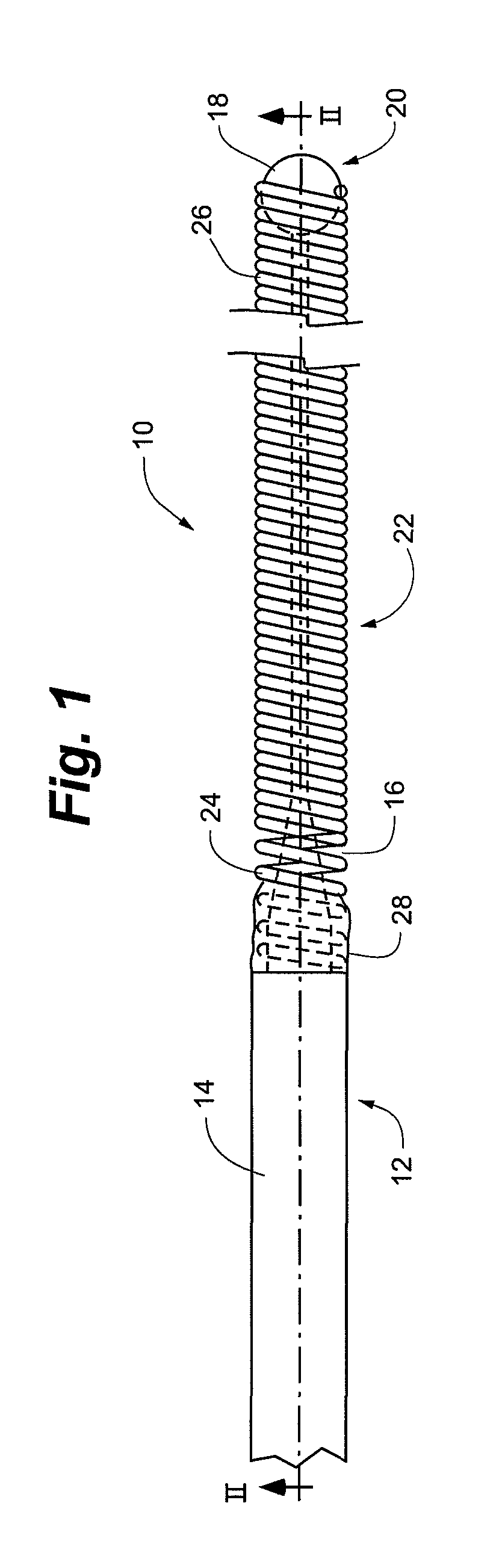

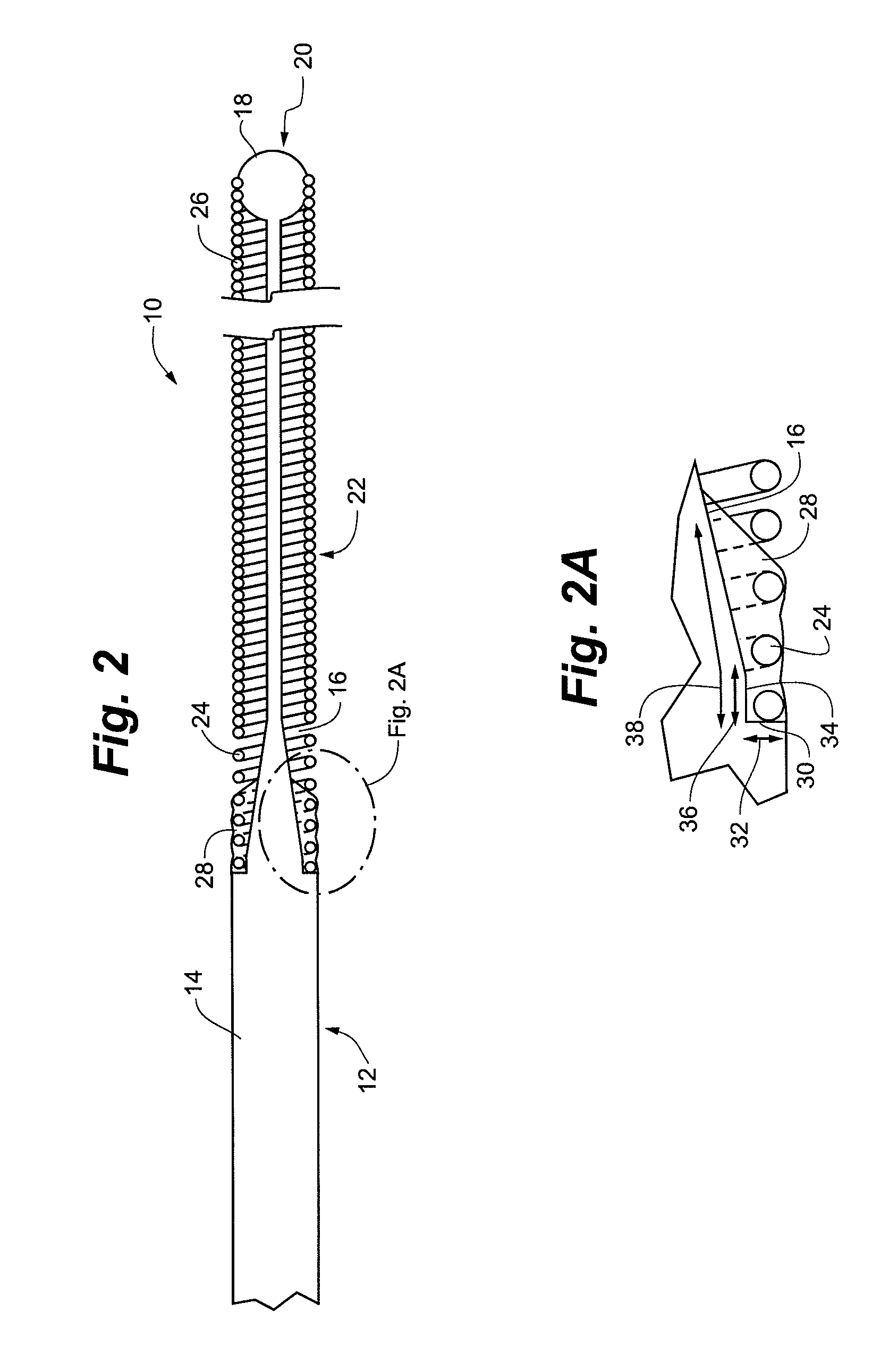

Medical guidewire

The guidewire provides a core and wire coil construction. The core can be shaped with a generally squared-off distally facing shoulder that forms a platform for a proximal end portion of the wire coil. The wire coil can have a plurality of spaced apart coil turns at its proximal end portion. A bonding agent comprising an adhesive can be used to secure the core to the wire coil proximal end portion.

Owner:HERAEUS MEDICAL COMPONENTS LLC

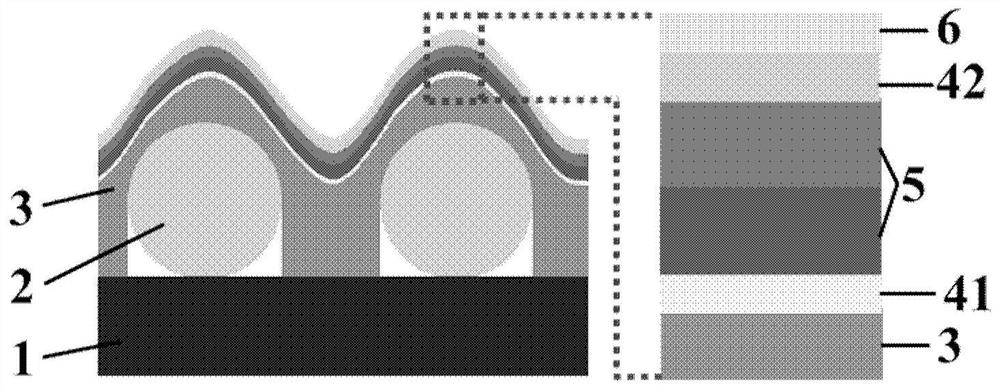

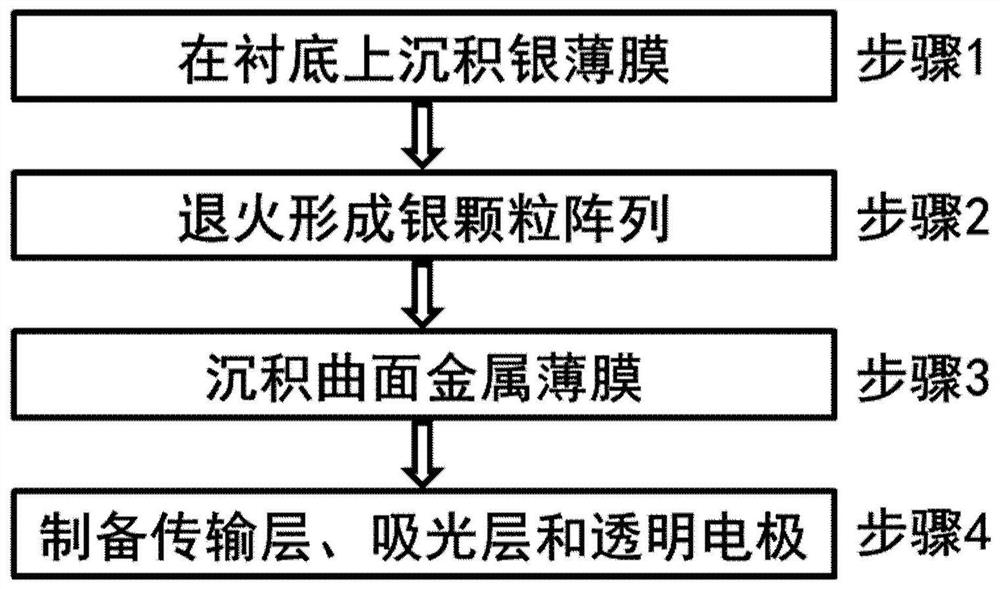

Curved heterojunction solar cell and manufacturing method thereof

PendingCN111952458AWith trapping effectImprove light absorption efficiencyFinal product manufactureSolid-state devicesHeterojunctionEngineering

The invention discloses a curved-surface heterojunction solar cell and a manufacturing method thereof. The curved-surface heterojunction solar cell comprises a substrate; a silver nanoparticle array arranged on the substrate; a curved surface metal film arranged on the silver nanoparticle array and serving as a light trapping structure and a charge collecting electrode; a first carrier transmission layer arranged on the curved surface metal film; a light absorbing layer disposed on the first carrier transport layer; a second carrier transport layer disposed on the light absorbing layer; and anelectrode disposed on the second carrier transport layer. The curved surface heterostructure has a light trapping effect, and the light absorption efficiency of the light absorption layer can be improved; compared with a sharp light trapping structure, the curved surface structure does not easily cause defects into the film; the curved surface structure is beneficial to reducing the thickness ofthe light absorption layer and increasing the interface area of the heterojunction, thereby improving the charge transmission efficiency.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Battery and method of manufacturing the same

InactiveUS20180123168A1Junction areaInterface resistance does not become problematicSolid electrolytesCell electrodesElectrolyteAnode

Owner:MURATA MFG CO LTD

High level integration phase change memory device having an increased diode junction area and method for manufacturing the same

ActiveUS20100117042A1Increase junction areaIncrease currentSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memorySilicon

A phase change memory device includes a semiconductor substrate active region, a plurality of first conductivity type silicon pillars, and a plurality of second conductivity type silicon patterns. The plurality of first conductivity type silicon pillars is formed on the semiconductor active region such that each first conductivity type silicon pillar is provided for two adjoining cells. The plurality of second conductivity type silicon patterns is formed on the plurality of first conductivity type silicon pillars such that two second conductivity type silicon patterns are formed on opposite sidewalls of each first conductivity type silicon pillars. Two adjoining cells together share only one first conductivity type silicon pillar and each adjoining cell is connected to only one second conductivity type silicon pattern which constitutes a PN diode which serves as a single switching element for each corresponding cell.

Owner:SK HYNIX INC

Semiconductor device using soi-substrate

ActiveUS20090152630A1Improve powerImprove pressure resistanceTransistorSolid-state devicesSoi substrateSilicon

According to a feature of the present invention, a semiconductor device includes a SOI substrate, including a semiconductor substrate; an insulating layer formed on the semiconductor substrate and a silicon layer formed on the insulating layer. A drain region and a source region are formed in the silicon layer so that the source region is in contact with the insulating layer but the drain region is not in contact with the insulating layer.

Owner:LAPIS SEMICON CO LTD

NOR flash memory and manufacture method thereof

ActiveCN109727983AIncrease junction areaImprove programming efficiencySolid-state devicesSemiconductor devicesEtchingPolycrystalline silicon

The invention discloses a NOR flash memory. In the flash cell array of the storage area of the NOR flash memory, active regions are in strip shapes and are arranged in parallel. The polycrystalline silicon of polycrystalline silicon control gates of the flash cells in the same row are connected together to form a polycrystalline silicon row. A polycrystalline silicon floating gate is on top of theactive region perpendicularly intersecting the polycrystalline silicon row and is isolated by a first gate oxide layer. A drain region comprises a self-aligned conformal injection region extending tothe sides of the active regions. The position of the self-aligned conformal injection region is defined by the self-aligned etched back field oxygen. The self-aligned etch back region of the field oxide is formed by the self-aligned definition of the gate structure and the active region after the gate structure etching. In the source region, a self-aligned conformal injection region is also superimposed. The invention also discloses a method for manufacturing a NOR flash memory. The NOR flash memory can improve the programming efficiency without changing the gate structure, and can also reduce electric leakage and improve the performance of the device.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Novel high-current-density fast recovery diode structure and manufacturing method thereof

ActiveCN104795450AIncrease junction areaIncrease current densitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh current densityEngineering

The invention discloses a novel high-current-density fast recovery diode structure and a manufacturing method thereof, is applicable to the production of large-current fast recovery diodes, and belongs to the field of semiconductor devices. The method is characterized in that the grooving technology is used, grooves are formed in the active area on the front side of a chip, groove intervals are correspondingly adjusted according to device performance parameters, boron-doped polycrystalline silicon is then used for deposition, and a device grooved anode area is formed through pushing; a method using vacuum platinum steaming before annealing is used on the back of a single chip, and good central fast recovery feature is achieved; a terminal area is consistent with a conventional device and adopts a field ring structure; compared with the prior art, the novel high-current-density fast recovery diode structure can evidently increase device current density in unit chip area and increase device current capacity; the device active area of devices with identical current indexes can be effectively reduced, wafer utilization rate is increased, and economic benefits are increased; the heavily-doped polycrystalline silicon can be in ohmic contact with an N-type chip, and device reliability is increased.

Owner:BEIJING MXTRONICS CORP +1

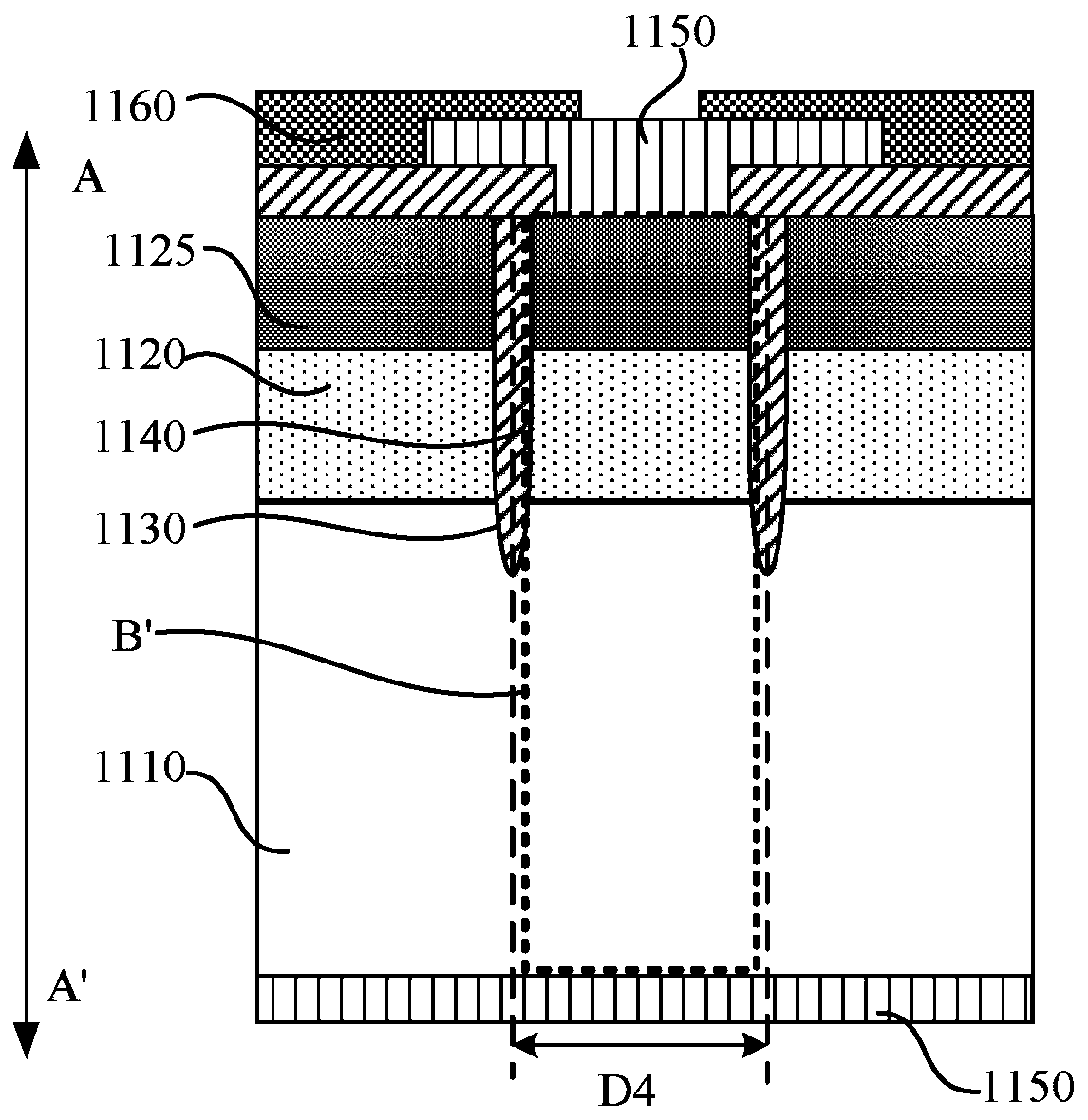

Bidirectional diode, manufacturing method thereof, and overvoltage protection device

PendingCN109950326AImprove flow capacityReduce volumeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The embodiment of the invention discloses a bidirectional diode, a manufacturing method thereof and an overvoltage protection device. The bidirectional diode comprises a semiconductor substrate, an epitaxial layer of a first conductivity type located on one side of the semiconductor substrate, at least two separated trenches at one side of the epitaxial layer away from the semiconductor substrate,diffusion regions which extend into the epitaxial layer along any trench and are in one-to-one correspondence with the trenches, conductive mediums arranged in the trenches, and two electrodes whichare electrically connected to the conductive mediums in the different trenches, wherein the depth of the trenches is smaller than the thickness of the epitaxial layer in a direction perpendicular to the semiconductor substrate, the conductivity type of the diffusion regions are a second conductivity type different from the first conductivity type, any two adjacent diffusion regions are separated by a portion of the epitaxial layer, the diffusion regions are separated from the semiconductor substrate by a portion of the epitaxial layer. The technical solution provided by the embodiment of the invention can improve the flow capacity of the device and reduce the volume of the device.

Owner:MAANSHAN BENCENT ELECTRONICS CO LTD