NOR flash memory and manufacture method thereof

A manufacturing method and technology of flash memory, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of inability to eliminate the mutual interference of flash memory cells, increase the coupling of flash memory cells, and large floating gate area, so as to achieve a large erasing effect The effect of reading current, reducing resistance, and increasing junction area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] Manufacturing method of existing NOR flash memory:

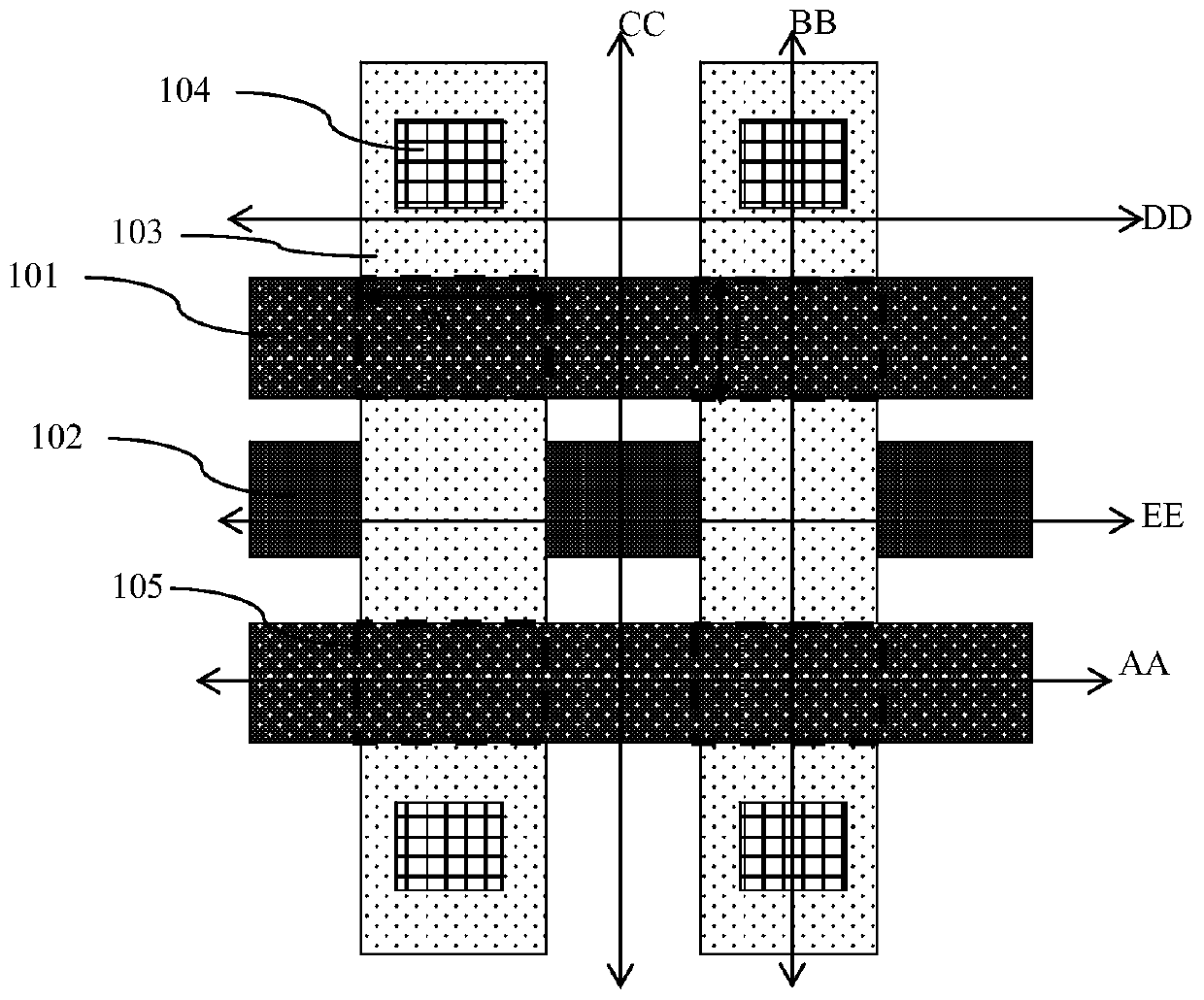

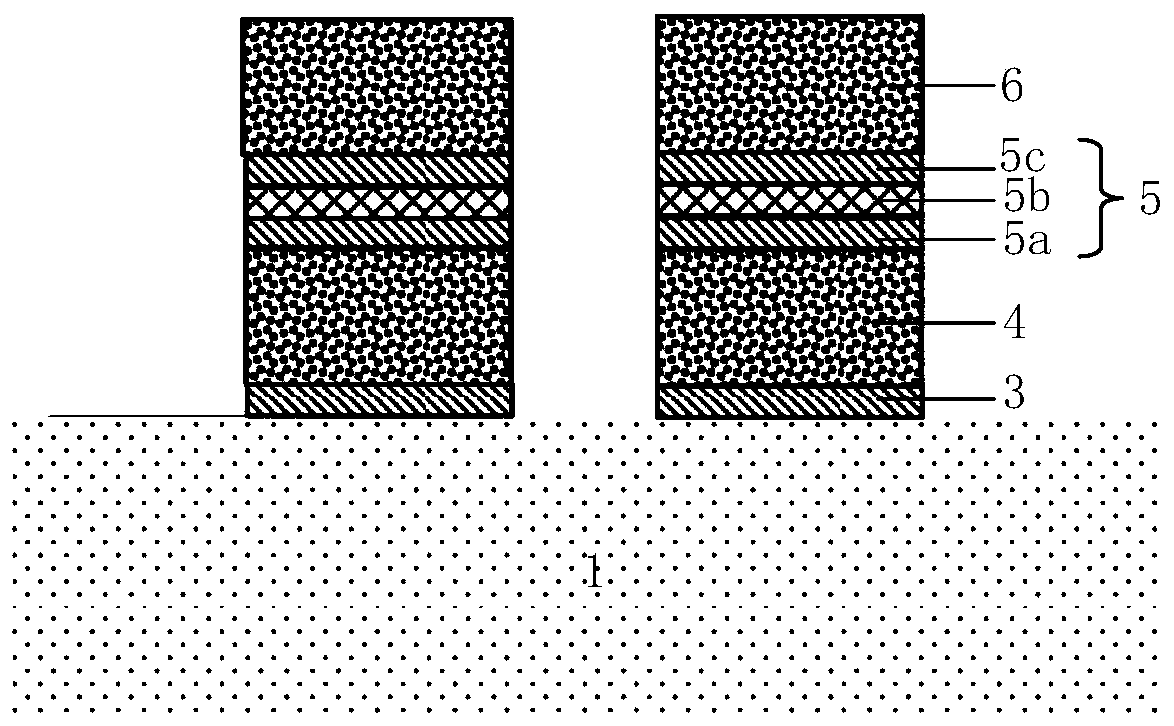

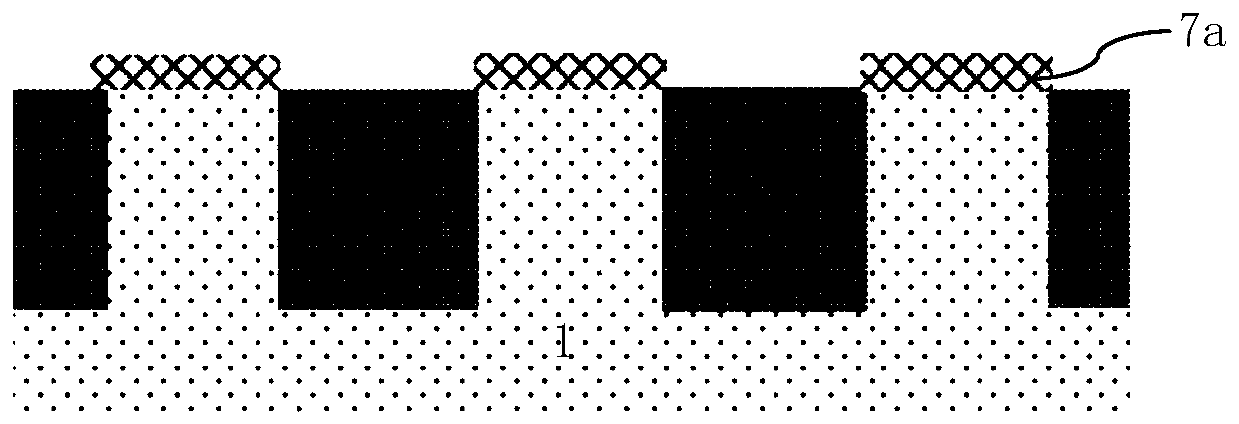

[0066] Such as figure 1 Shown is the layout structure of the storage area of the existing NOR flash memory; Figure 2A It is the trailing edge of gate structure formation in the existing NOR flash memory manufacturing method figure 1 Sectional view of line BB; Figure 2B It is the source-drain injection time edge in the existing NOR flash memory manufacturing method figure 1 Sectional view of line DD; Figure 2C It is the source-drain injection time edge in the existing NOR flash memory manufacturing method figure 1 The cross-sectional view of the EE line; the manufacturing method of the existing NOR flash memory comprises the following steps:

[0067] Step 1: providing a semiconductor substrate 1 , forming a field oxygen 2 in the semiconductor substrate 1 and isolating an active region 103 by the field oxygen 2 .

[0068] In the existing method, the semiconductor substrate 1 is a silicon substrate.

[0069] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More