Silicon wafer thinning fixture with through-hole electroplating copper salient points and thinning technique

A technology of through-hole electroplating and process method, which is applied in the manufacturing of circuits, electrical components, semiconductor/solid-state devices, etc., can solve problems such as cracks, wafer ruptures, stress concentration, etc., to achieve low cost, improve yield, and avoid stress concentration. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] Further illustrate this embodiment below in conjunction with accompanying drawing:

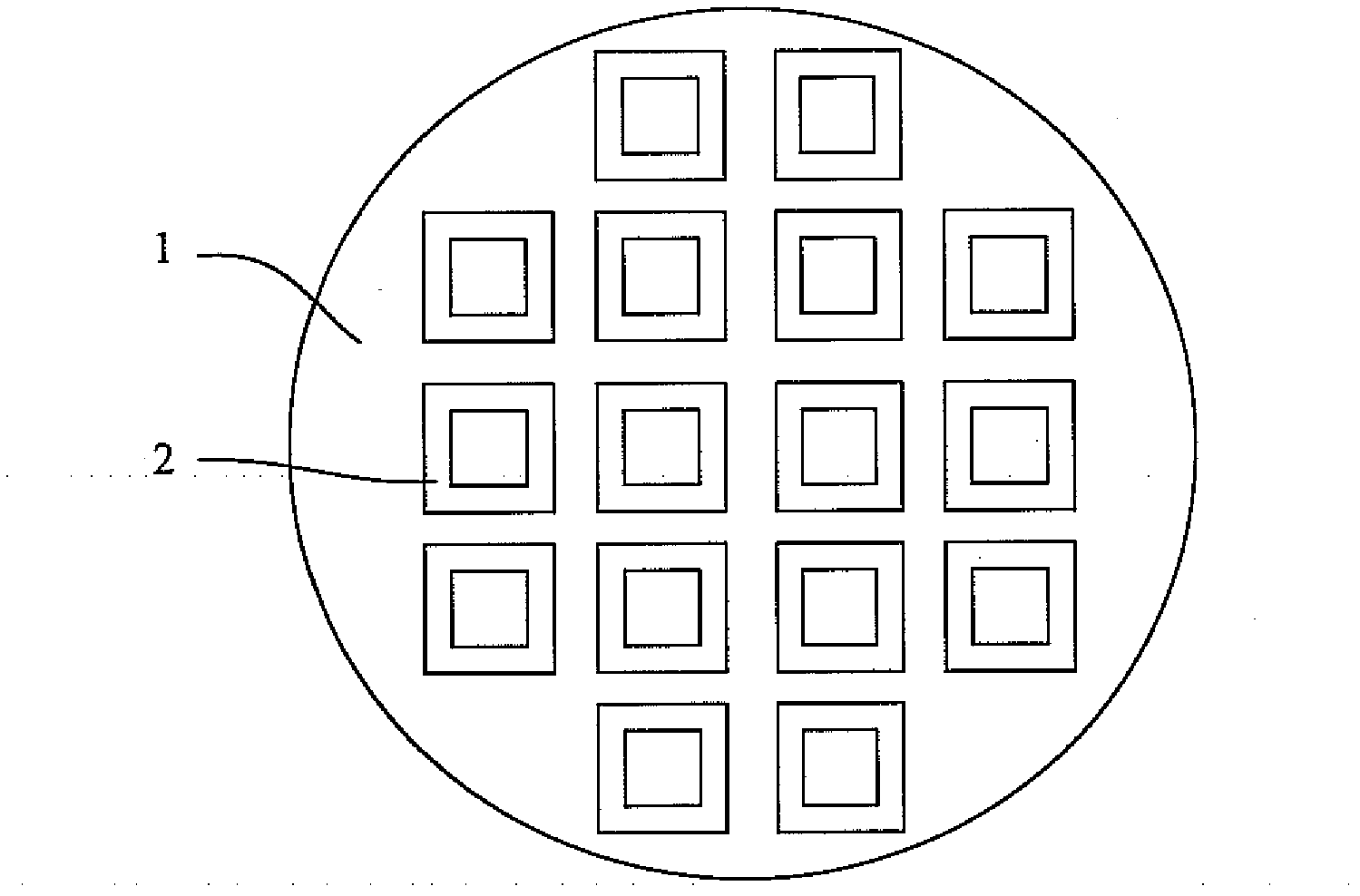

[0030] Referring to the figure, the jig wafer 1 is provided with a groove 2 capable of accommodating copper bumps 4 on the silicon wafer. The material of the jig wafer 1 is a silicon wafer or a metal wafer. Mark for fixture wafer 1 alignment.

[0031] The steps of the thinning process package in this embodiment are as follows:

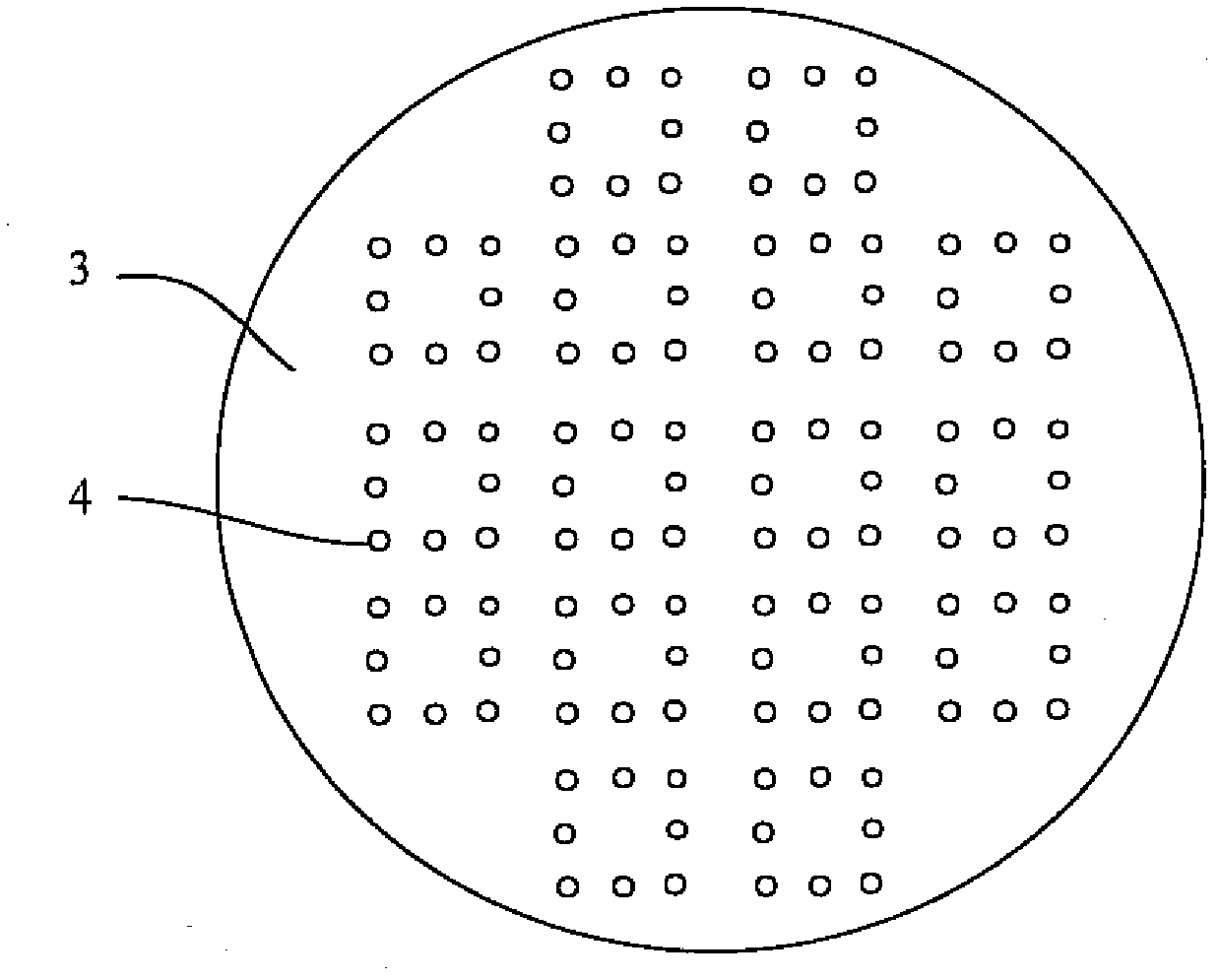

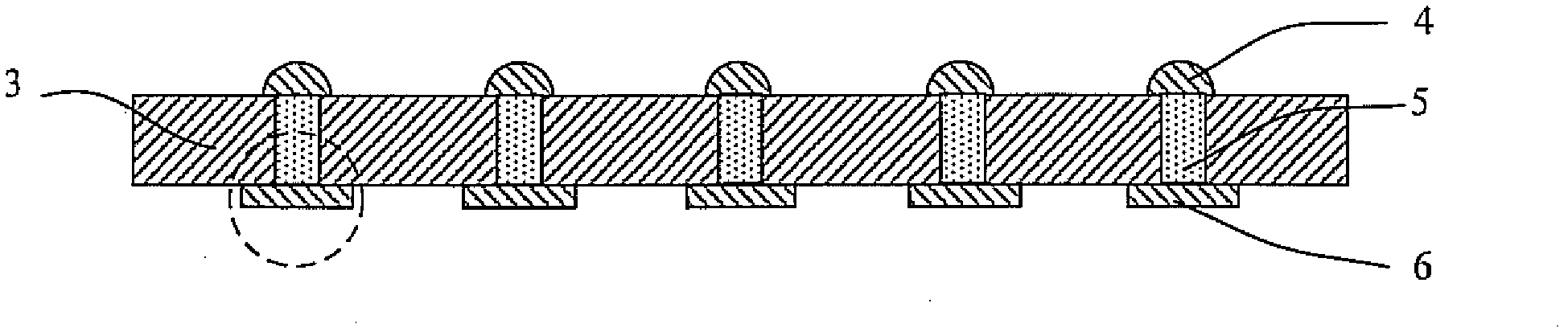

[0032] A. Electroplating the silicon wafer 3 with through holes. The through holes in the silicon wafer 3 are electroplated in a bottom-up manner. First, the back of the silicon wafer 3 is electroplated, and the through holes on the back are sealed. The sealing process can be partial The hole is sealed by electroplating, and the copper metal 6 filling the through hole is not formed on the back. Due to the influence of the electroplating process, local bumps are easily formed at the opening of the through hole, that is, the protrusion 7 produced by partially fil...

Embodiment 2

[0039] Embodiment 2 is the same as Embodiment 1, except that the fixing method of silicon wafer 3 and fixture wafer 1 is vacuum adsorption, and the silicon wafer 3 and fixture wafer are connected through the vacuum adsorption through hole 10 on the fixture circle 1. 1 fixed, such as Figure 6 shown.

Embodiment 3

[0041] Embodiment 3 is the same as Embodiment 1, except that the fixture disc 1 is made of stainless steel, and the fixture disc 1 is manufactured by machining. The shape of the groove 2 on the fixture disc 1, the processing methods include: corrosion, laser cutting, grinding, milling. In order to ensure the flatness of the fixture disc 1, the fixture disc 1 needs to be polished, such as figure 1 , figure 2 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com