Merging sort structure

A sequential logic and auxiliary controller technology, applied in the direction of concurrent instruction execution, machine execution devices, etc., can solve problems such as memory occupation, achieve stable operation, maximize resources, and achieve the effects of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

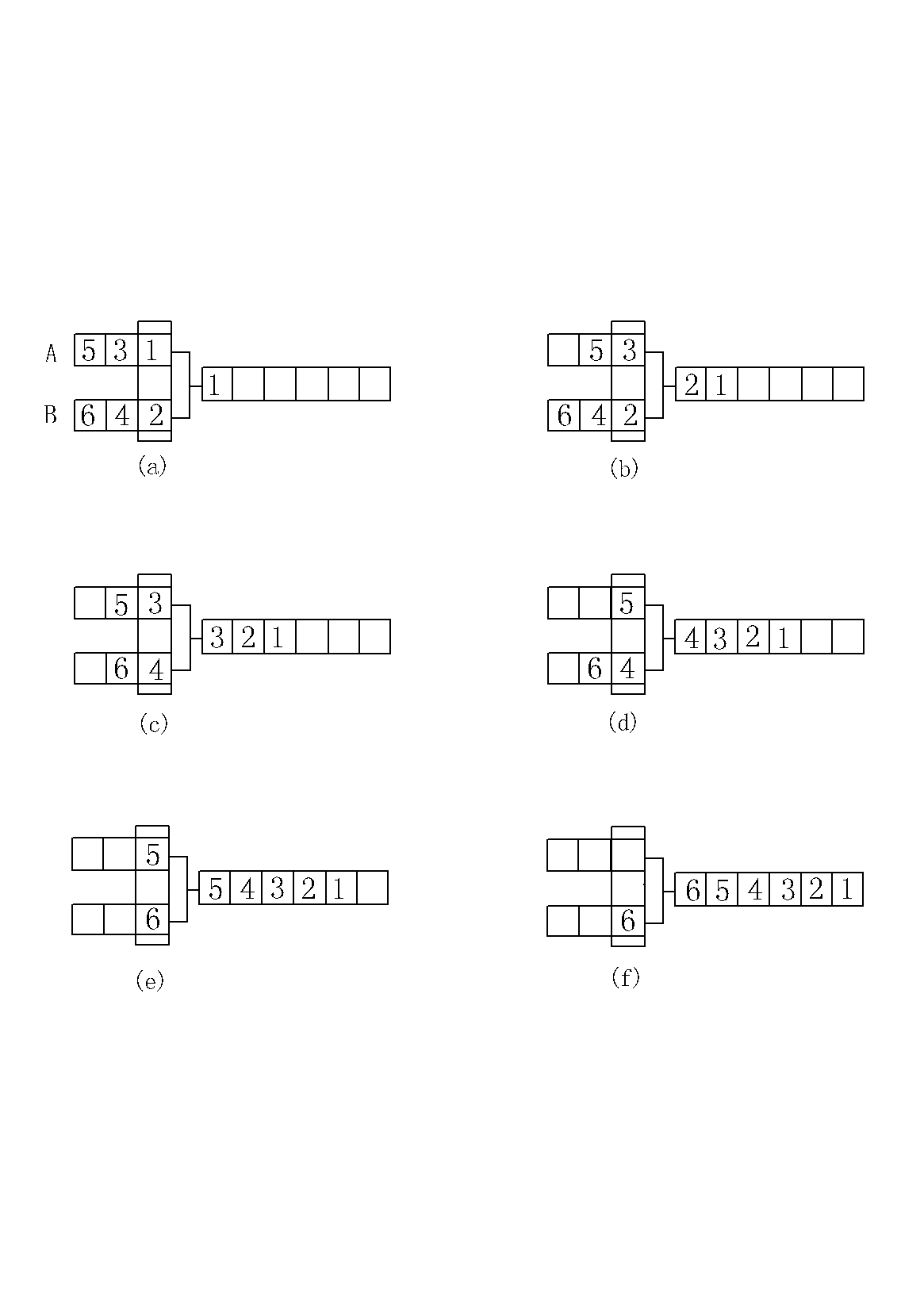

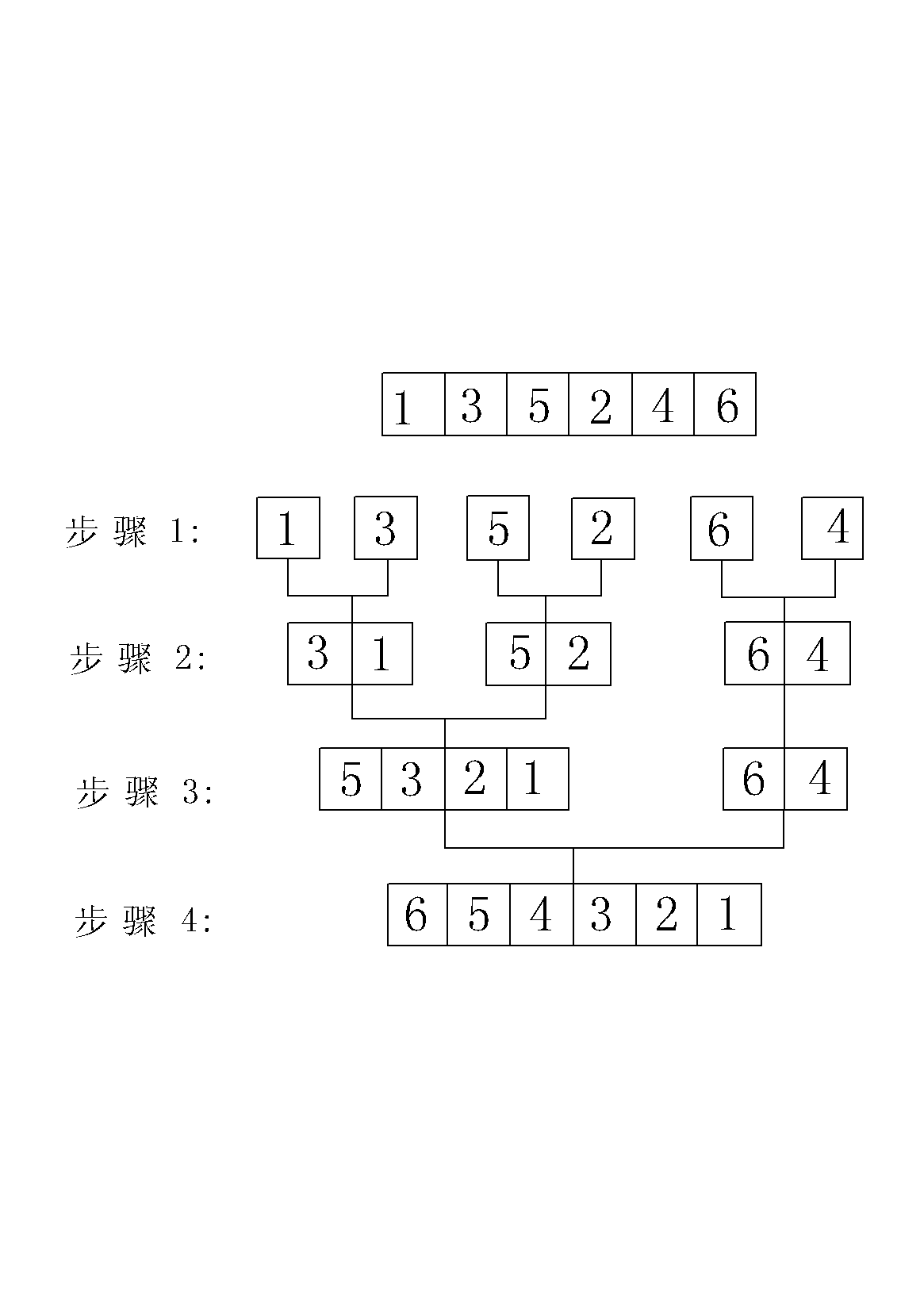

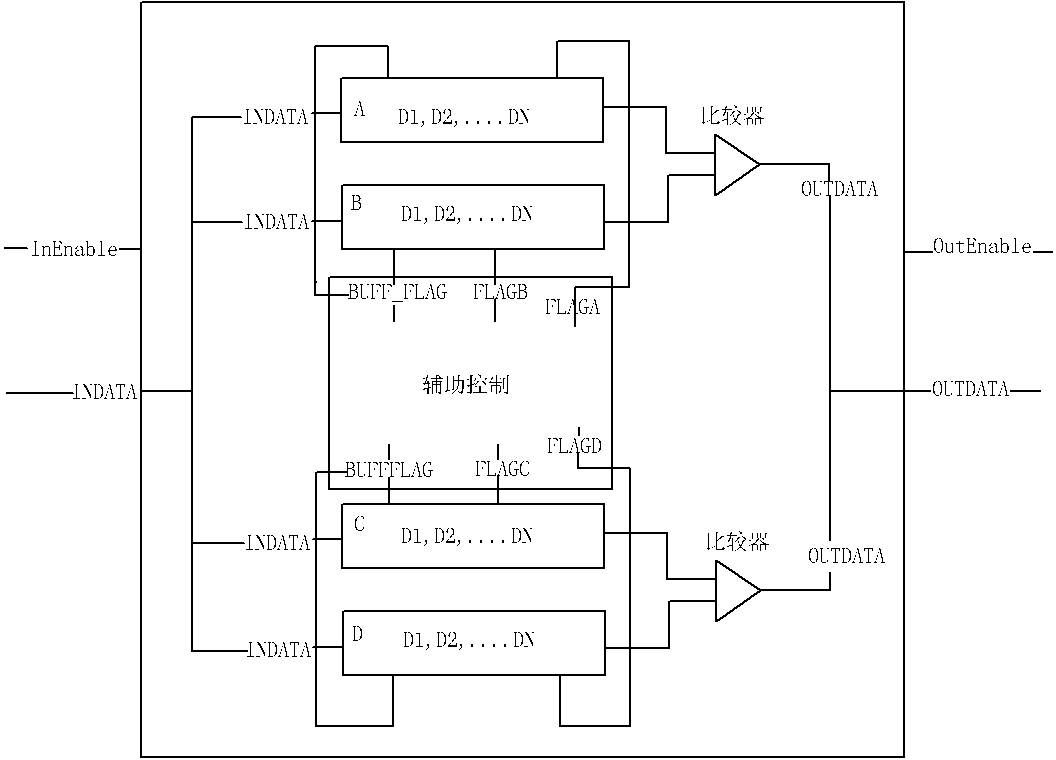

[0029] See image 3 As shown, it is a merge operation based on registers. Its hardware structure: the stored queue includes two queue registers, the two queue registers are connected to the comparator, and the two queue registers are respectively connected to the auxiliary controller. The comparator is triggered by a rising edge, and the auxiliary control The register is set with a counter that counts the dequeue or enqueue of each queue register; queue: the queue length is N: N registers D1, D2... DN, where D1 is the head of the queue, and DN is the tail of the queue; comparator: sorted data Bit n bits, using n-bit comparators, triggered by rising edges; Auxiliary controller: each queue has a flag bit FLAG, which is counted by a flag bit FLAG, initially 0, when entering the queue, the flag is increased by one, and when leaving the queue The time mark is reduced by one, and one group of queues (two) has a group flag bit BUFFFLAG, which is used to judge the input and output swi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More