P-type silicon substrate heterojunction cell

A heterojunction cell and silicon substrate technology, applied in the field of solar cells, can solve the problems of reduced light energy conversion efficiency, ineffective carrier collection, reduced transition tunneling probability, etc., and achieves increased processes, increased costs, and increased The effect of collection and utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the content of the present invention easier to understand clearly, the present invention will be described in further detail below according to specific embodiments in conjunction with the accompanying drawings,

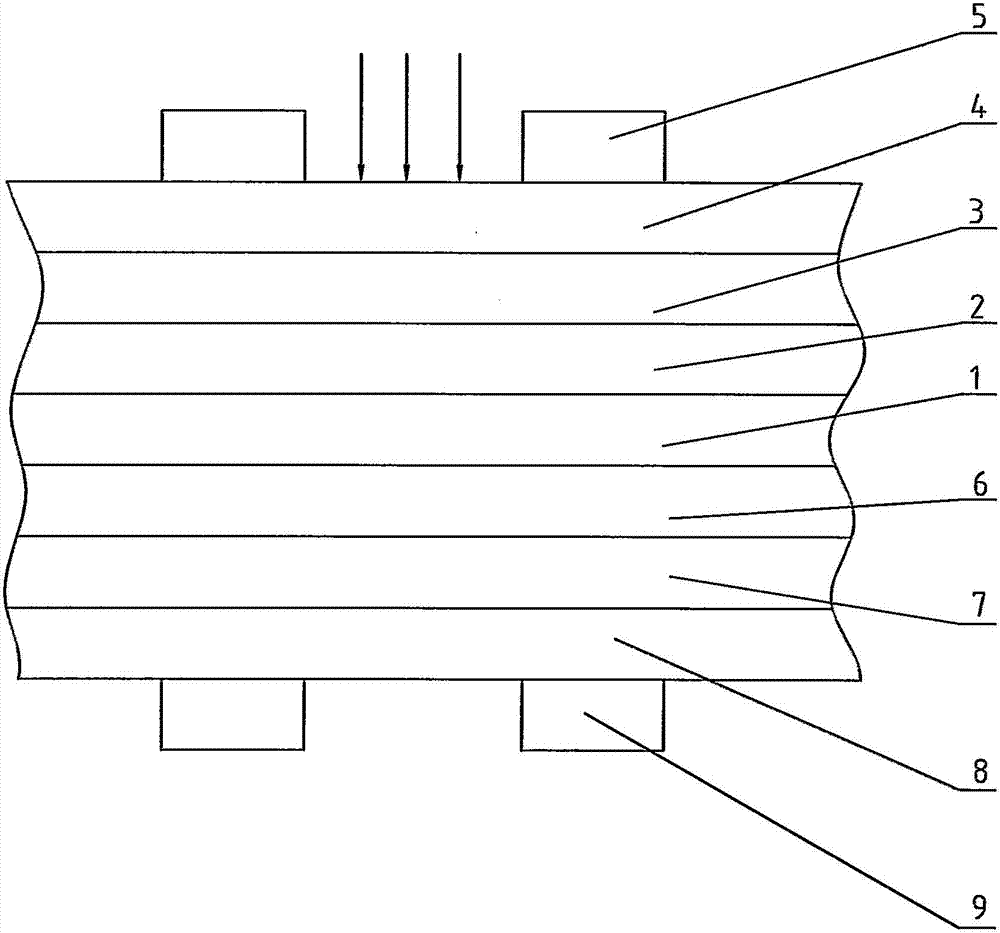

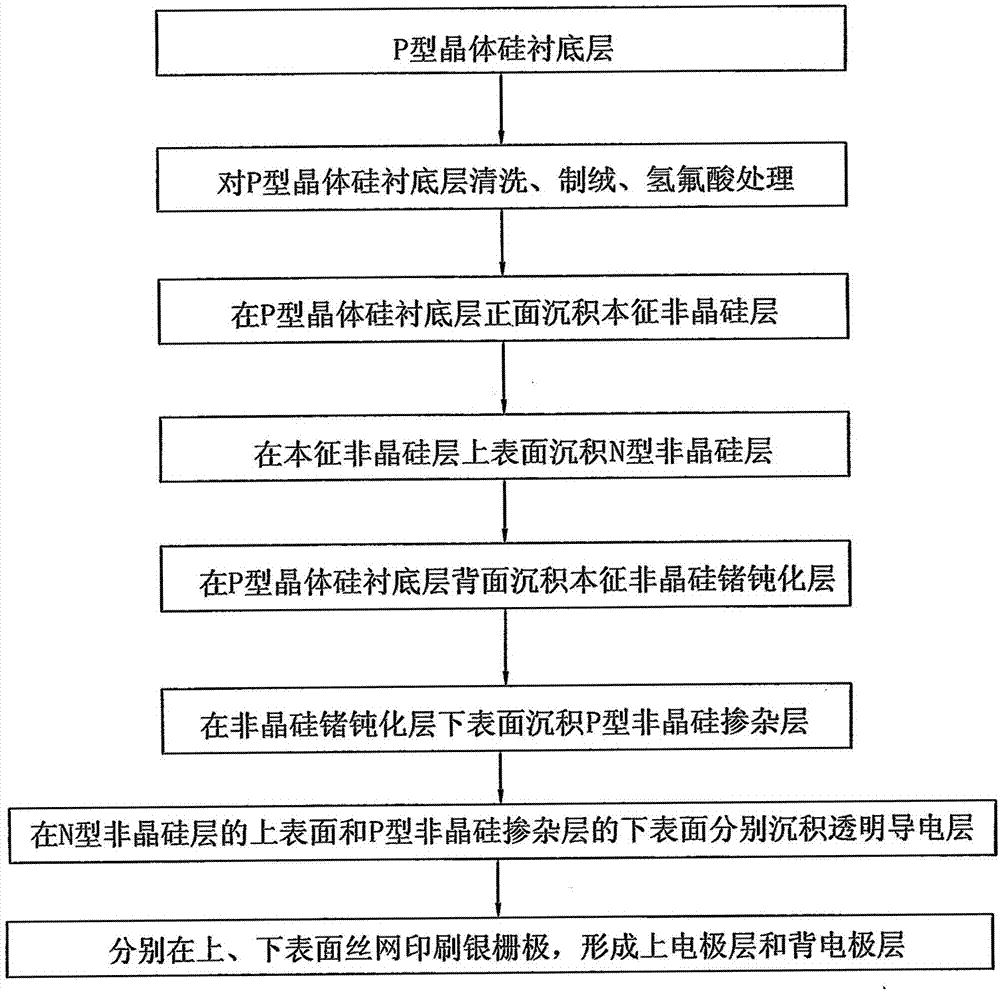

[0020] Such as figure 1 As shown, a P-type silicon substrate heterojunction cell comprises a P-type crystalline silicon substrate layer 1, an intrinsic amorphous silicon layer 2, an N-type amorphous silicon layer 3, and a P-type amorphous silicon layer. Doped layer 7, a first transparent conductive layer 4, an upper electrode layer 5, an intrinsic amorphous silicon germanium passivation layer 6, a second transparent conductive layer 8 and a back electrode layer 9, P-type crystalline silicon lining The bottom layer 1 has a front side and a back side, the intrinsic amorphous silicon layer 2 is deposited on the front side of the P-type crystalline silicon substrate layer 1; the N-type amorphous silicon layer 3 is deposited on the upper surface of...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More