High speed 1553 bus protocol processor

A bus protocol and processor technology, which is applied in the field of computer communication, can solve problems such as undiscovered product descriptions, and achieve the effects of time determination, efficient CPU interface, and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

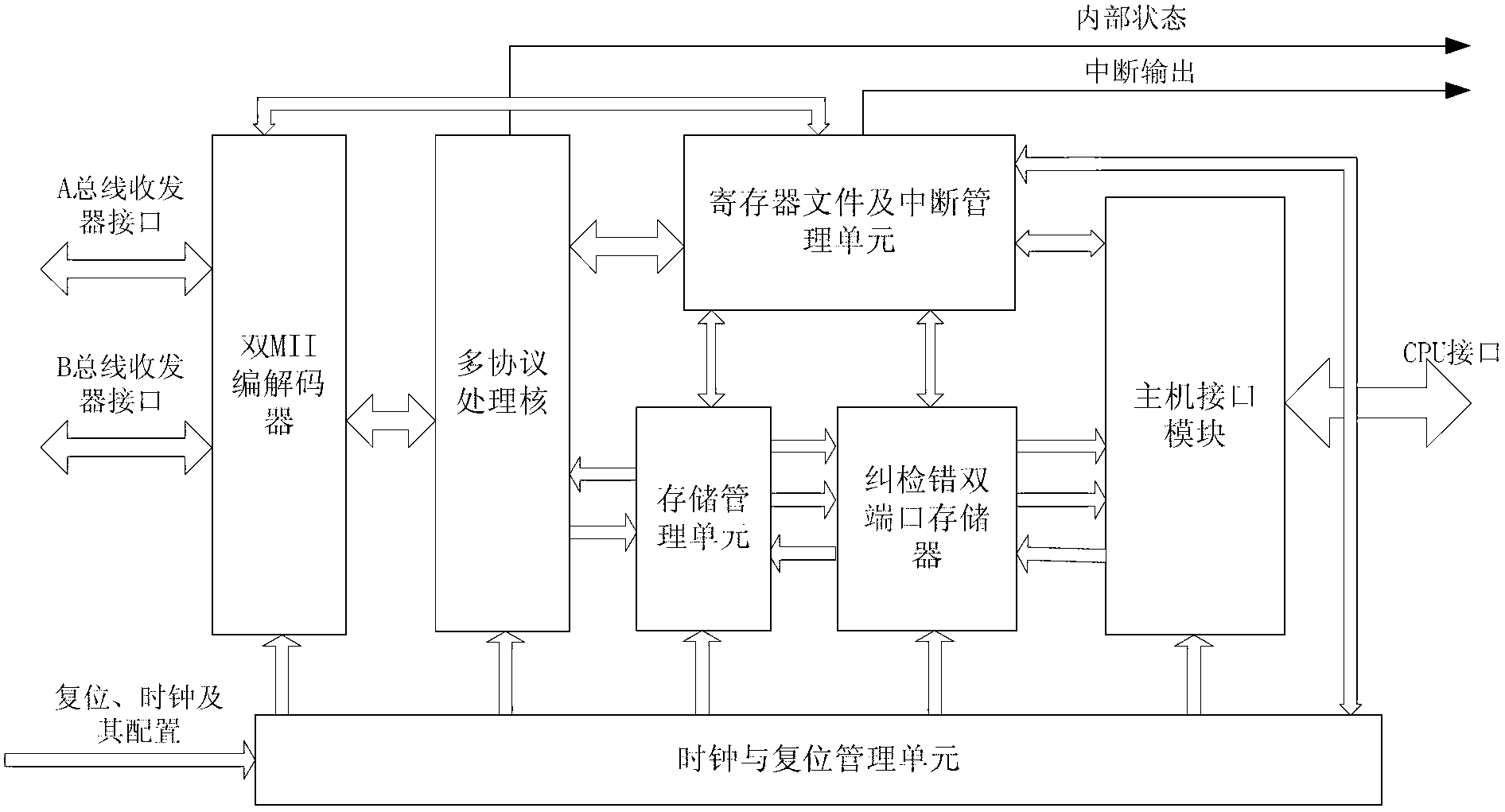

[0046] see figure 1 , a high-speed 1553 bus protocol processor, which mainly contains seven modules (parts):

[0047] The host interface module is respectively connected with the register file, the interrupt management unit, and the error correction and detection dual-port memory, and handles the data conversion between the host and the register and memory in the processor;

[0048] The error correction and detection dual-port memory is respectively connected with the storage management unit, the register file and the interrupt management unit; it includes two error correction and detection codec modules, one of which is responsible for the encoding and decoding of the host access memory port, and the other is responsible for the multi-protocol core Encoding and decoding of access memory por...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More