On-chip ferrite bead inductor

A ferrite bead, inductor technology, applied in inductors, electro-solid devices, semiconductor devices, etc., can solve the problems of integration incompatibility, consumption of substrate surface, large form factor, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

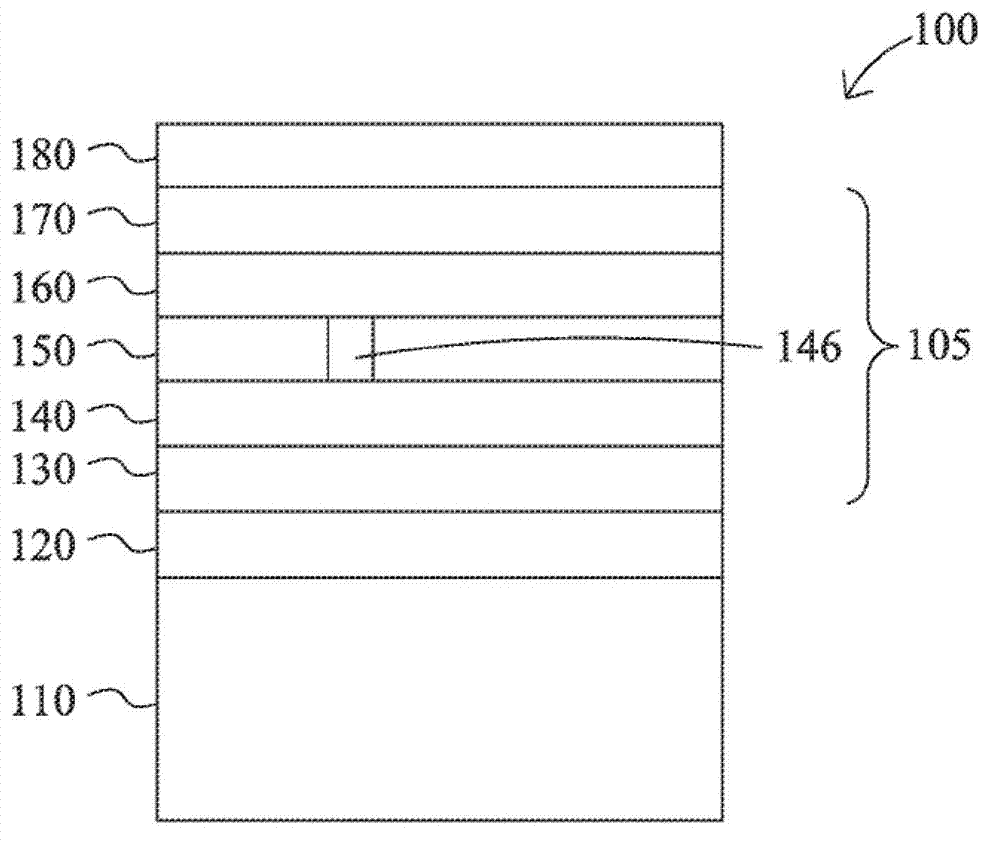

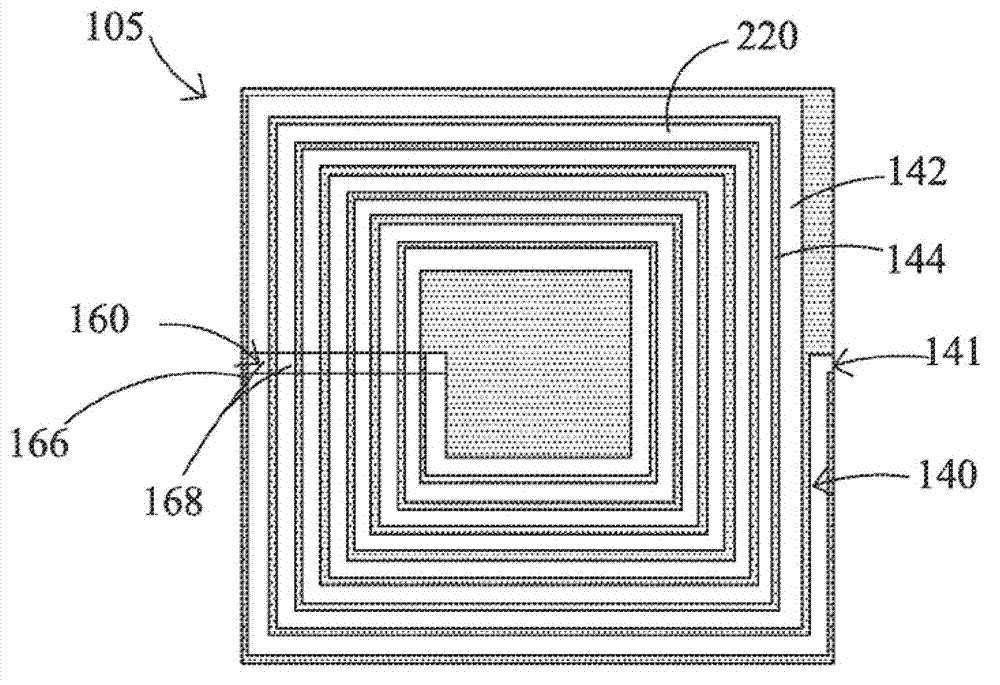

[0034] expected combination Figure 1 This description of exemplary embodiments should be read in conjunction with the accompanying drawings, which are considered a part of the entire written description. In the description of the embodiments disclosed herein, any reference to direction or orientation is intended for convenience of description purposes only and is not intended to limit the scope of the invention in any way. Relative terms such as "lower", "upper", "horizontal", "vertical", "above", "below", "upward", "downward", "top" and "bottom" and their derivatives (e.g., "Horizontally", "downwardly", "upwardly", etc.) should be construed to mean an orientation as described subsequently or as shown in the drawings in the discussion. These relative terms are for convenience of description only and do not require that the device be constructed or operated in a particular orientation. Unless expressly stated otherwise, terms relating to joining, connecting, etc. (such as "c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More