Automatic testability design system and automatic testability design method for electronic design interchange format (EDIF) netlist-level circuit based on practical extraction and reporting language (Perl)

A design method and design system technology, applied in the field of automatic testability design system, can solve the problems such as inconvenient reading and modification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

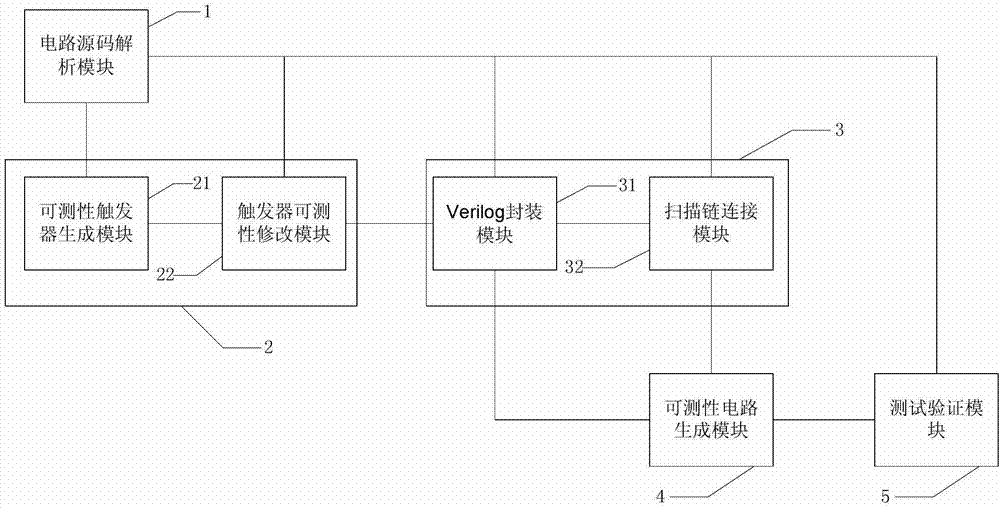

[0046] Specific implementation mode 1. Combination figure 1 Describe this specific embodiment, the automatic testability design system based on the EDIF netlist level circuit of Perl, it comprises circuit source code parsing module 1, flip-flop modification module 2, scan chain design module 3, testability circuit generation module 4, Test verification module 5;

[0047] The circuit source code analysis module 1 is used to analyze the EDIF netlist-level description of the digital logic circuit, and obtain the information used by all flip-flops in the circuit;

[0048] The trigger modification module 2 includes a testability trigger generation module 21 and a trigger testability modification module 22;

[0049] The trigger modification module 2 is used to complete the testability modification of all triggers in the EDIF netlist description file of the circuit according to the trigger information provided by the circuit source code analysis module;

[0050] The scan chain desi...

specific Embodiment approach 2

[0055] Embodiment 2. The difference between this embodiment and the automatic testability design system based on Perl-based EDIF netlist level circuits described in Embodiment 1 is that the testability circuit generation module 4 obtains the final design for testability. The latter circuit shields all the internal information of the circuit to the outside, and only provides an interface in the form of a common hardware description language.

specific Embodiment approach 3

[0056] The specific embodiment three, the automatic testing method of the EDIF netlist level circuit based on Perl, it is realized by the following steps:

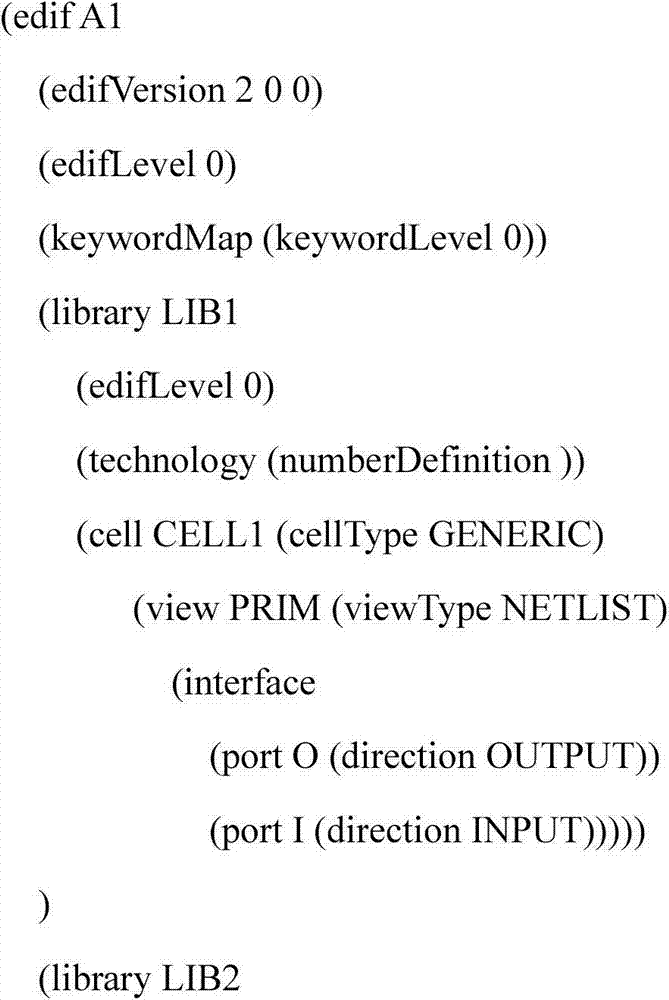

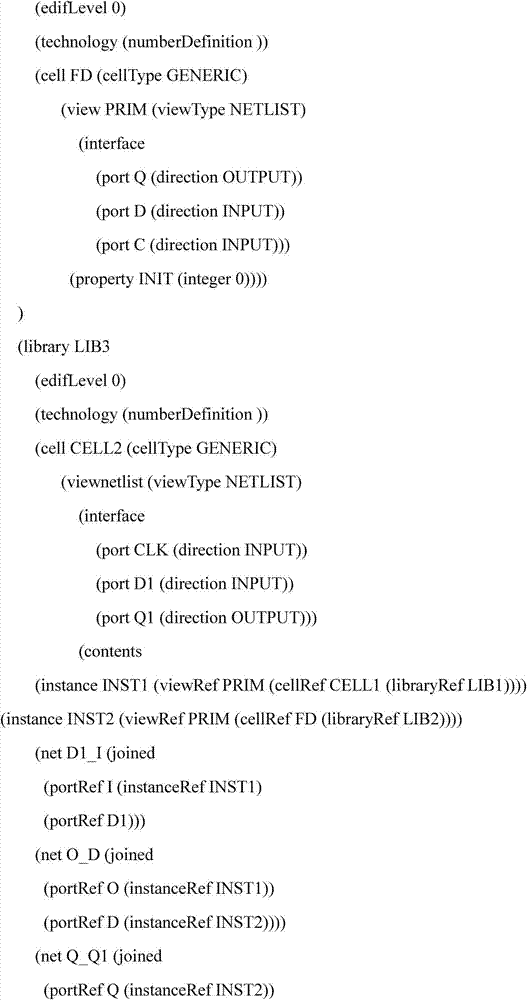

[0057] Step 1. Use the circuit source code analysis module 1 to analyze the triggers used in the circuit, and use Perl to process in the EDIF environment;

[0058] Step 2: Use the trigger modification module 2 to modify the trigger used in the circuit for testability, and use Perl to process it in the EDIF environment;

[0059] Step 3. Use Perl to perform Verilog encapsulation on the EDIF circuit after the testability modification of the flip-flop, shield the EDIF details, and then design the scan chain for the flip-flop with the testability modification in the circuit;

[0060] Step 4. Use Perl to give the final testable circuit that conforms to Verilog syntax, and after verifying that the modification is correct, use Perl to generate an automatic test file that conforms to Tel syntax, and then realize the automatic test ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More