Single event upset resisting reinforcing system and method used for FPGA (Field Programmable Gate Array)

An anti-single event and reloading technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of not being able to meet different needs, single interface mode, lack of portability, etc., to achieve enhanced applicability, The effect of enhancing operability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

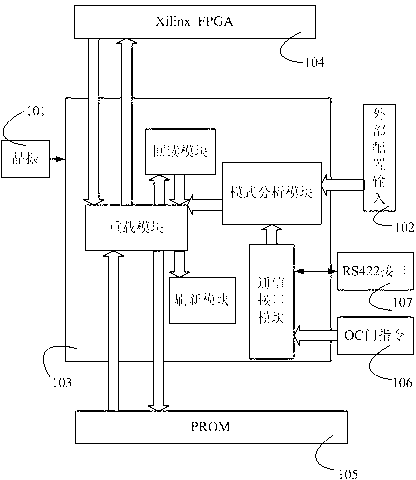

[0059] Such as figure 1 Shown is an embodiment of the present invention, and host computer is connected with communication interface module by serial port 107; The dedicated pin of Xilinx SRAM type FPGA 104 that the user selects is connected with readback refresh control device 103 according to different interface modes; Store FPGA configuration file The PROM 105 is also connected to the reload module, the readback module and the refresh module respectively according to different interface modes.

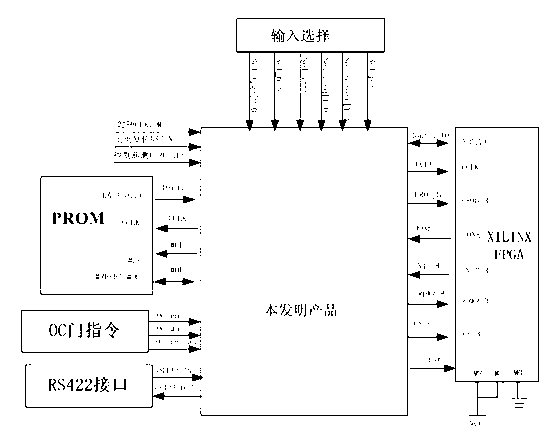

[0060] According to the external configuration 102 selected by the user, the FPGA device model, interface mode, readback refresh mode, power-on ban, readback cycle and readback overload threshold are determined. image 3 and Figure 4 Corresponding to the input selection signals Sel_fpga[2:0], Sel_intf, Sel_mode, Sel_per, Sel_freq[1:0], Sel_biterr[1:0], the operations corresponding to different values are shown in the table below.

[0061] Sel_fpga[2:0] is used to select the FPG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com