Fin field effect transistor and technology thereof

A technology of field-effect transistors and transistors, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve problems such as reduced component performance, increased gate dielectric layer thickness, and decreased gate capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

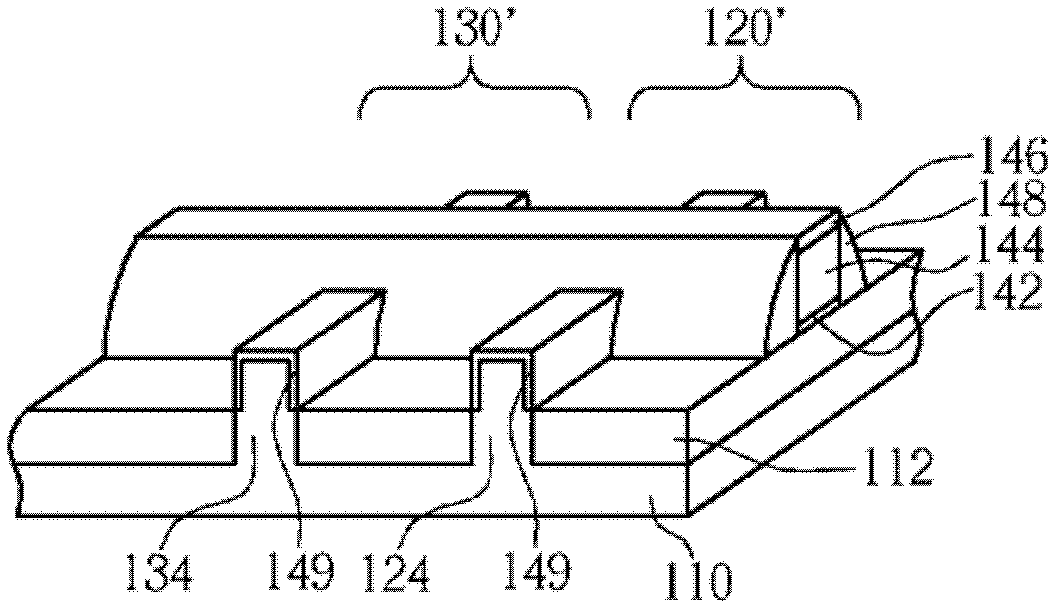

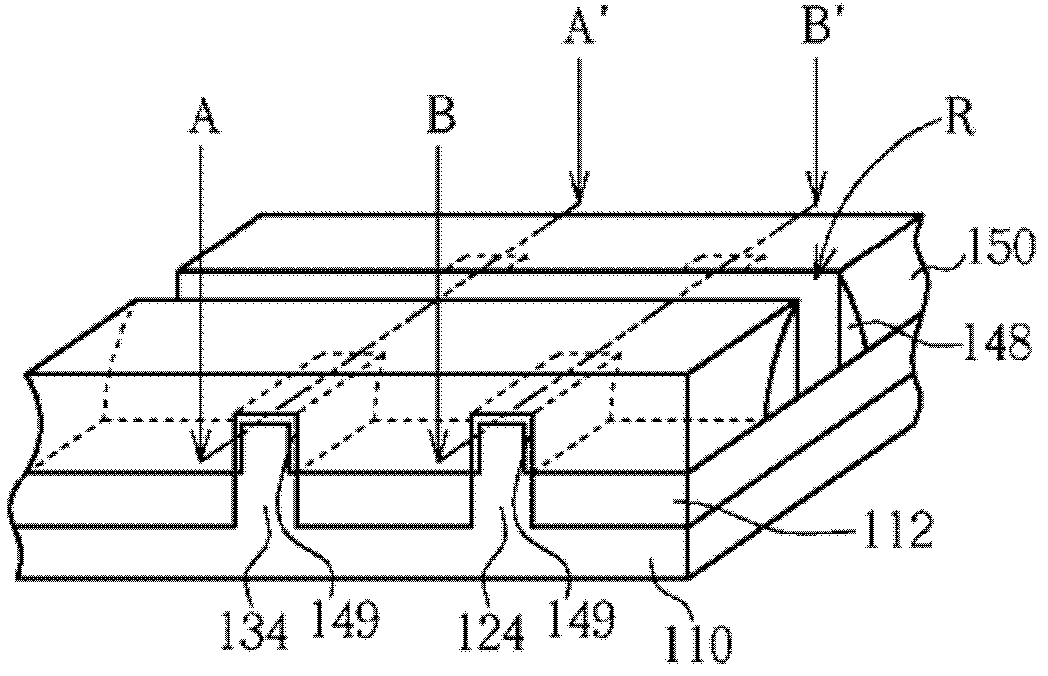

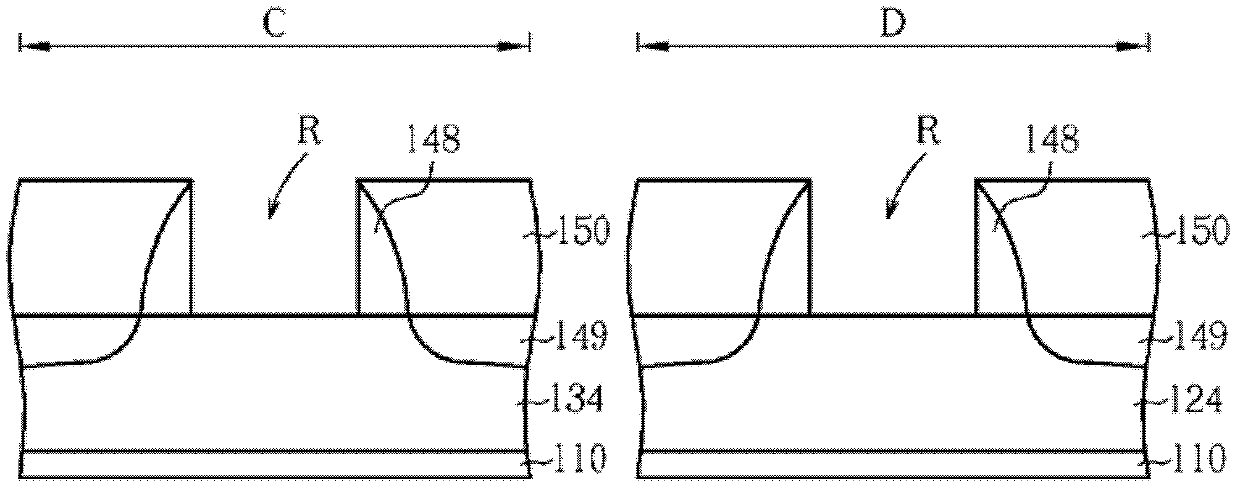

[0024] Figure 1-2 A three-dimensional view of a fin field effect transistor process according to an embodiment of the present invention is shown. Such as figure 1 As shown, first, a substrate 110 is provided. Then, the first FinFET 120' and the second FinFET 130' are formed on the substrate 110.

[0025] In detail, the method for forming the first FinFET 120' and the second FinFET 130' may include: providing a bulk substrate (not shown), forming a hard mask layer (not shown) thereon ), and pattern it to define the first fin structure 124 and the second fin field effect transistor 130' corresponding to the first fin field effect transistor 120' to be formed in the underlying bulk substrate The second fin structure 134 is located at the base 110 . Next, an etching process is performed to simultaneously form the first fin structure 124 and the second fin structure 134 on the substrate 110 in a bulk substrate (not shown). In this way, the fabrication of the first fin structu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More