Addressing and storage integrated two read one write memory controller

A storage controller and addressing technology, which is applied in the field of operation control circuit and timing control, can solve the problems of unfavorable execution instruction sequence speed, increasing the burden of microprocessor execution program instruction flow, and costing microprocessor clock pulse cycle, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

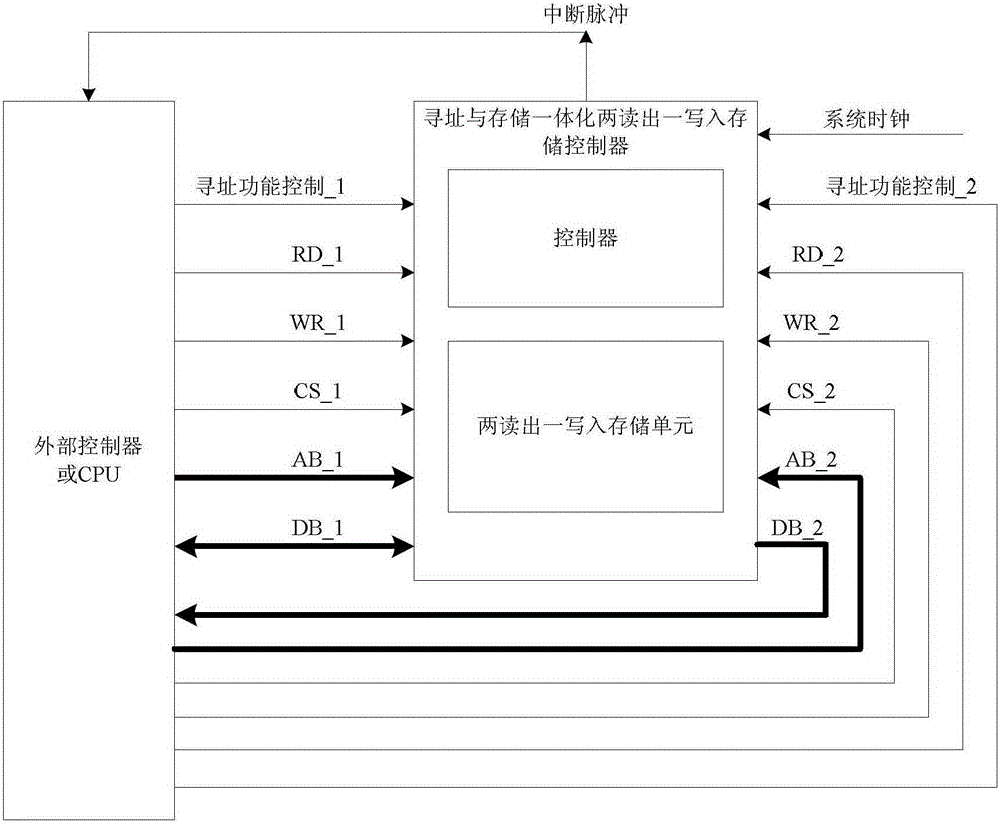

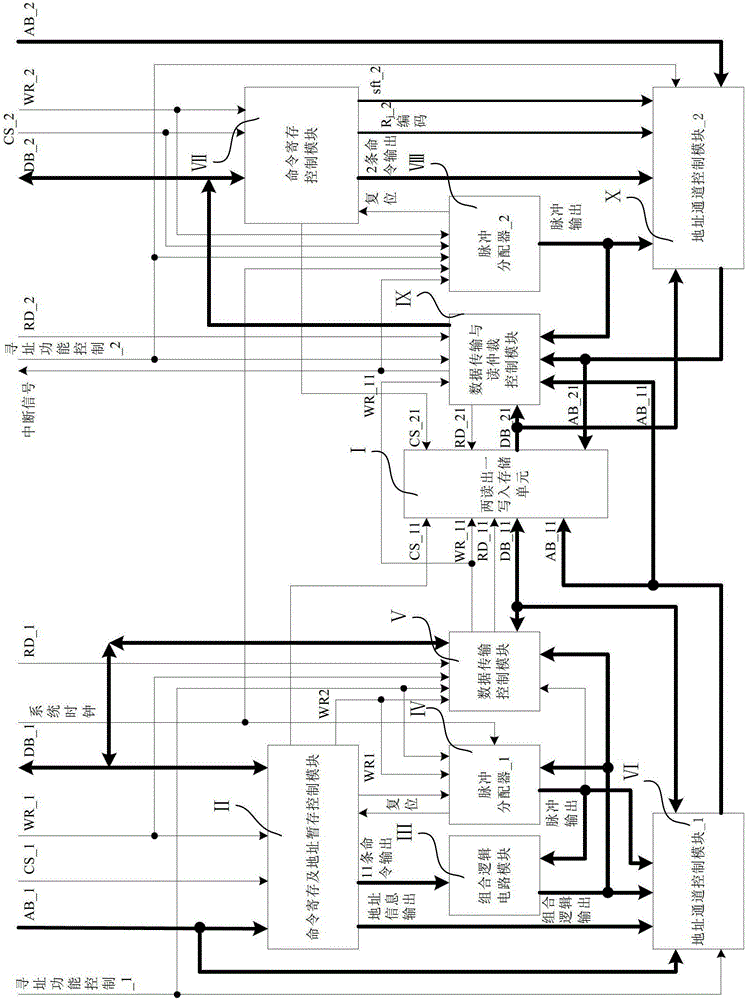

[0140] An addressing and storage integrated two-read one-write memory controller, such as image 3 As shown, the integrated two-read-one-write memory controller includes two read-one-write memory unit I, command register and address temporary storage control module II, combinational logic circuit module III, pulse distributor_1IV, data Transmission control module Ⅴ, address channel control module _1Ⅵ, command register control module Ⅶ, pulse distributor _2Ⅷ, data transmission and read arbitration control module Ⅸ and address channel control module _2Ⅹ;

[0141] The two read-one-write storage unit I, command register and address temporary storage control module II, data transmission control module V, address channel control module_1VI, command register control module VII, data transmission and read arbitration control module IX and Address channel control module_2X connection;

[0142] The command storage and address temporary storage control module II is also connected with t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More