Wafer-level bonding method for three-dimensional integrated packaging technology

A three-dimensional integration, wafer-level technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of insufficient density of the oxide layer, oxide layer on the bonding interface, uneven surface, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

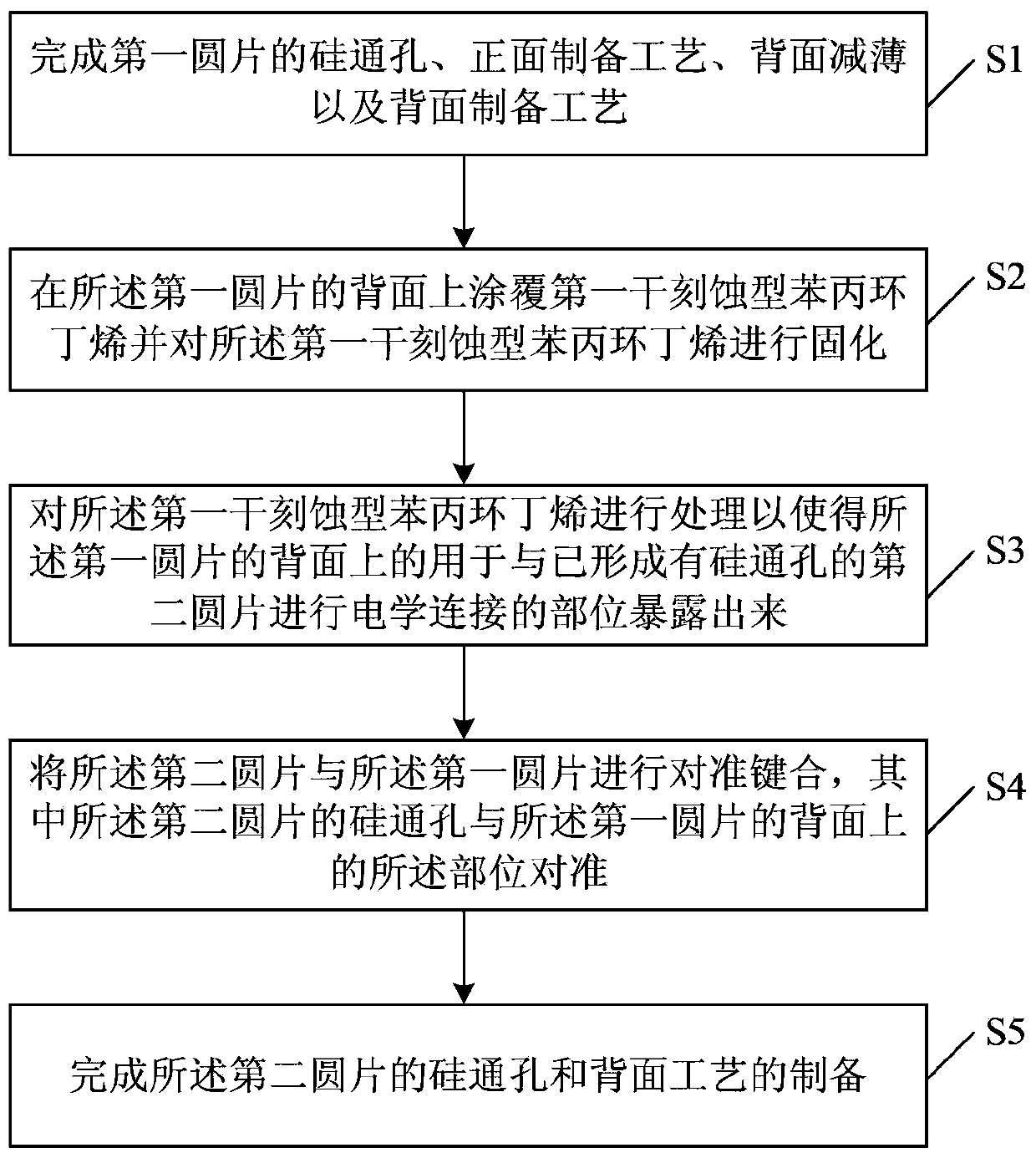

[0016] First, if figure 1 As shown, a wafer-level bonding method for three-dimensional integrated packaging technology according to an embodiment of the present invention includes the following steps:

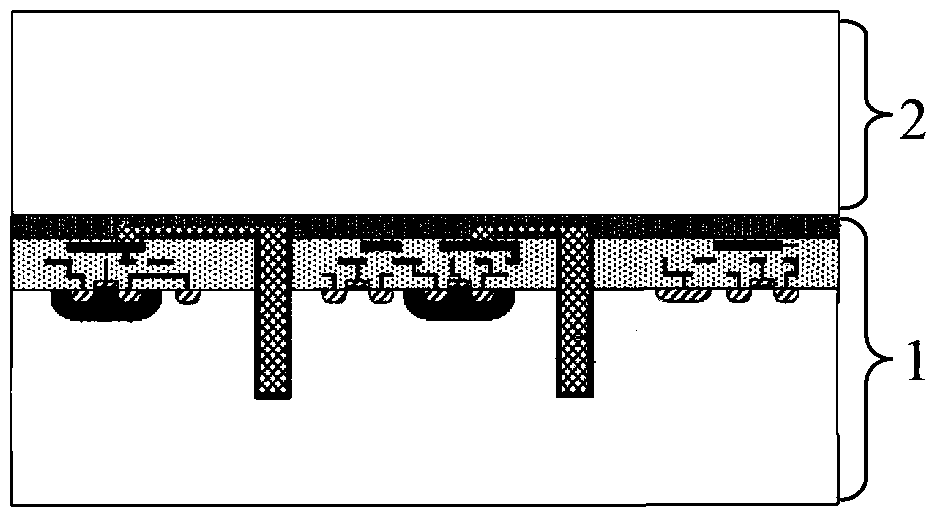

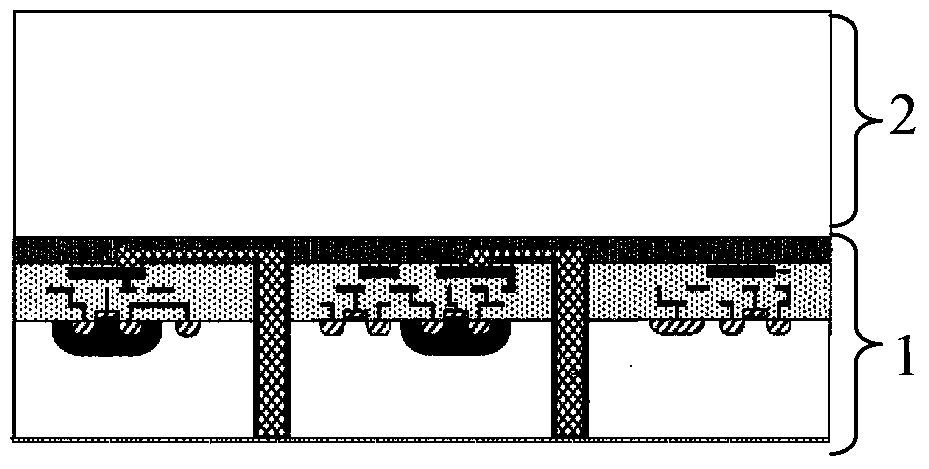

[0017] S1. Complete the through-silicon vias, front-side preparation process, back-side thinning and back-side preparation process of the first wafer;

[0018] S2. Coating a first dry-etched benzopropane (BCB) on the back surface of the first wafer and curing the first dry-etched benzopropene;

[0019] S3. Processing the first dry-etched phenylpropane to expose the portion on the back of the first wafer for electrical connection with the second wafer on which T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More