Semiconductor package piece and manufacturing method thereof

A manufacturing method and packaging technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as insufficient bonding force and weak bonding, so as to increase the area of the electroplating layer and ensure firmness performance, improve the effect of welding firmness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

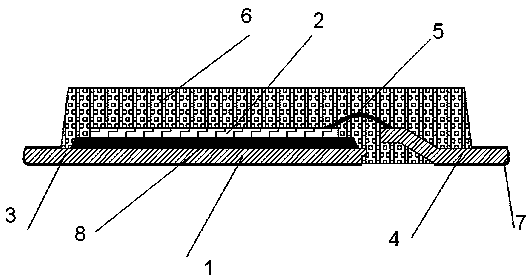

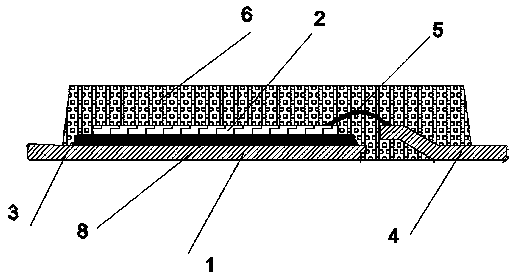

[0029] refer to figure 1 , a semiconductor package, comprising a lead frame 1 and a chip 2, the lead frame 1 has a chip holder 3, the chip 2 is fixed on the chip holder 3 by a bonding material 8, the chip 2 and the lead frame The pin 4 of 1 is connected with a welding wire 5, and an encapsulation compound 6 covers the chip 2 on the lead frame 1. The exposed part of the lead frame 1 is plated with an electroplating layer 7, and at the same time, the side of the pin 4 of the lead frame is plated with Tin layer 7.

[0030] In this embodiment, the tin-plated layer 7 is plated on the exposed part of the lead frame 1, especially the tin-plated layer 7 is plated on the side of the lead frame pin 4, so as to increase the tin-plated layer and the area of the tin-plated layer of the lead frame 1, Therefore, when the semiconductor package is subsequently welded to the PCB board, the firmness of welding of the two is improved.

Embodiment 2

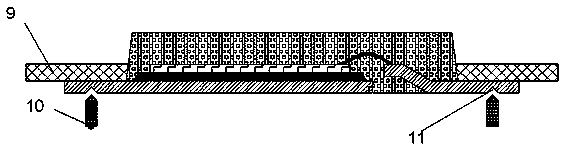

[0032] refer to figure 2 , image 3 , Figure 6 and Figure 7 , a method for manufacturing a semiconductor package, the method steps comprising:

[0033] s1, lay the lead frame 1 flat, and then fix the chip 2 on the chip holder 3 of the lead frame 1 through the bonding material 8, the chip 2 and the pin 4 of the lead frame 1 are connected with a bonding wire 5, and an encapsulation compound 6 Covering the chip 2 on the lead frame 1;

[0034] s2, the inherent concave template 9 on the lead frame 1, use the punch 10 to half-cut the bottom of the two sides of the lead frame 1 (specifically, the chip holder 3 and the pin 4), and the two sides of the lead frame 1 (specifically, the chip holder) 3 and pin 4) Dig out a "∧" shaped gap 11 at the bottom;

[0035] s3, electroplating and tinning the lead frame 1 with the notch 11 dug out in s2, and plating the tin-plated layer 7 on the external exposed part of the lead frame 1;

[0036] s4, the inherent concave template on the lead...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More