Atomic-order flat surface treatment method of silicon wafer, and heat treatment device

A heat treatment device and surface treatment technology, applied in the field of planarization treatment, can solve problems such as undisclosed crystalline defects, unmentioned mass production, etc., and achieve the effect of high yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

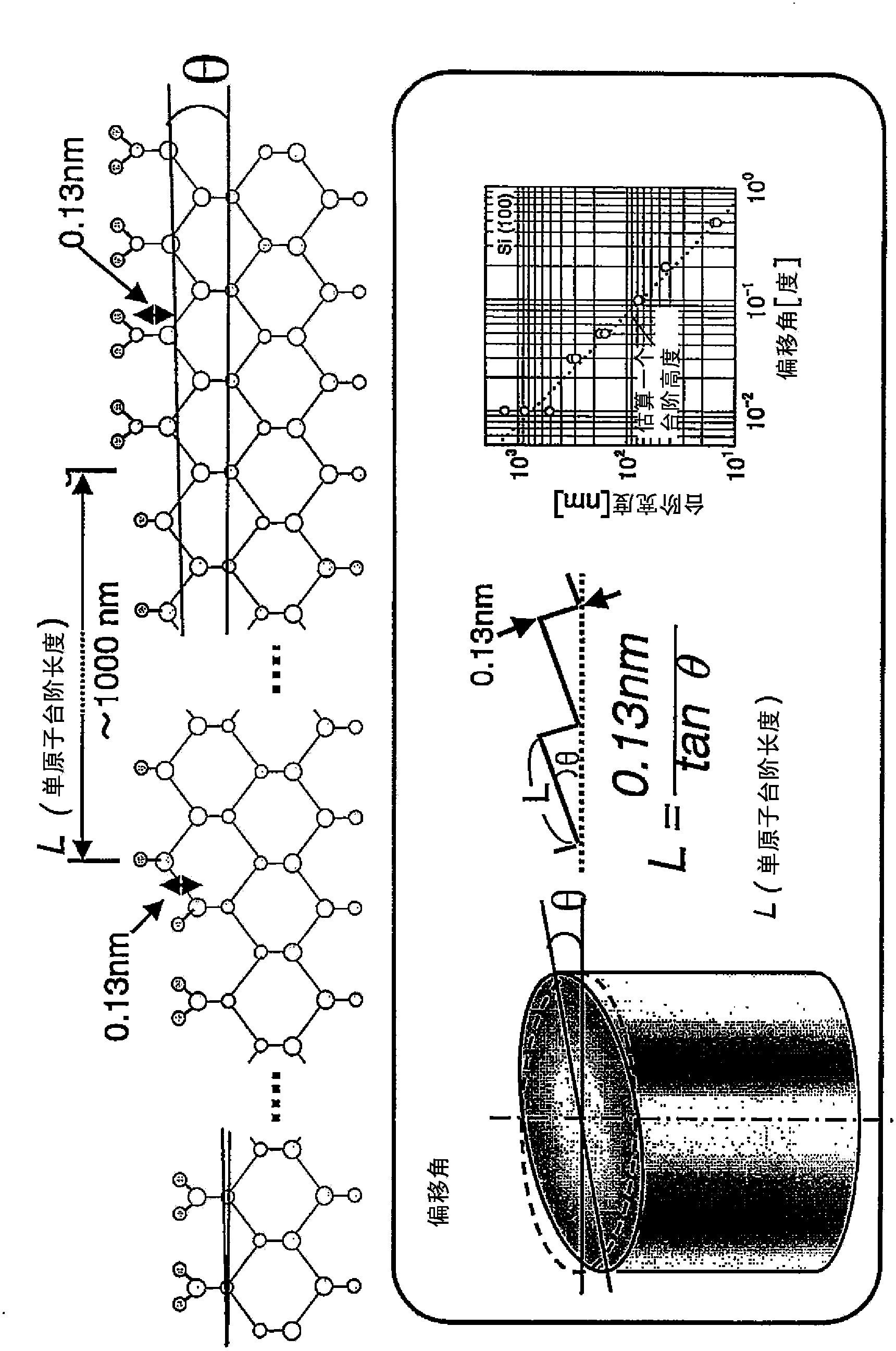

Method used

Image

Examples

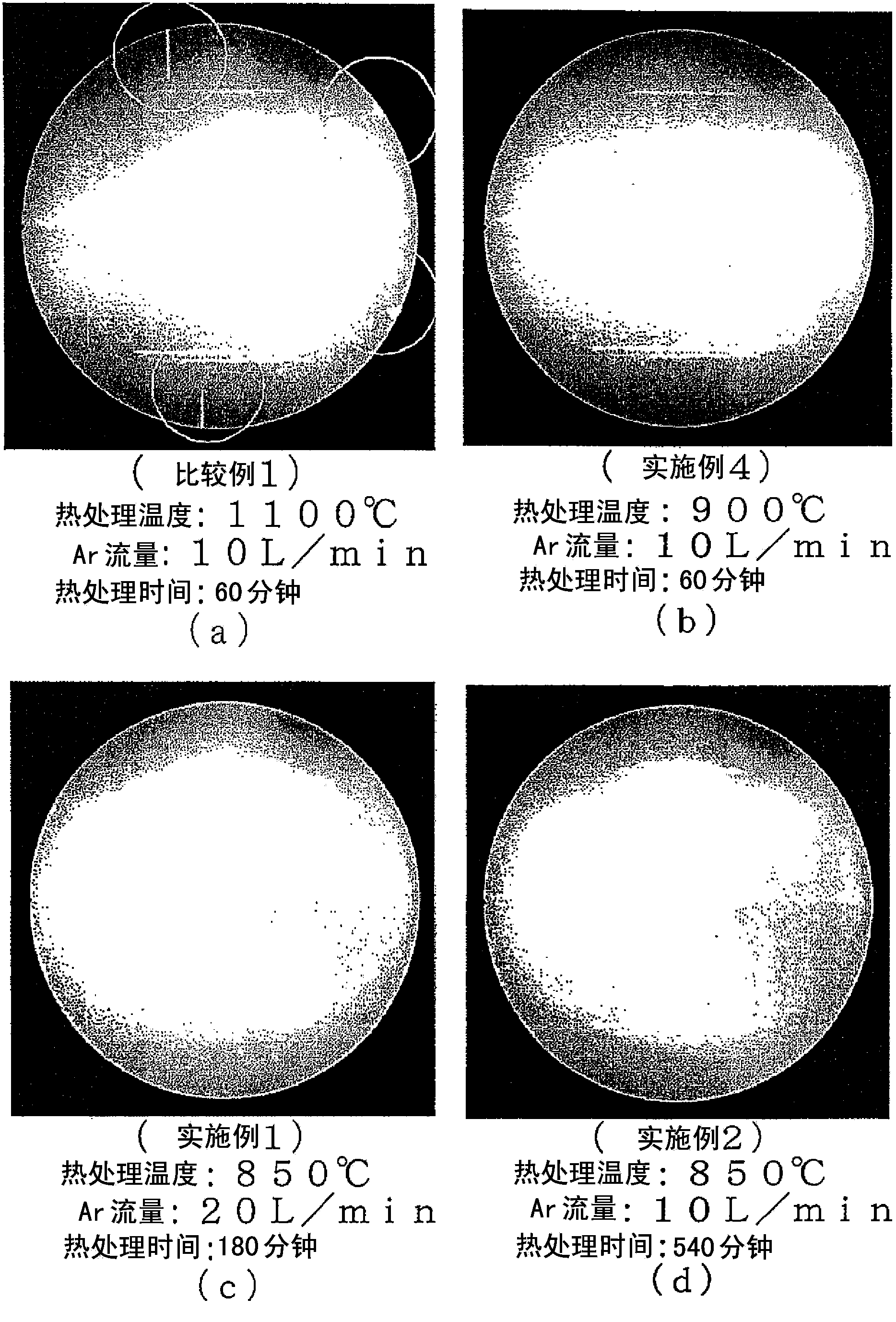

Embodiment 1

[0104] First, a silicon wafer with a diameter of 200mmφ and (100) orientation on the surface was prepared, and the surface of the silicon wafer was cleaned according to the following steps. First, use the O 3 water, the silicon wafer surface was washed for 10 minutes, washed with dilute HF (0.5 wt%) for 1 minute, and finally rinsed with ultrapure water for 3 minutes.

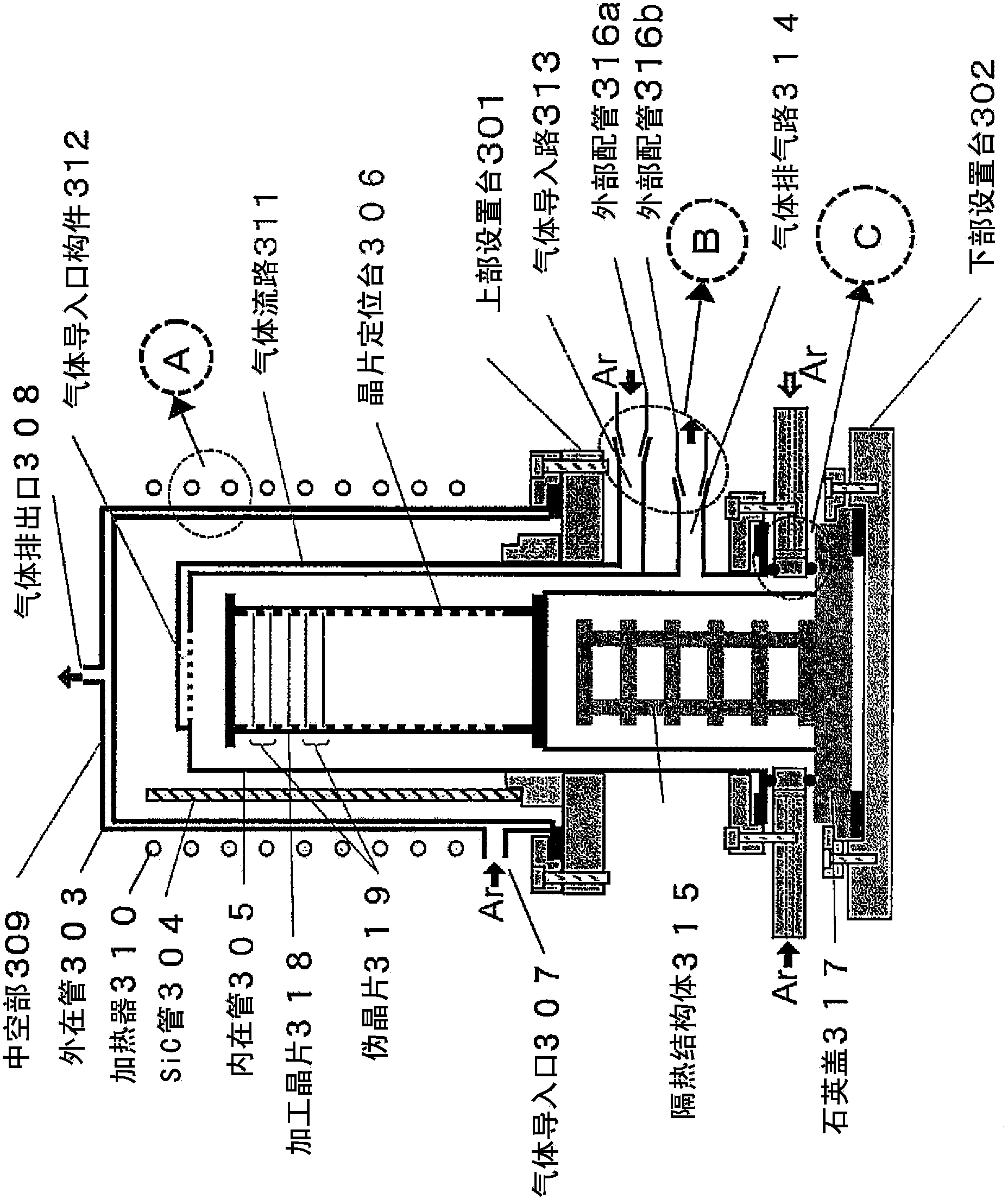

[0105] Then, in image 3 The silicon wafer is placed in the heat treatment apparatus shown, and the water flowing in at 20L / min is 0.2ppb or less, O 2 Heat treatment was performed at a heat treatment temperature of 850° C. and a heat treatment time of 180 minutes while Ar was 0.1 ppb or less.

[0106] However, during heat treatment, do not follow the Figure 4 , 5 , 6 to implement, and set to the above-mentioned patent document 1 Figure 9 Conditions of the heat treatment apparatus equivalent to those carried out in the heat treatment apparatus described in .

[0107] Specifically, first, according to Fi...

Embodiment 2

[0109] A sample was prepared under the same conditions as in Example 1 except that the Ar flow rate was 10 L / min and the heat treatment time (holding time) was 540 minutes.

Embodiment 3

[0111] A sample was prepared under the same conditions as in Example 1 except that the Ar flow rate was 10 L / min and the heat treatment time (holding time) was 270 minutes.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More