A CPU hardware optimization method

An optimization method and hardware technology, applied in the direction of program loading/starting, program control devices, etc., can solve the problems of high bus bandwidth load and low execution efficiency, and achieve the effect of shortening execution time, reducing bandwidth load, and optimizing execution process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

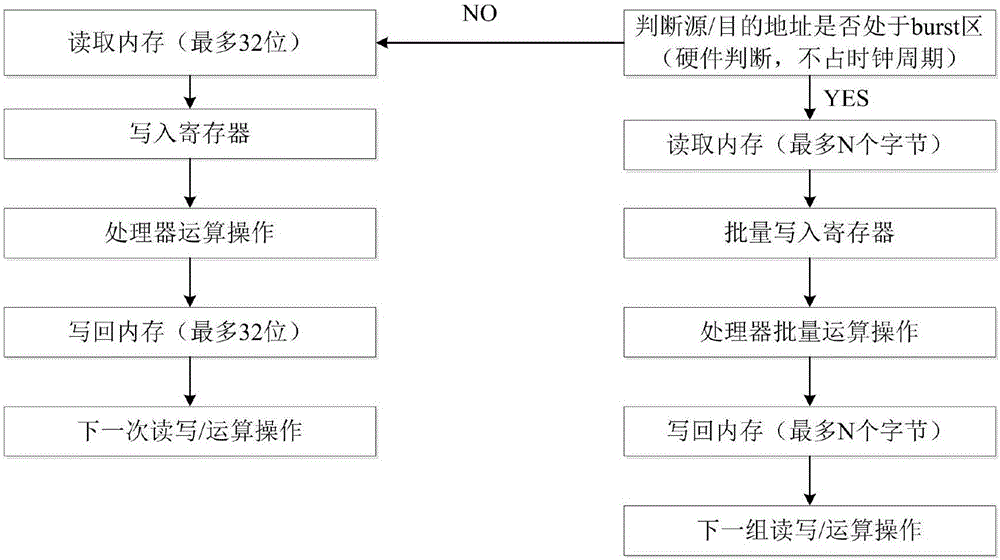

[0024] 椐 Figure 1 to Figure 5 Shown, a kind of hardware optimization method of CPU, its steps are as follows:

[0025] 1. Configure the burst area through the burst address editor

[0026] Assign values to two general-purpose registers in the CPU so that their values correspond to the lower address and upper address of the burst area. Then set a reserved bit of EFLAG to one, assign these two addresses to the burst configuration register group of the CPU, and then perform a zero-set operation on the reserved bit of EFLAG for the next burst area configuration. Repeat this step multiple times to configure multiple burst regions.

[0027] 2. Accelerate memory-to-memory transfer instructions through hardware optimization

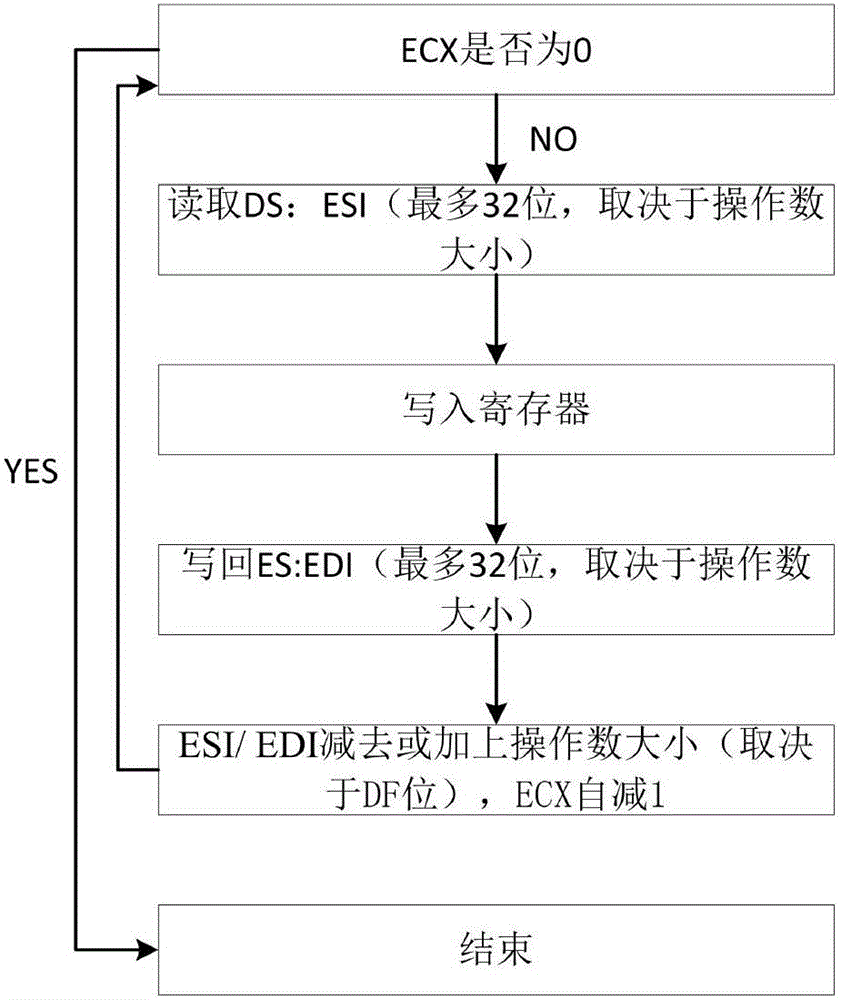

[0028] Taking the REP MOVS instruction as an example, first judge whether the addresses of DS:ESI and ES:EDI are in the burst area through hardware. If it is in the burst area, execute the optimization logic, otherwise execute the original logic. In t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More