SRIO interconnection exchanging device based on field programmable gate array (FPGA)

A technology of switching devices and interconnecting modules, applied in the field of communications, can solve the problems of low cost performance, occupation, and high chip prices.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the objectives, technical solutions, and advantages of the embodiments of the present invention clearer, the technical solutions of the present invention will be introduced below in conjunction with the embodiments of the present invention and the accompanying drawings.

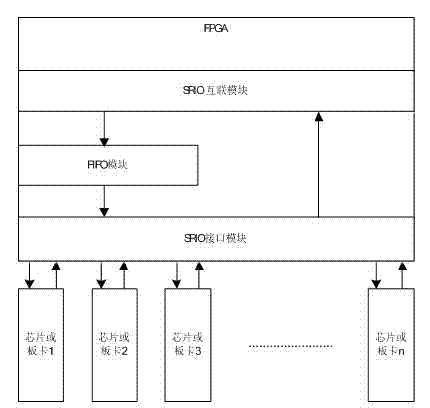

[0024] See attached figure 1 , The SRIO interconnection exchange device provided by the embodiment includes an SRIO interconnection module, a FIFO module, and an SRIO interface module:

[0025] SRIO interconnect module, used to exchange data between various chips or boards within the FPGA to achieve data exchange between chips or boards;

[0026] The FIFO module is used to isolate the SRIO interconnection module from the SRIO interface module, and also serves as a data buffer;

[0027] The SRIO interface module is used to ensure that the FPGA receives or sends data based on the SRIO protocol.

[0028] The present invention implements the SRIO interconnection exchange device based on the programm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More