Cyclic time to digital convertor

A digital converter and cycle time technology, applied in analog/digital conversion, code conversion, instrumentation, etc., can solve the problems of high delay unit matching requirements, multi-chip area, consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to increase the input range of the traditional TDC, maintain linearity within a larger input range and reduce design requirements. The present invention provides a cycle time digital converter circuit, which is described in detail below:

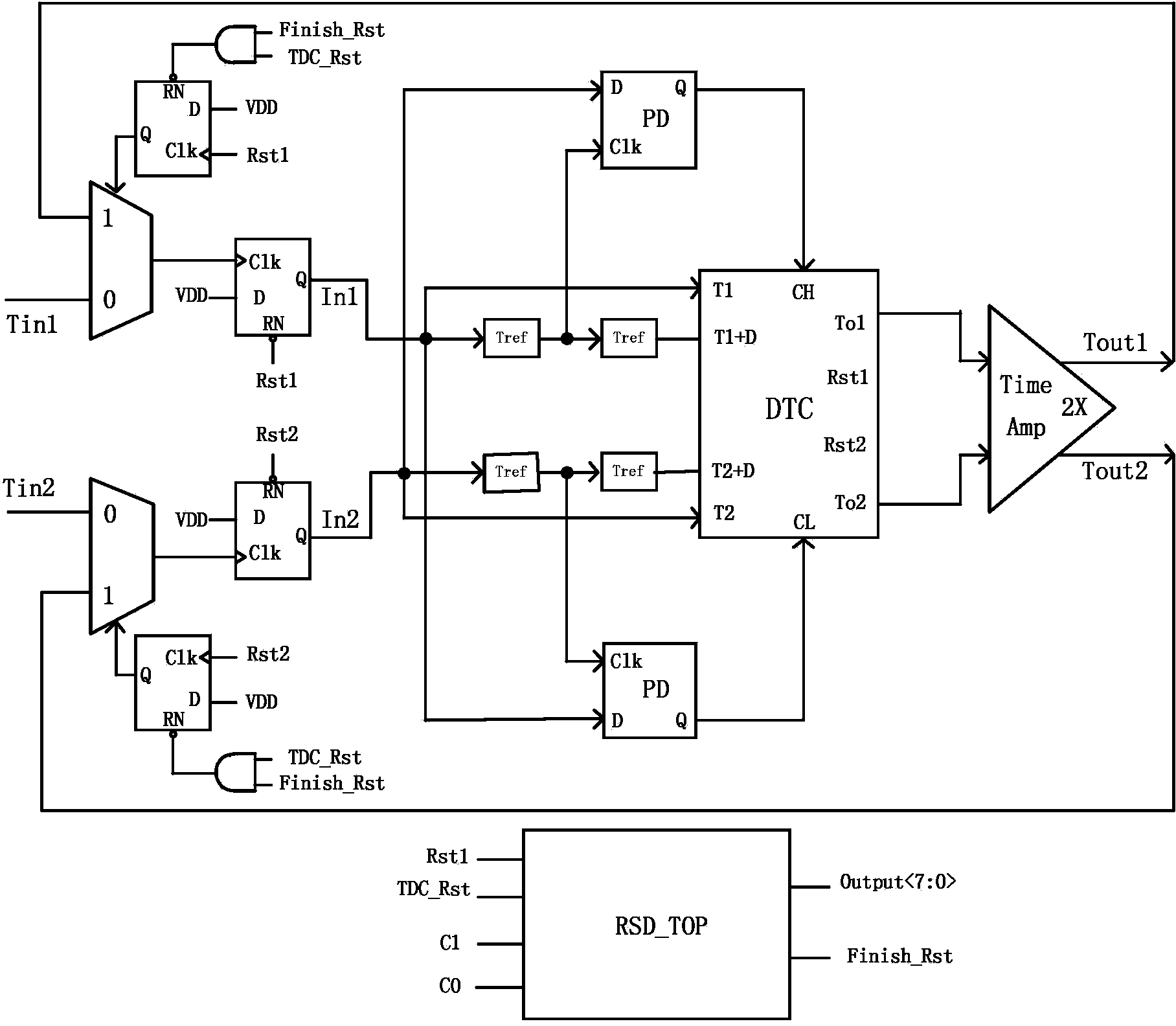

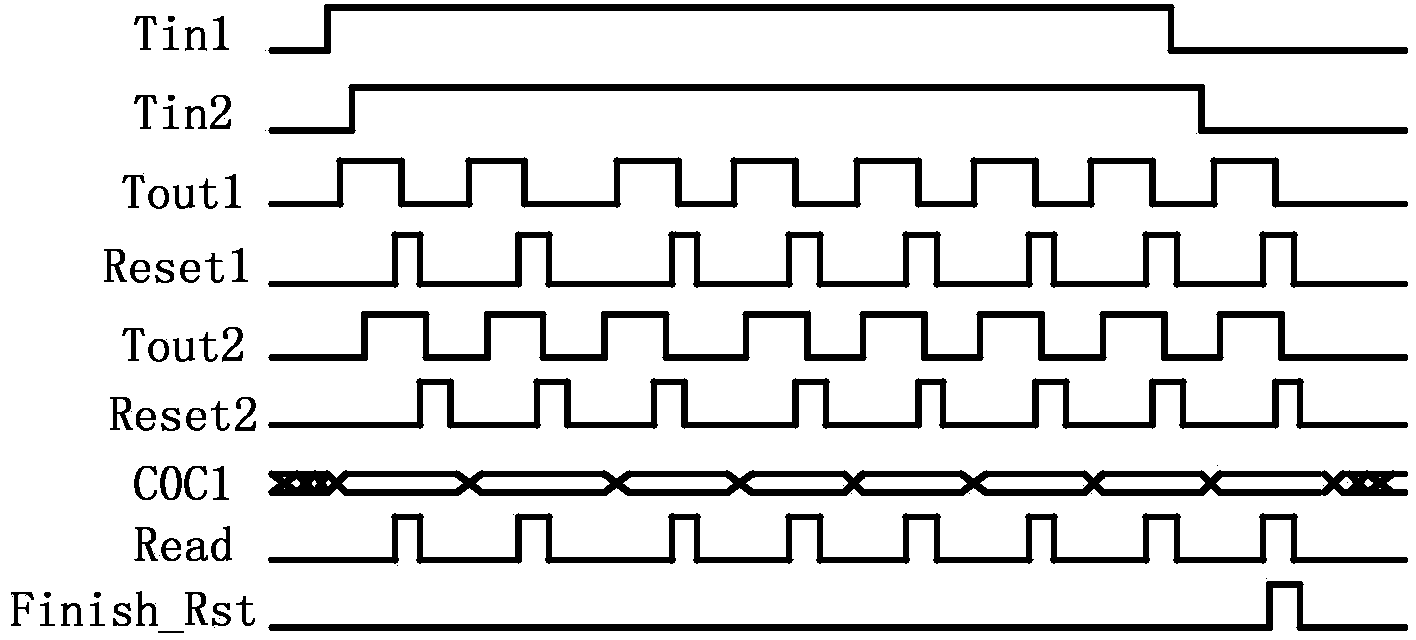

[0031] See figure 1 , The circuit block diagram of the cycle time digital converter includes: multiplexer, D flip-flop, delay unit, phase detector, sub-DTC (digital to time converter), readout circuit, time amplifier, NOT gate, AND gate Wait.

[0032] Cyclic TDC adopts a symmetrical structure. The symmetrical structure can obtain an algorithm similar to Cyclic ADC and eliminate matching errors to obtain good linearity. The multiplexer selects the initial time signal and the residual signal. The PD phase detector compares the phase difference between In1 and In1 after passing through the delay unit. The result of the comparison is used as the DTC input for further conversion.

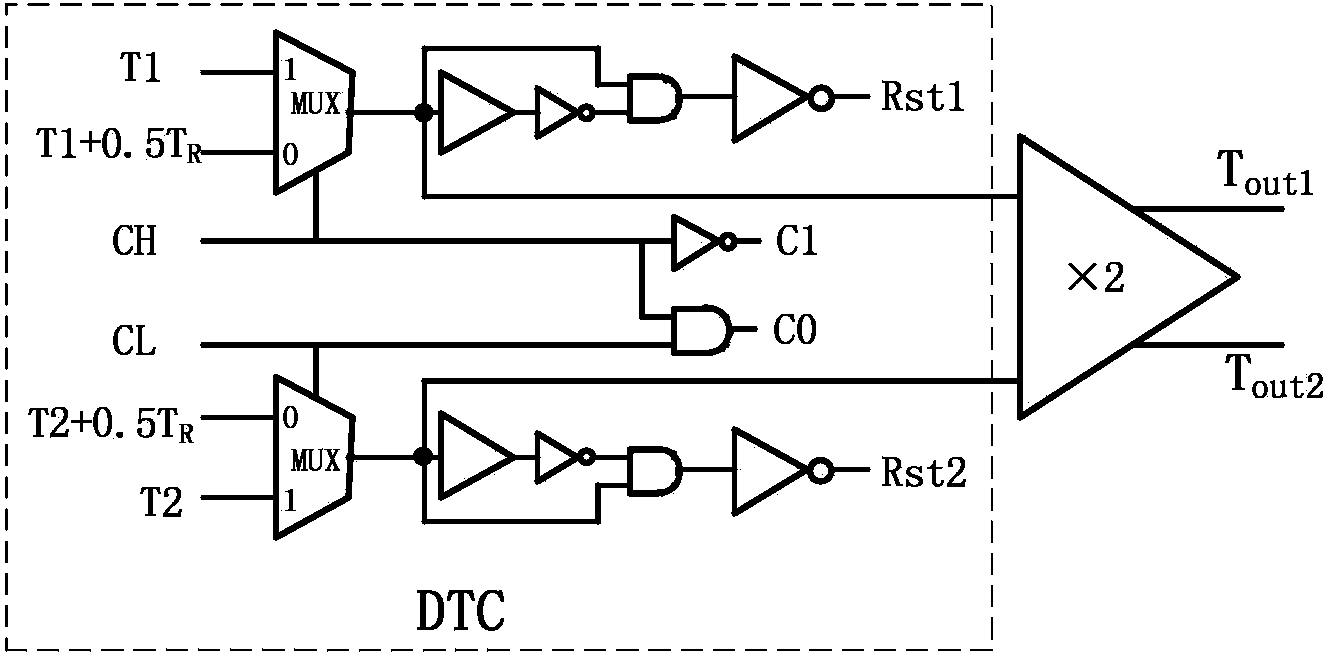

[0033] The principle circuit diagram of DTC see ima...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More