Improved structure for cmos etsoi with multiple threshold voltages and active well bias capability

A biasing and insulating layer technology, applied in the direction of electric solid-state devices, circuits, electrical components, etc., can solve the problems of random doping fluctuations, increased drain leakage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

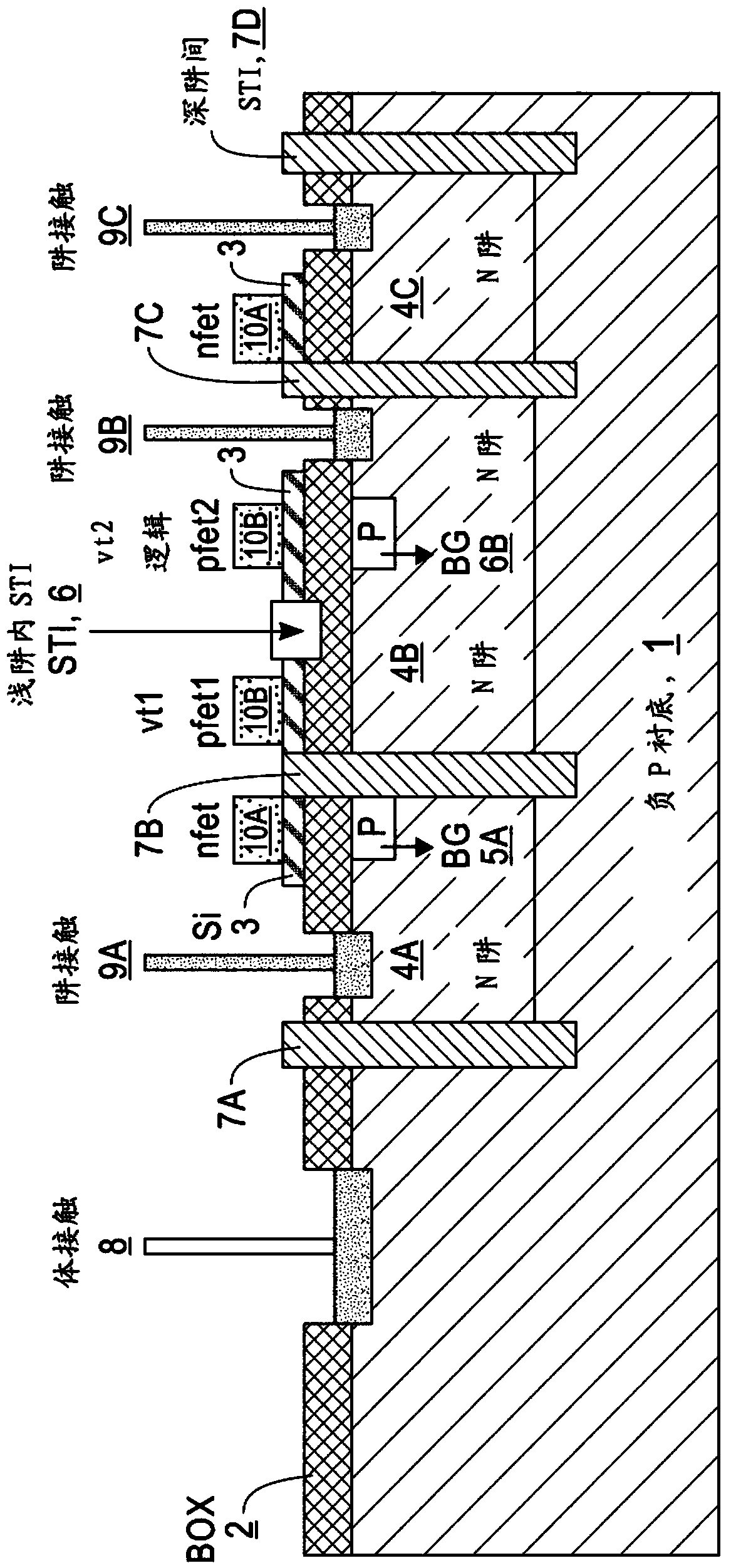

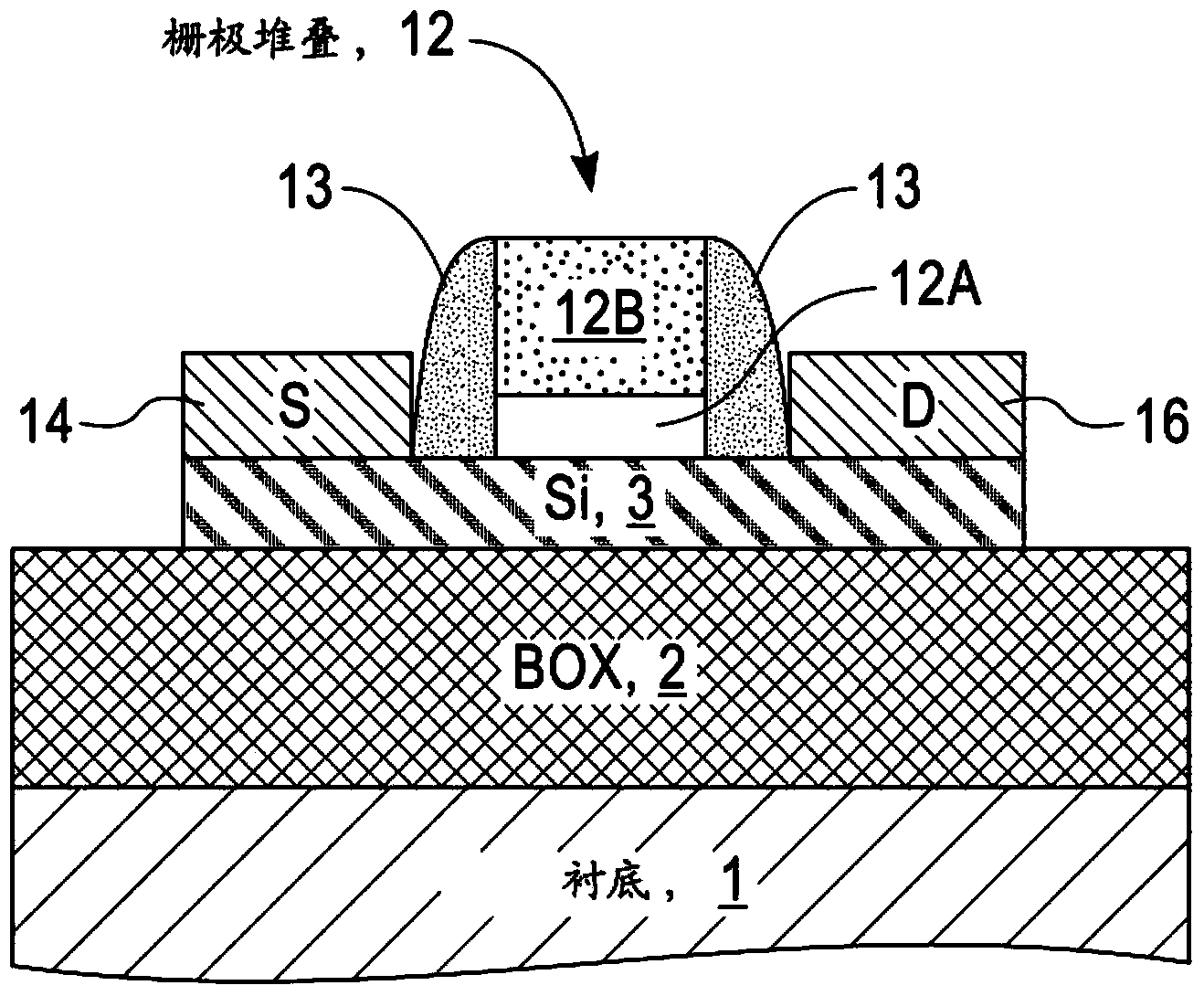

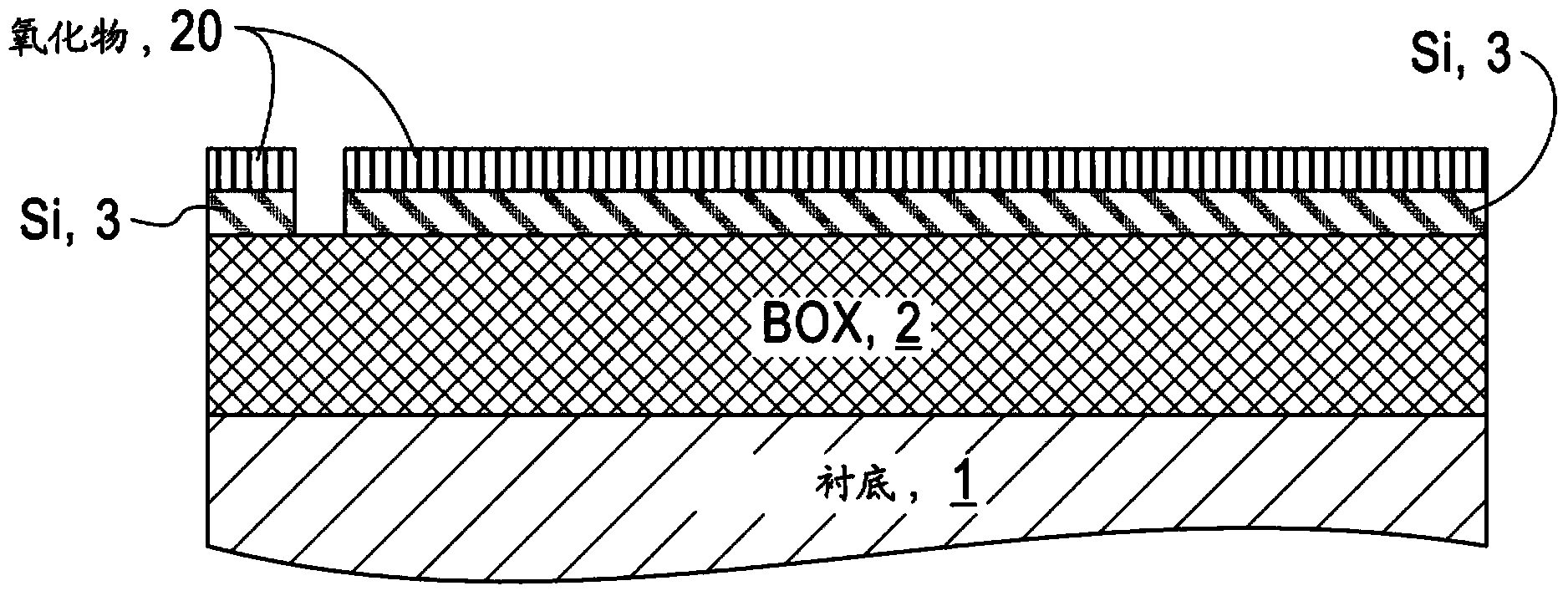

[0015] Overall, it may be advantageous to use different back gate doping types (p-type or n-type) to achieve the desired transistor threshold voltage. Basically, two different threshold voltages are achieved using two different doping types. Changing the back gate type from n-type to p-type results in a change in work function of about one volt, which is electrically equivalent to changing the applied potential by that amount. Using a different doping of the back gate may be simpler to implement than modifying the work function of the top gate and can reduce the number of masks required. Additionally, different back gates can be used for other functions.

[0016] It may also be beneficial to apply different back gate biases to nFETs and pFETs in order to tune performance, compensate for process variations and optimize a given front gate work function.

[0017] It may also be advantageous to apply the same backgate bias to all NFETs and the same backgate bias to all PFETs in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More