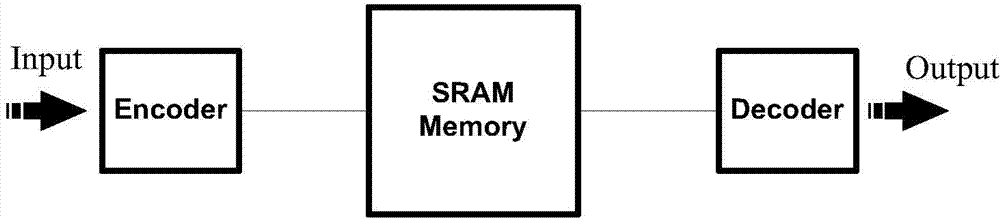

Error correction circuit of SRAM (Static Random Access Memory)-type memory

An error correction circuit and memory technology, which is applied in static memory, instruments, etc., can solve the problems that the encoding circuit and the decoding circuit cannot improve the reading and writing speed, increase the production cost of the device, and increase the power consumption of the device.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to make the above-mentioned purposes, features and advantages of the present invention more obvious and understandable, the specific implementation modes of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the above-mentioned and other purposes, features and advantages of the present invention will be clearer. Like reference numerals designate like parts throughout the drawings. The drawings have not been drawn to scale, emphasis instead being placed upon illustrating the gist of the invention.

[0022] Such as figure 2 As shown, the present invention provides an error correction circuit for SRAM memory, which includes: an encoding module Encoder, a first transmission gate module TG, a second transmission gate module and an exclusive OR operation module TG&XOR, and an error correction circuit module Locating error.

[0023] In this embodiment, the input end of the encoding module Encoder is connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More