Baseband signal processor supporting multi-chip architecture and processing method of baseband signal processor

A baseband signal and processor technology, applied in baseband system components and other directions, can solve problems such as high cost, inability to be handled by baseband signal processors, and impracticality, and achieve the effect of improving scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

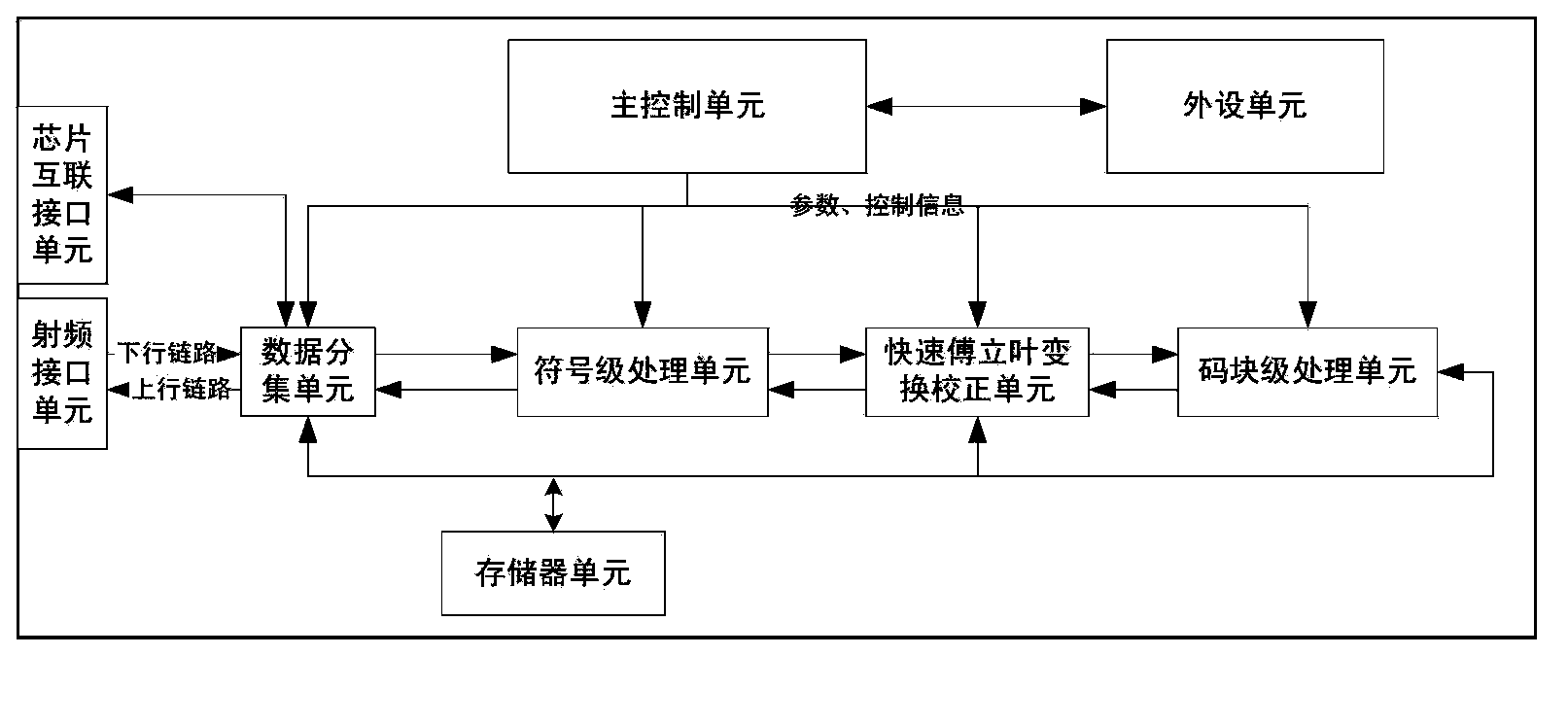

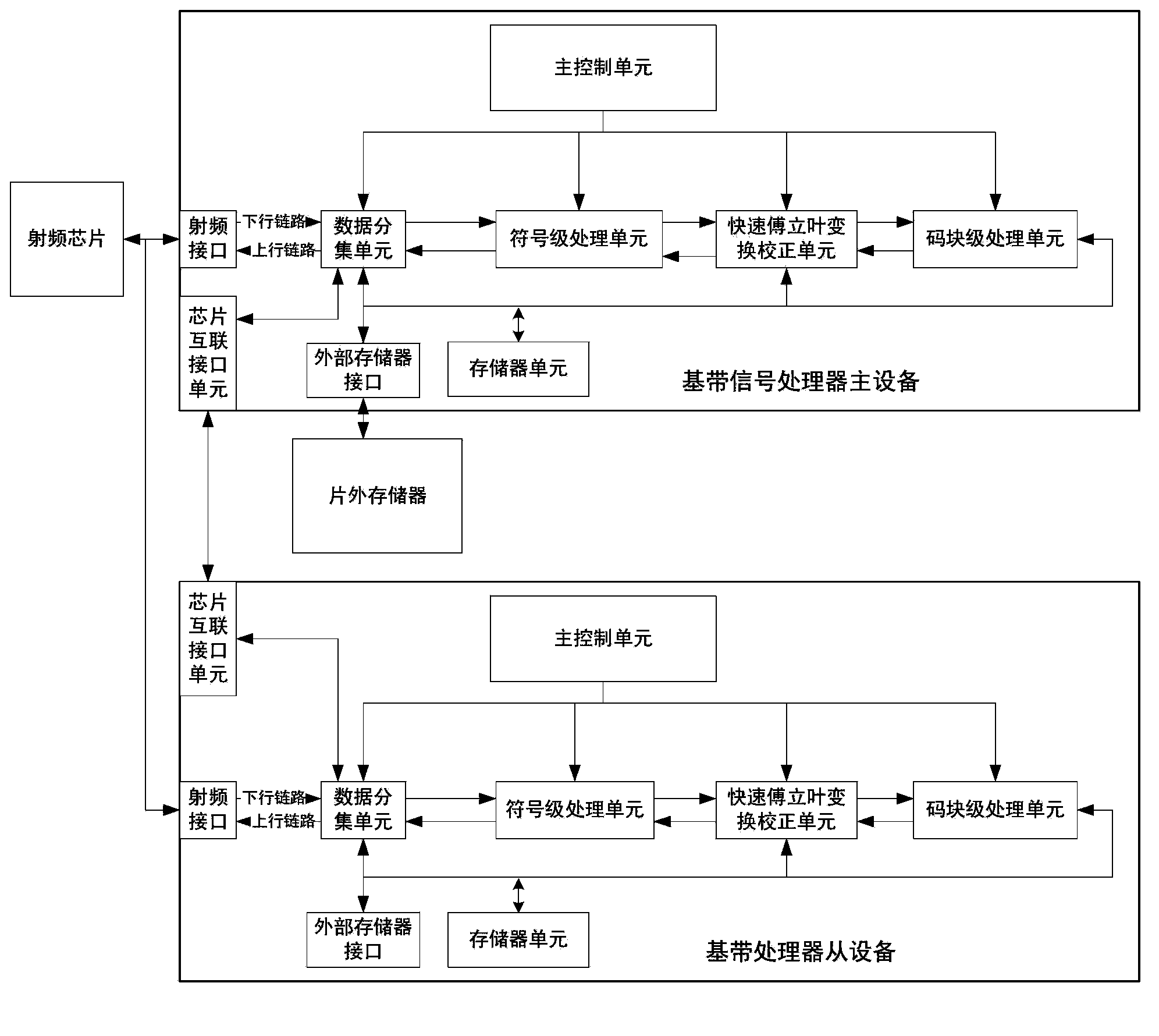

[0035] Embodiment 1: Application of a baseband signal processor with dual-chip architecture

[0036]Assuming that the single baseband signal processor of the present invention realizes FFT of 4096 points internally, it can support a wireless broadband communication system with a bandwidth of 20MHz. In this embodiment, the wireless broadband communication system supporting a bandwidth of 40MHz is used as an example. figure 2 In the dual-chip architecture shown, the two baseband signal processors cooperate in a master-slave mode, which can meet the bandwidth requirement of 40MHz.

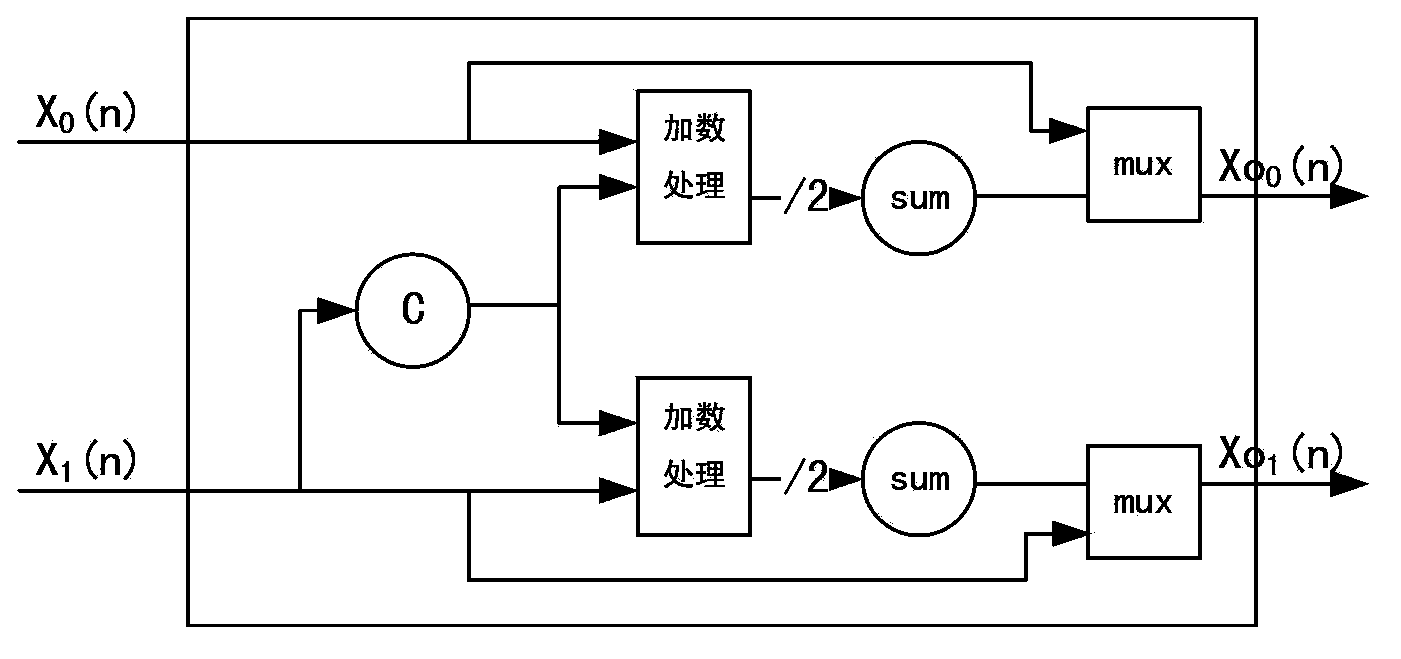

[0037] The following focuses on the three core hardware units added by the single baseband signal processor of this embodiment to the ordinary baseband signal processor: data diversity unit, chip interconnection interface unit and fast Fourier transform correction unit.

[0038] Data Diversity Unit:

[0039] According to the configuration of the main control unit, the data diversity unit provides th...

Embodiment 2

[0047] Embodiment 2: Another implementation scheme of the chip interconnection interface unit

[0048] On the basis of the first embodiment, the chip interconnection interface unit of this embodiment is realized by using another implementation scheme. This embodiment uses an existing or future mature high-speed interconnection interface, and cooperates with some handshake signals to realize high-speed interconnection between chips.

[0049] Existing high-speed interconnection interfaces that meet the above-mentioned communication rate requirements include the following: DigRF V4, USB3.0, FireWire IEEE 1394-2008, and C2C technology of Arteris based on DDR mode. In the typical application of two-chip interconnection, the above-mentioned high-speed interconnection interface cooperates as follows: Figure 5 The interactive handshake signals shown can realize high-speed data exchange between two chips, and the functions of these interactive handshake signals are the same as those ...

Embodiment 3

[0052] Embodiment 3: Downlink baseband signal processing method of 40MHz SISO system

[0053] In this embodiment, a 40 MHz SISO system is taken as an example, and the dual-chip architecture baseband signal processor of Embodiment 1 is adopted. The external radio frequency chip undertakes the function of transmitting and receiving wireless signals, outputs time-domain sampling data to the baseband signal processor, and receives time-domain sending sampling data from the baseband signal processor. This embodiment adopts a commonly used radio frequency chip, and only faces one baseband signal processor, that is, it can simultaneously output time-domain sampling data to two baseband signal processors, but only receives time-domain transmission sampling data from the baseband signal processor main device, to avoid interface bus conflicts. If there is a radio frequency chip that can interface with multiple baseband signal processors, then multiple baseband signal processors can sim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More