A pulse d-type flip-flop using floating gate MOS tube

A MOS tube and flip-flop technology, which is applied in the field of pulse D-type flip-flops, can solve the problems of inferior performance such as speed and power consumption, and achieve the effects of higher power consumption, better speed, and better power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with the accompanying drawings and embodiments. While the invention will be described in conjunction with the preferred embodiments, it will be understood that it is not intended to limit the invention to the described embodiments. On the contrary, the invention is to cover alternatives, modifications and equivalents, which may be included within the scope of the invention as defined by the appended claims.

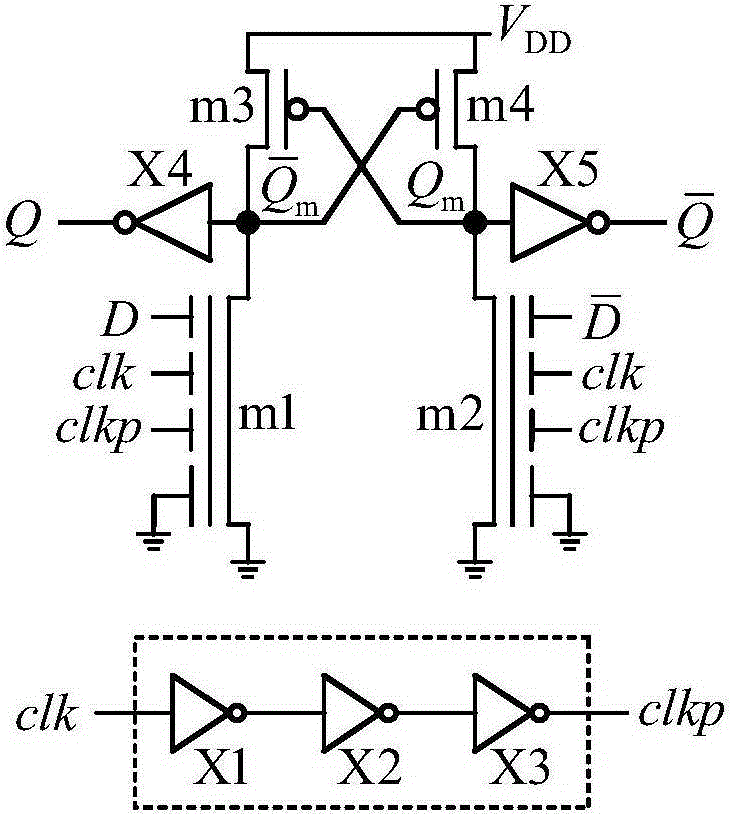

[0024] Such as image 3 As shown, this pulsed D-type flip-flop using a floating gate MOS transistor includes an inverter chain for inverting and delaying the clock signal, a pair of differentially configured pull-down multi-input floating gate MOS transistors, a pair of cross-coupled pMOS tube and two output inverters;

[0025] The inverter chain for inverting and delaying the clock signal is composed of inverters connected in series, including: a first inverter X1, a second inverter X2 and a th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More