Packaging structure

A technology of packaging structure and plastic sealing layer, which is applied in the direction of printed circuit, circuit, electric solid device, etc., can solve the problem of low packaging efficiency, achieve the effect of improving efficiency, meeting packaging requirements, and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

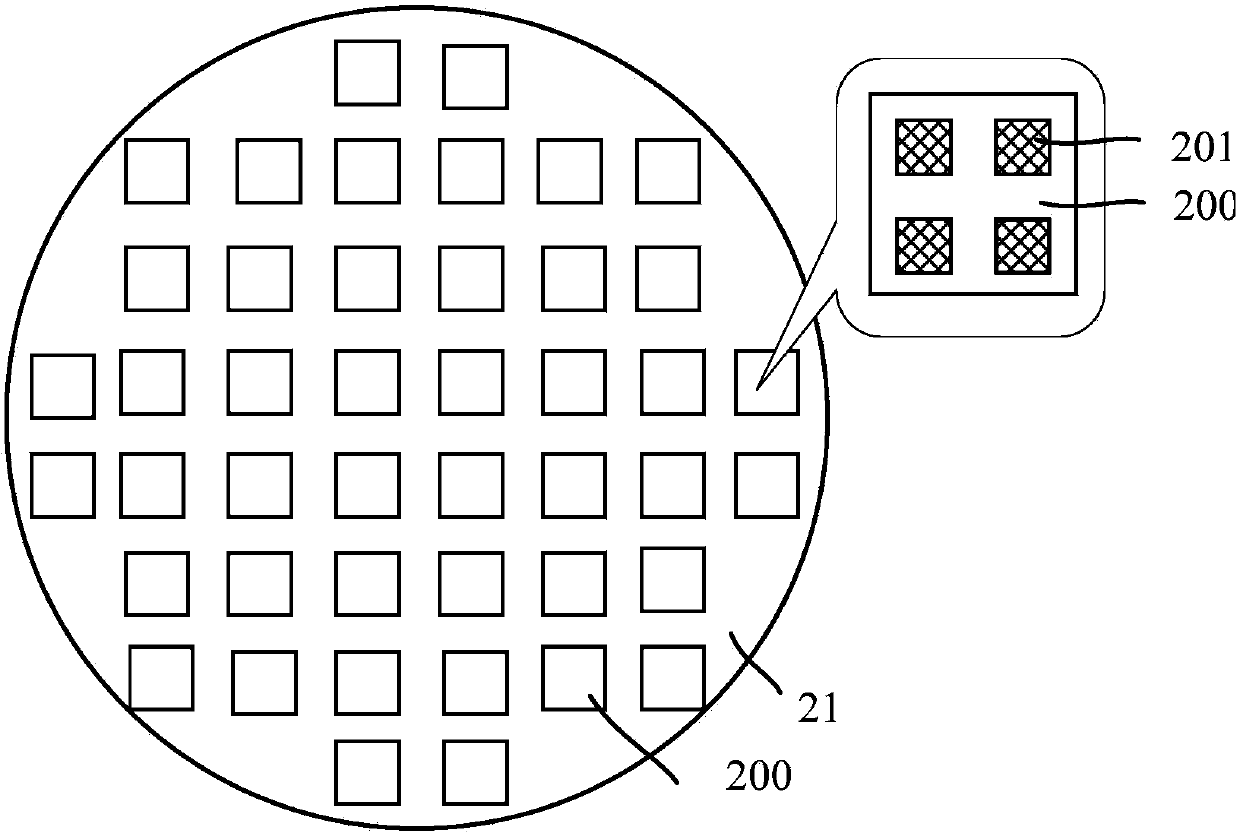

[0022] The existing POP packaging technology is to stack a single semiconductor chip on a circuit carrier, and the packaging efficiency is low.

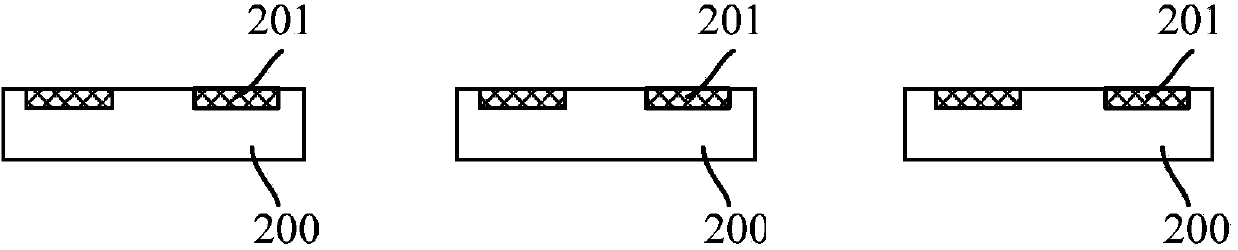

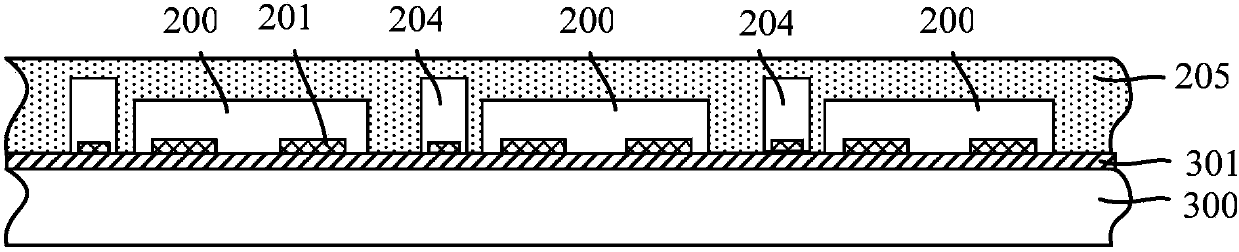

[0023] For this reason, the present invention provides a package structure comprising a pre-sealing board, a plurality of semiconductor chips are packaged in the pre-sealing board, and the semiconductor chips on the pre-sealing board and the input pads of the circuit carrier are connected together by metal bumps , to realize the integrated packaging of multiple semiconductor chips and the circuit carrier, and improve the packaging efficiency.

[0024] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. When describing the embodiments of the present invention in detail, for convenience of explanation, the schematic diagrams will not be partially enlarged ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More