Formal verification method for sequencing specification of FPGA (field programmable gate array) combinatorial logic system

A formal verification and combinatorial logic technology, applied in the verification field of FPGA combinatorial logic system sequence specification, can solve problems such as difficult program verification, state space explosion, and infinite loop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

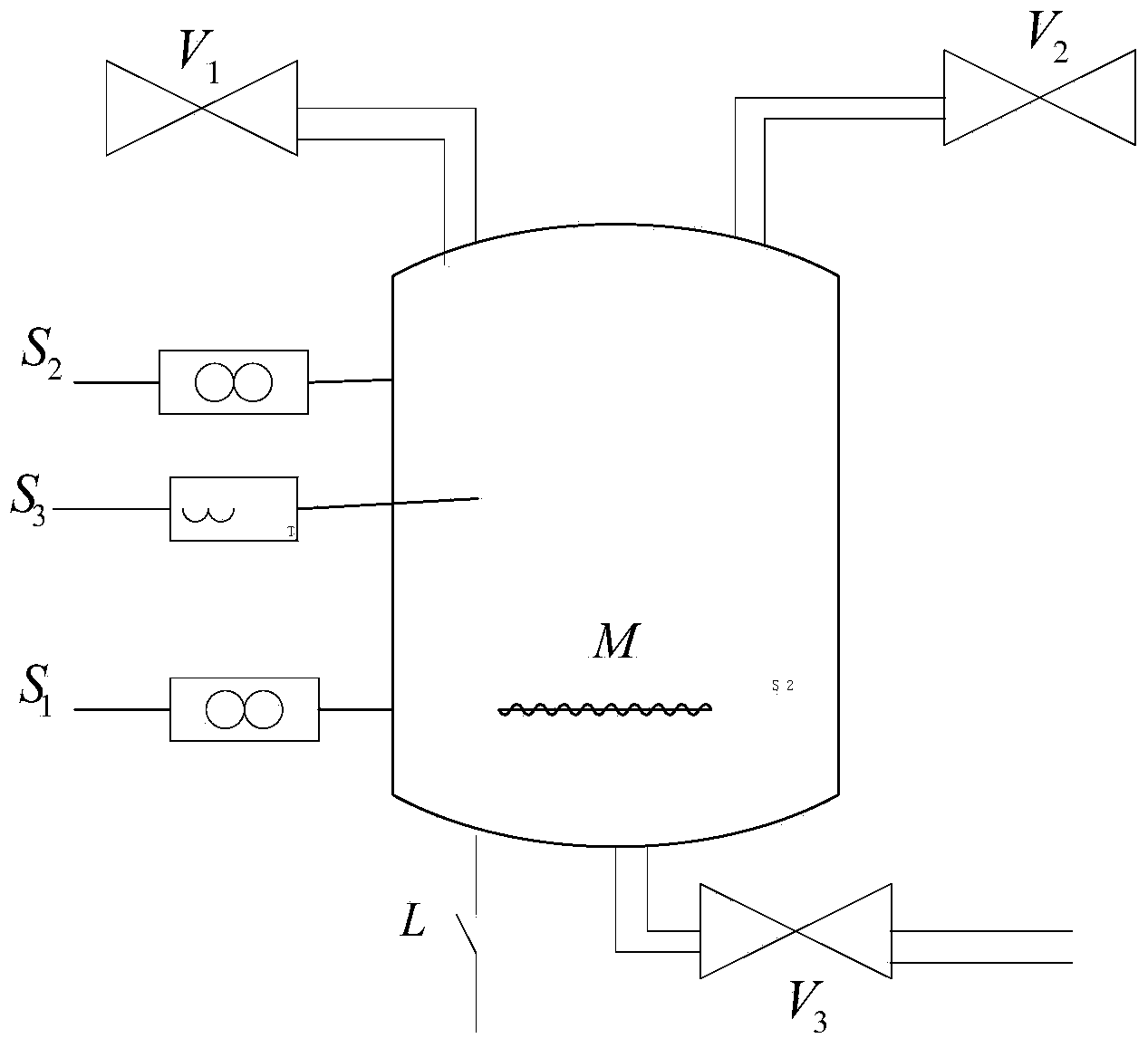

[0104] The present invention provides a kind of formal verification method of FPGA combinatorial logic system sequence specification, comprises the following steps:

[0105] 1) according to the order of operation specification of FPGA combinatorial logic system, obtain a VHDL program describing said FPGA combinatorial logic system; Wherein, said VHDL program includes setting the input quantity, output quantity of said FPGA combinatorial logic system, and said A logical relationship between input and output quantities, both of which are Boolean variables;

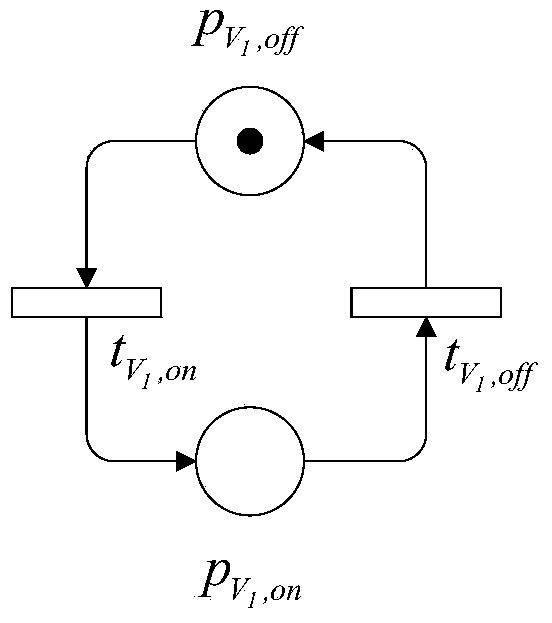

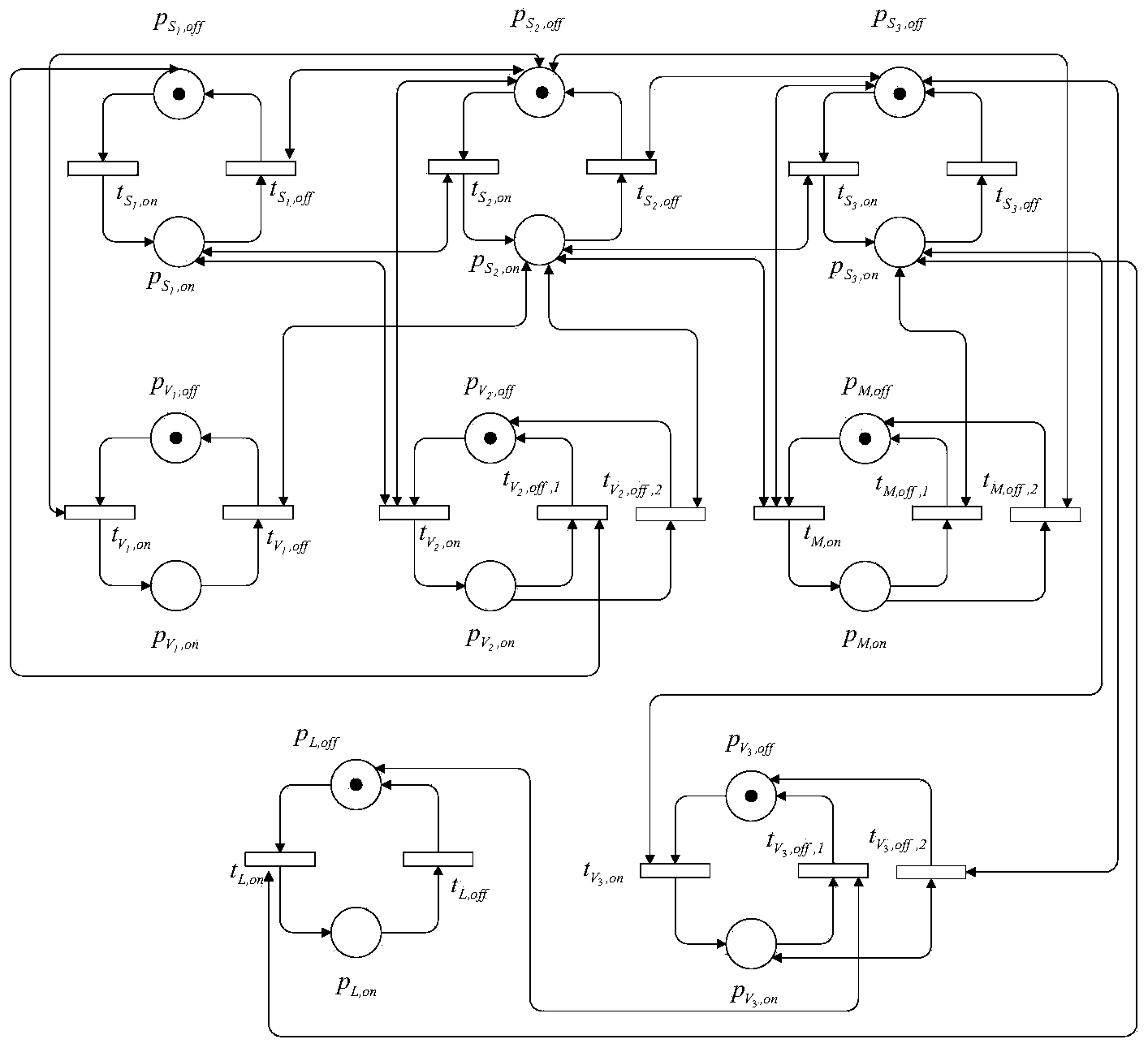

[0106] 2) for the input quantity, the output quantity of the VHDL program, and the logical relationship between the input quantity and the output quantity, set up a Petri net model; wherein, the Petri net model includes the state of each variable in the VHDL program , transitions between states, and the triggering conditions for each transition;

[0107] 3) according to the state of each variable in the Petri net model, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More