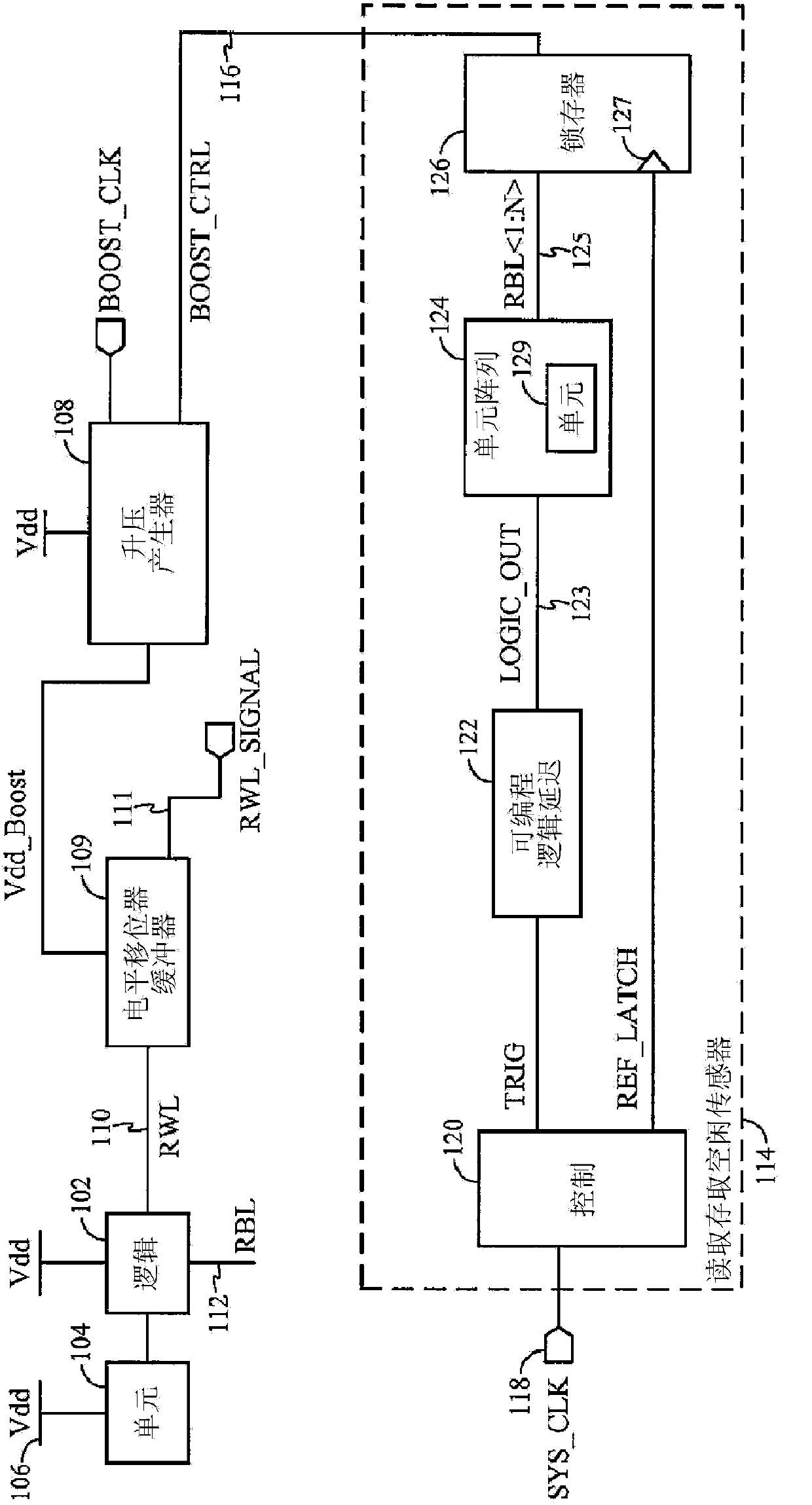

Adaptive read wordline voltage boosting apparatus and method for multi-port SRAM

A technology of supply voltage and equipment, applied in the field of static random access memory, which can solve the problems of SRAM cache memory performance degradation, affecting SRAM cache memory, high voltage sensitivity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

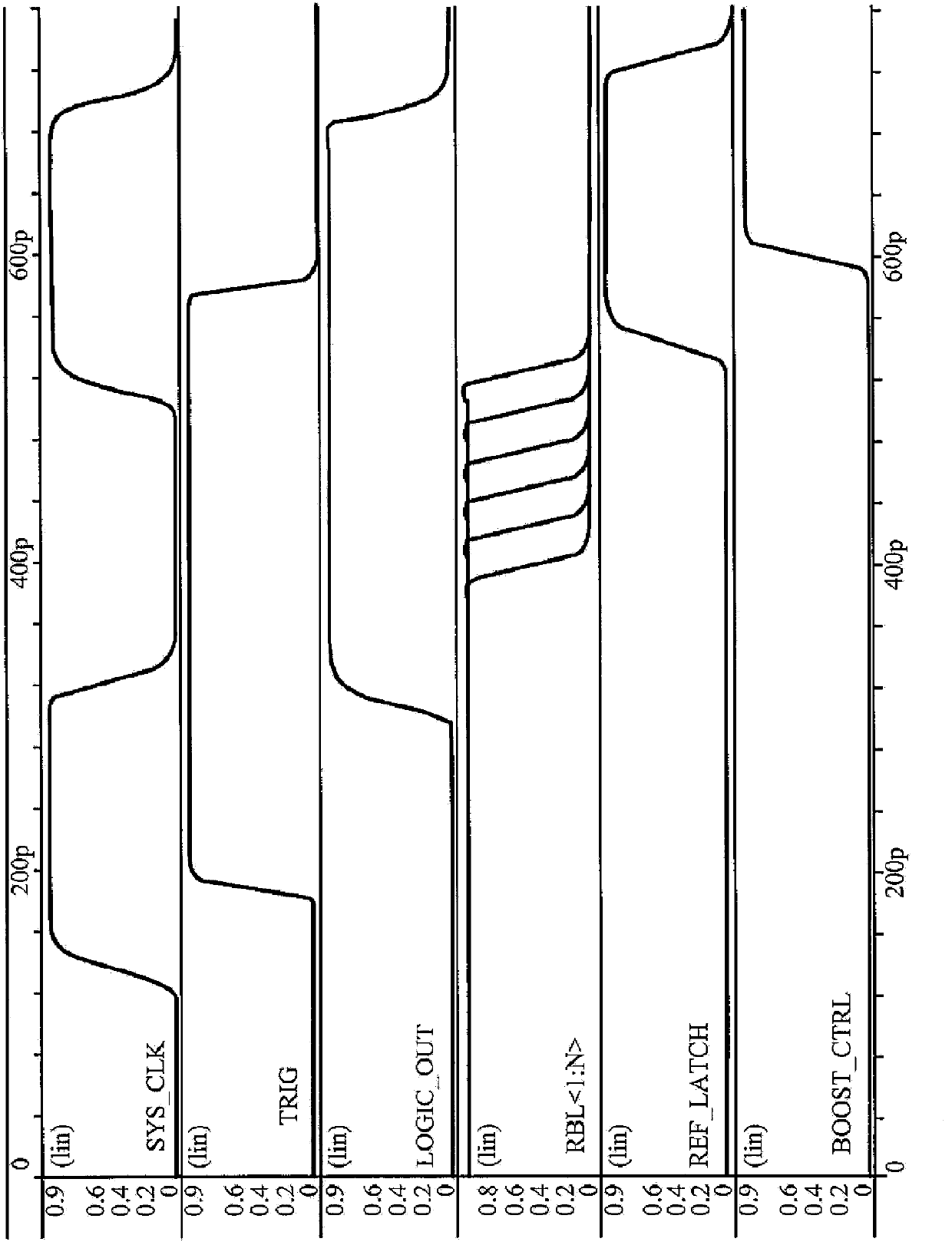

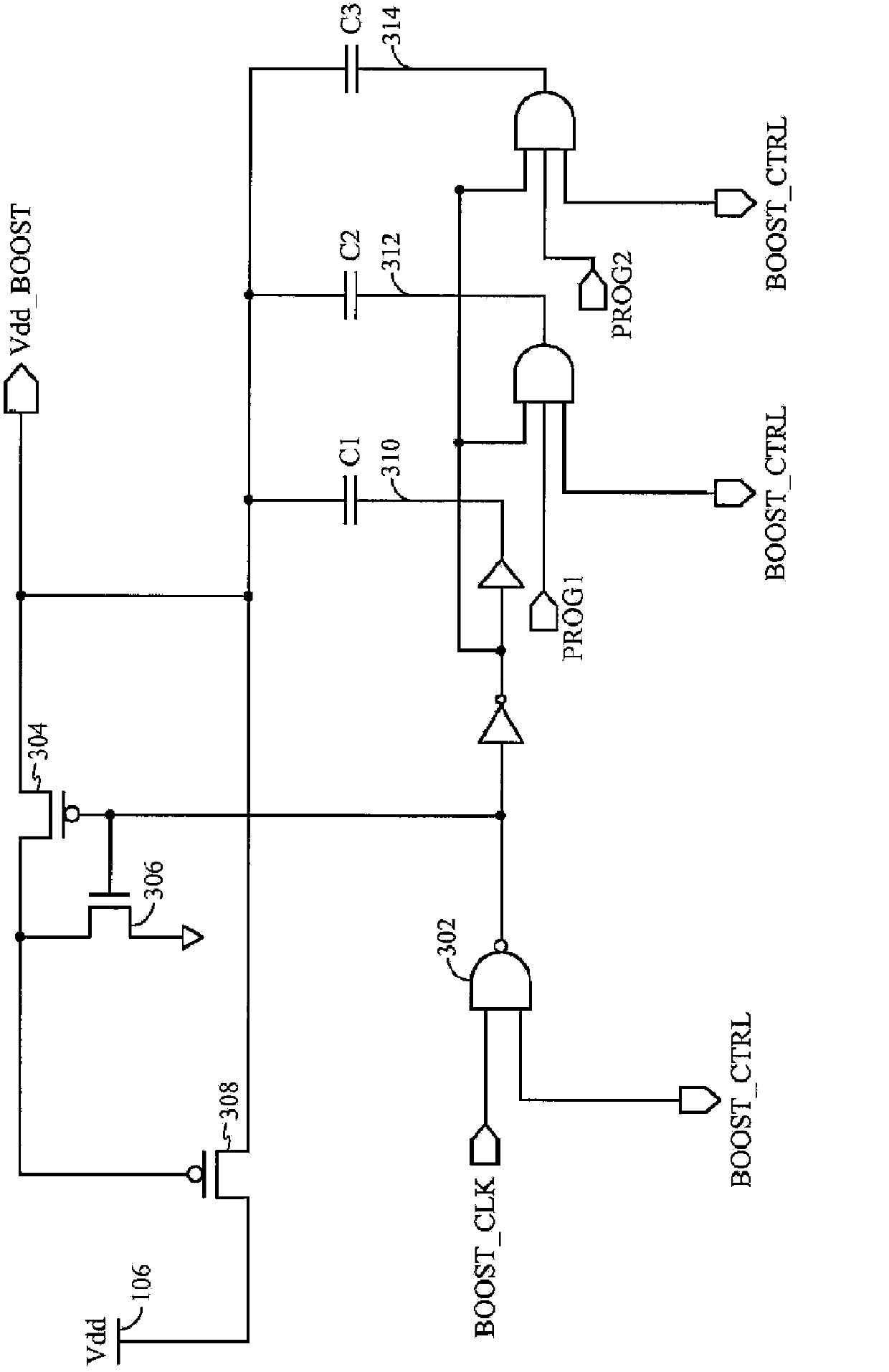

Embodiment Construction

[0019] Aspects of the invention are disclosed in the following description and associated drawings directed to specific embodiments of the invention. Alternative embodiments may be devised without departing from the scope of the invention. Additionally, well-known elements of the invention will not be described in detail or will be omitted so as not to obscure the relevant details of the invention.

[0020] The term "embodiments of the invention" does not require that all embodiments of the invention include the discussed feature, advantage or mode of operation.

[0021] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the embodiments of the invention. As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms unless the context clearly dictates otherwise. It will be further understood that the terms "comprises", "comprises", "comprises" and / or "comprising" when...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More