Power grid topology error identification system and method based on road-loop equation

A power grid topology and topology error technology, applied in the direction of measuring electricity, measuring electrical variables, measuring current/voltage, etc., can solve the problems of single data source, inability to effectively identify, asynchronous, etc., and achieve the effect of high accuracy and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

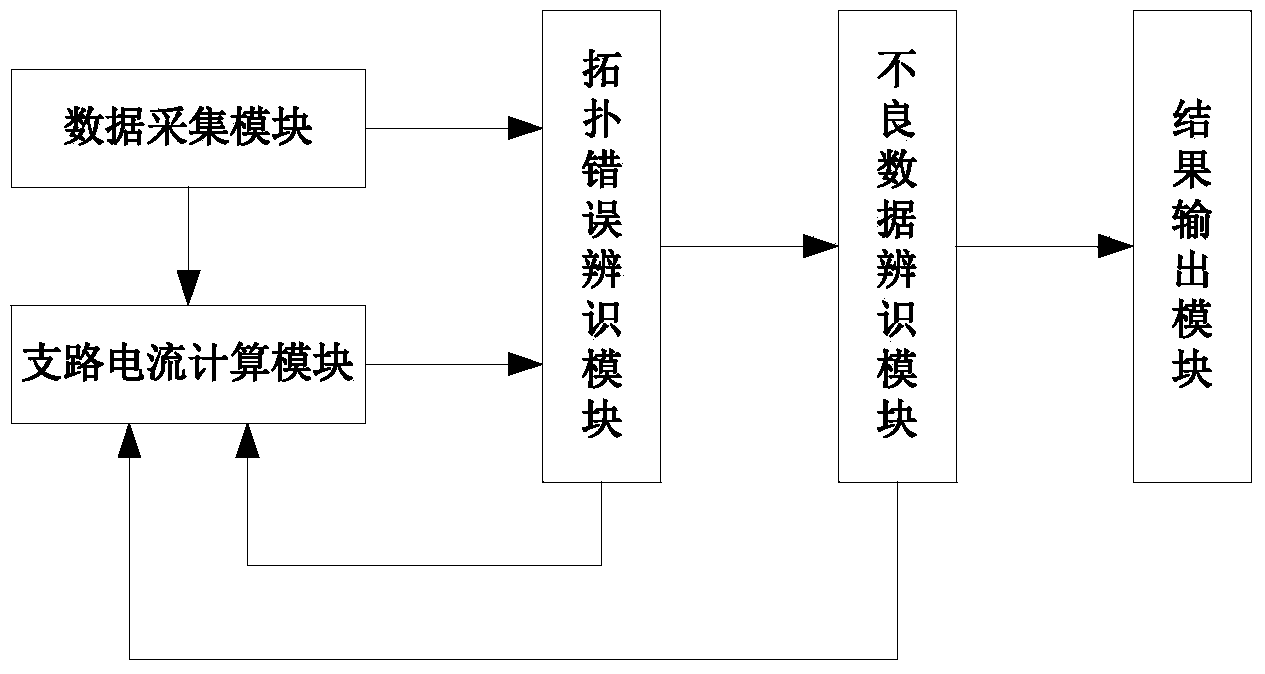

[0044] figure 1 It is the structural diagram of the network topology error identification system based on the road-loop equation provided by the present invention, such as figure 1 As shown, the network topology error identification system based on the road-loop equation includes a data acquisition module, a branch current calculation module, a topology error identification module, a bad data identification module and a result output module. Among them, the data acquisition module, the branch current calculation module, the topology error identification module, the bad data identification module and the result output module are sequentially connected, and the topology error identification module and the bad data identification module are also respectively connected with the branch current calculation module.

[0045] The data acquisition module is used to collect network structure parameters, tie switch status, circuit breaker status, branch rated current, node injection curre...

Embodiment 2

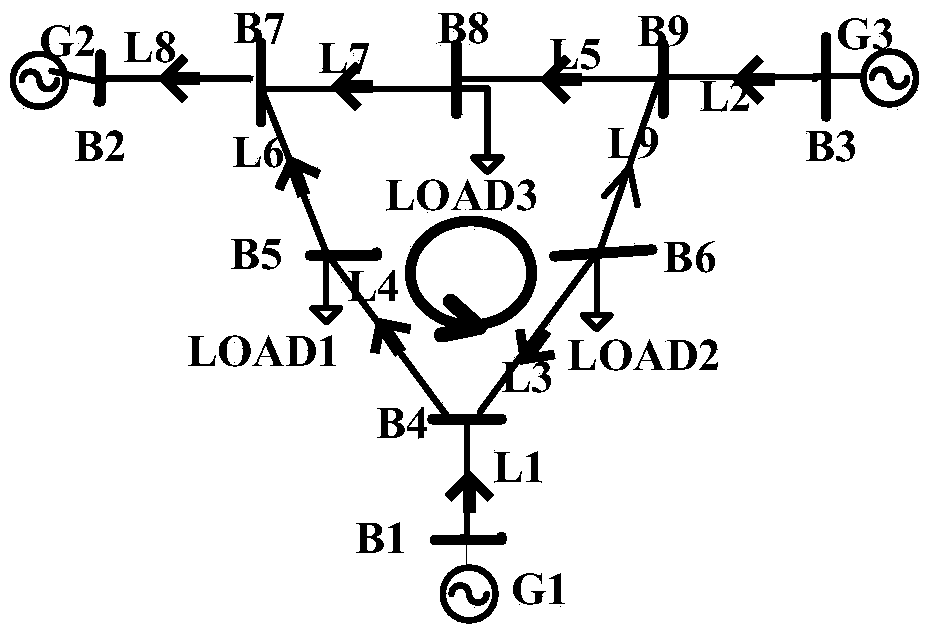

[0148] Based on PSCAD simulation software, build figure 2 The IEEE3-machine 9-node system model shown. Assume that busbars B2 and B7 are capable of switching operations. Among them, the system power supply S N =100MVA, U N =220KV, then I · LN = ( 0.223 + j 0.138 ) kA , ε 1 =(0.01785+j0.0111)kA.

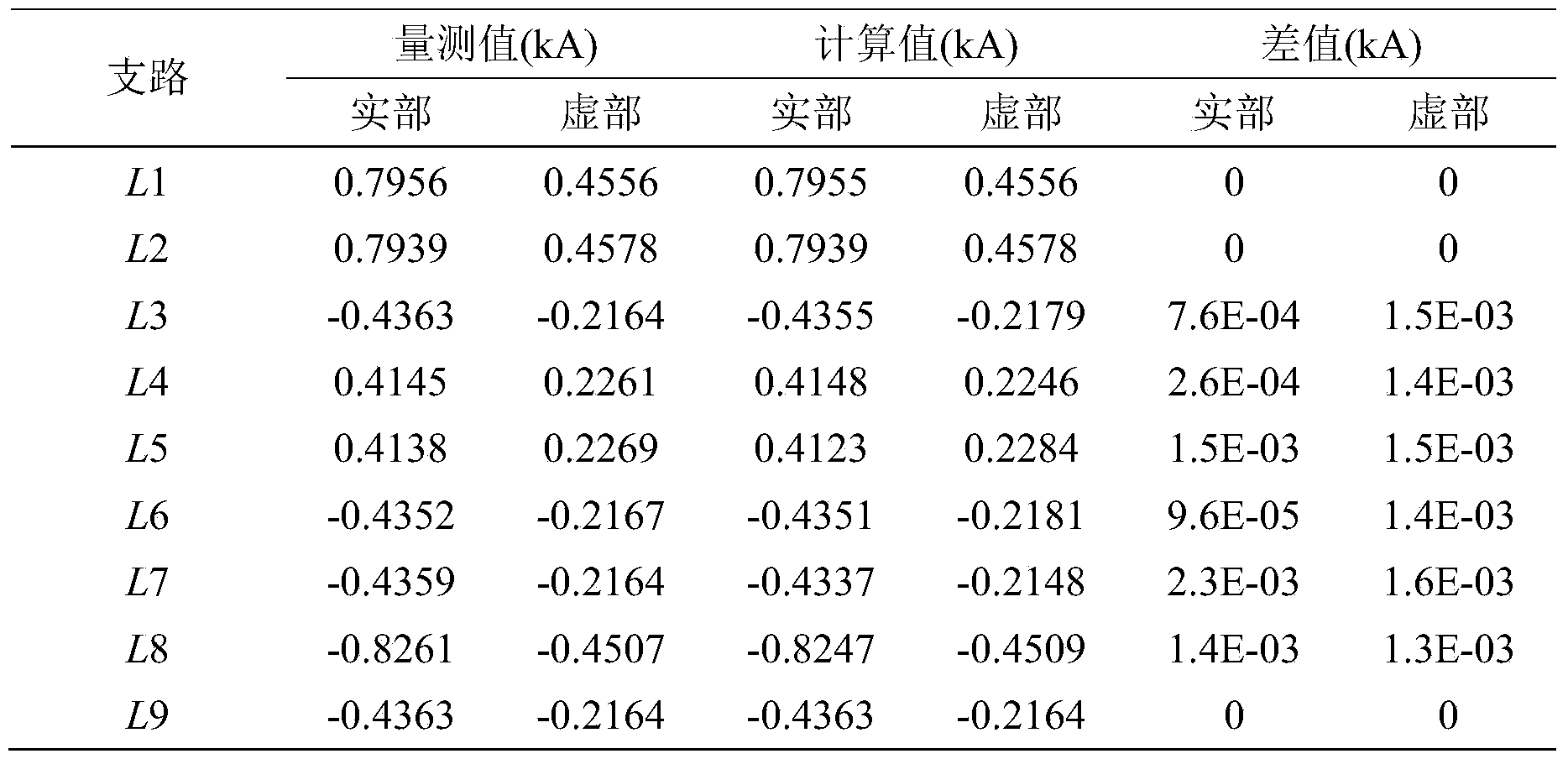

[0149] Verify the formula (5), the ground admittance of its branch is B / 2=1.623×10 -4 S, according to the above principles, the node injection current is shown in formula (11), and the loop current is i L9 =(-0.43628-j0.216385)kA, the calculation result is as follows image 3 shown.

[0150] Since the current of each branch of the system meets the set conditions, there is no topology information error and bad data.

[0151] I · ...

Embodiment 3

[0177] This embodiment uses the 10-machine 39-node system as an example, the system structure and road markings are as follows Figure 14 As shown in , the solid triangle arrows are marked as connecting branches, and the rest of the branches are tree branches. The minimum rating of the branch circuit is Therefore1 =(0.021544+j0.012933)kA. For networks with a large number of nodes and complex wiring, local topology errors can be identified. This paper only uses Figure 14 Take the two local networks marked as an example.

[0178] (1) The existence of multiple bad data.

[0179] node A local network with an end point such as Figure 15 shown. Its T and B matrices are shown in formula (22), and according to the analysis of formula (6), the injection current of the node can be the current of the other branches of the node and the equivalent value of the injection current of the node (for example, in the loop, except the influence of the current of the loop where it is loca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More