Cascode circuit

A circuit and cascading technology, applied in circuits, electronic switches, electrical components, etc., to improve cost/performance and minimize internal inductance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

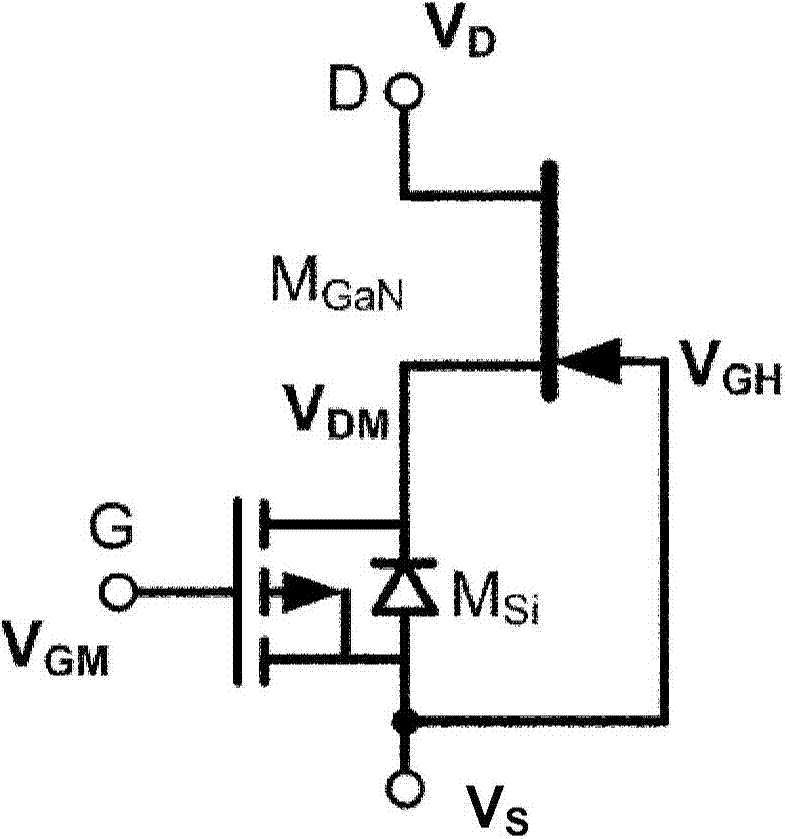

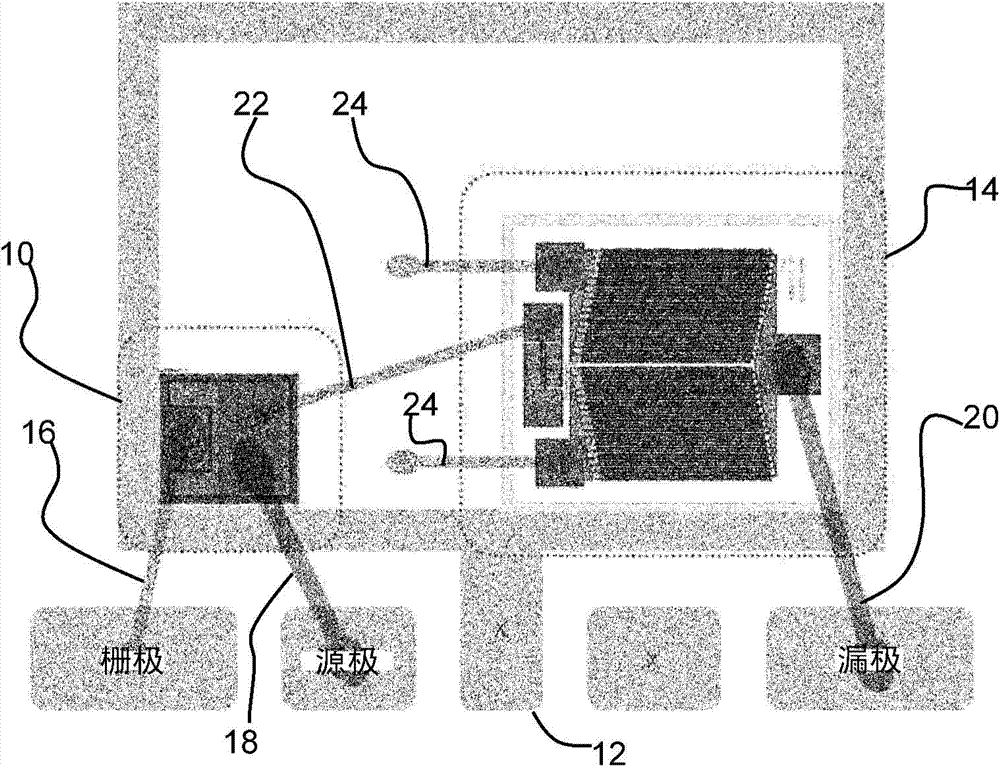

[0054] The present invention provides a cascode circuit structure in which low-voltage MOSFETs and depletion-mode power devices are mounted on a substrate (e.g., a ceramic substrate), which can then be provided in a semiconductor package (or sold separately to those wishing to customers who produce their own modules). Only GaN devices will be referred to below, but the same approach applies to SiC devices or other depletion mode devices. The present invention is concerned with high electron mobility transistors or junction gate field effect transistors.

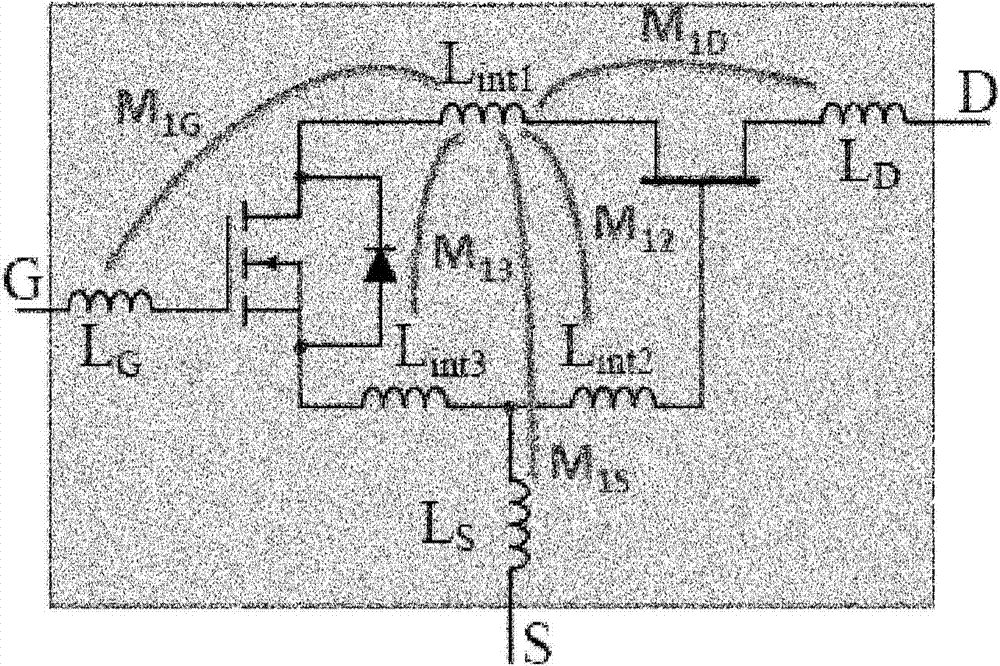

[0055] Figure 4 A circuit example of the present invention is shown. shows the layout of the components, but the circuit corresponds to figure 1 (although as noted below in Figure 4 optional additional components are shown).

[0056] The circuit has a first gallium nitride or silicon carbide field effect transistor 40 with a drain D for connection to the high power supply line. The drain of the second silicon MOSFET 4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More