Nine-stage ten-bit pipelined ADC circuit

A pipeline and circuit technology, applied in the direction of analog/digital conversion calibration/test, analog-to-digital converter, etc., can solve problems such as capacitance mismatch error, comparator offset, switch nonlinearity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

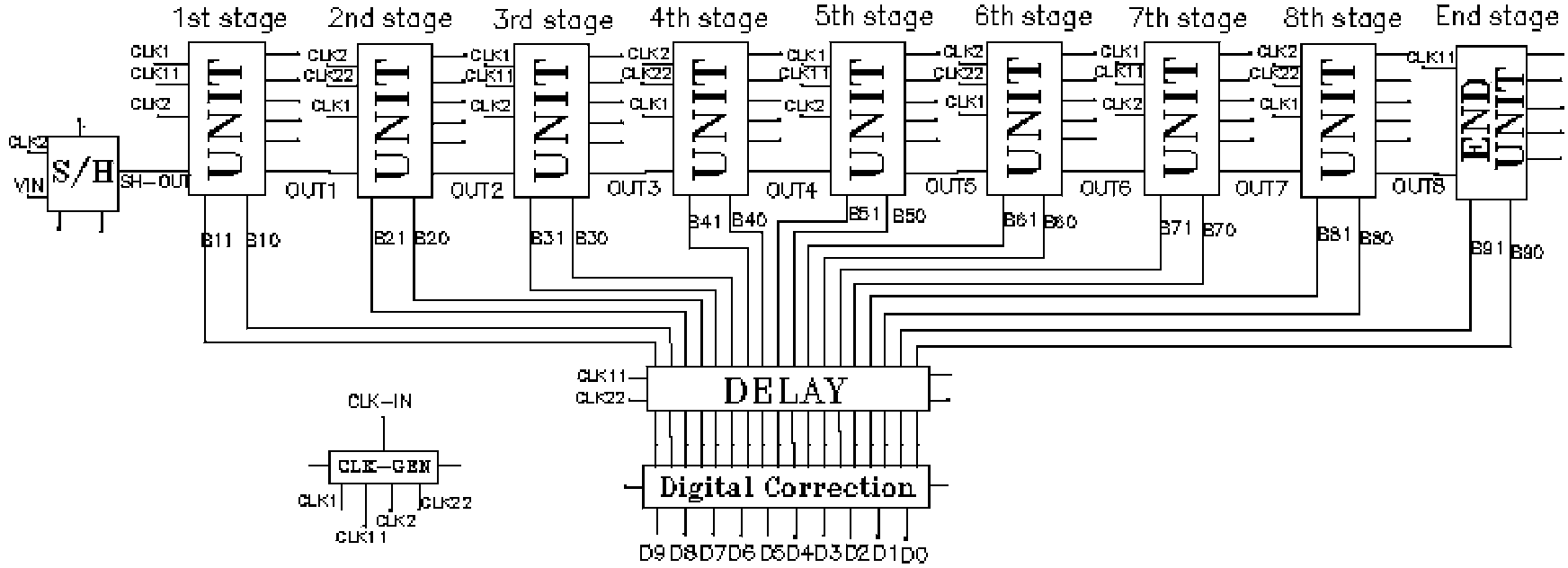

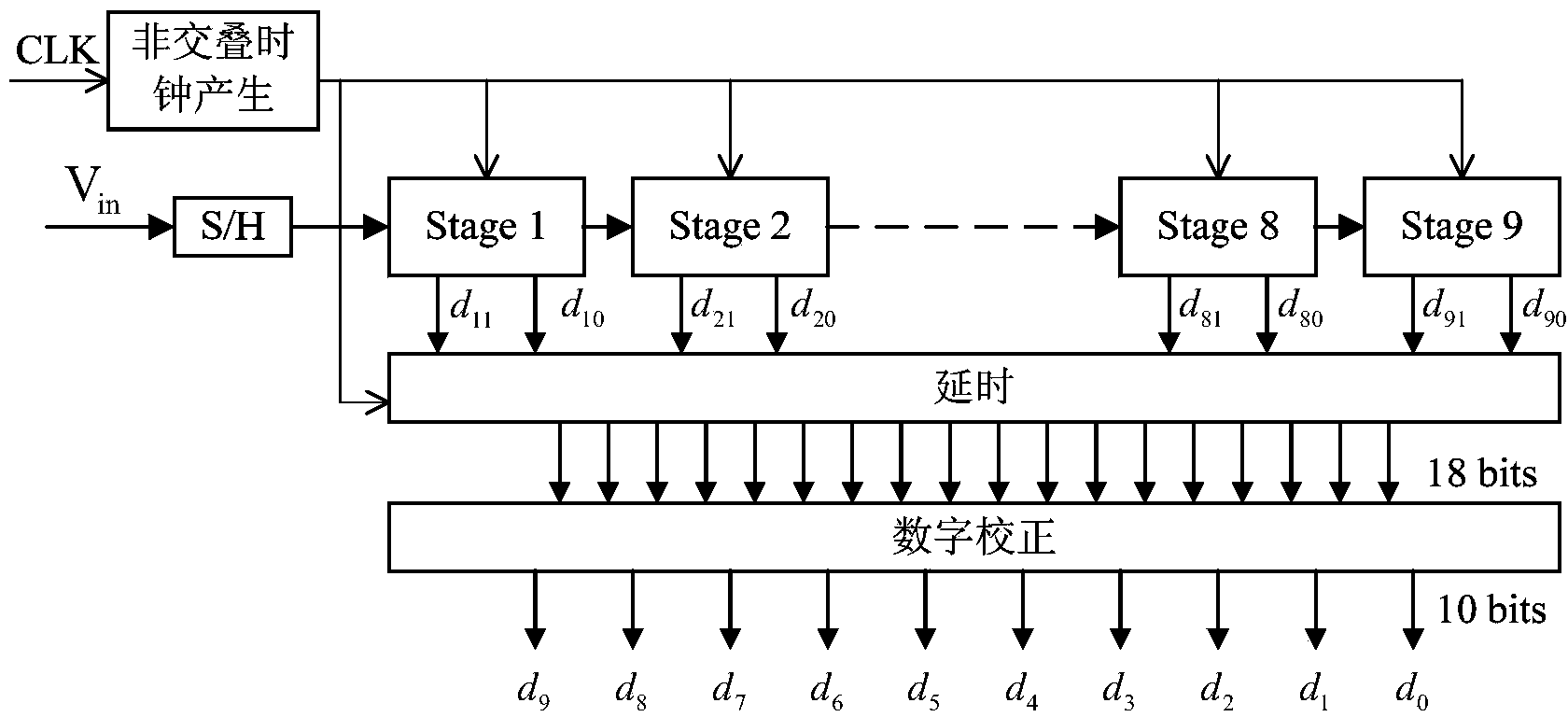

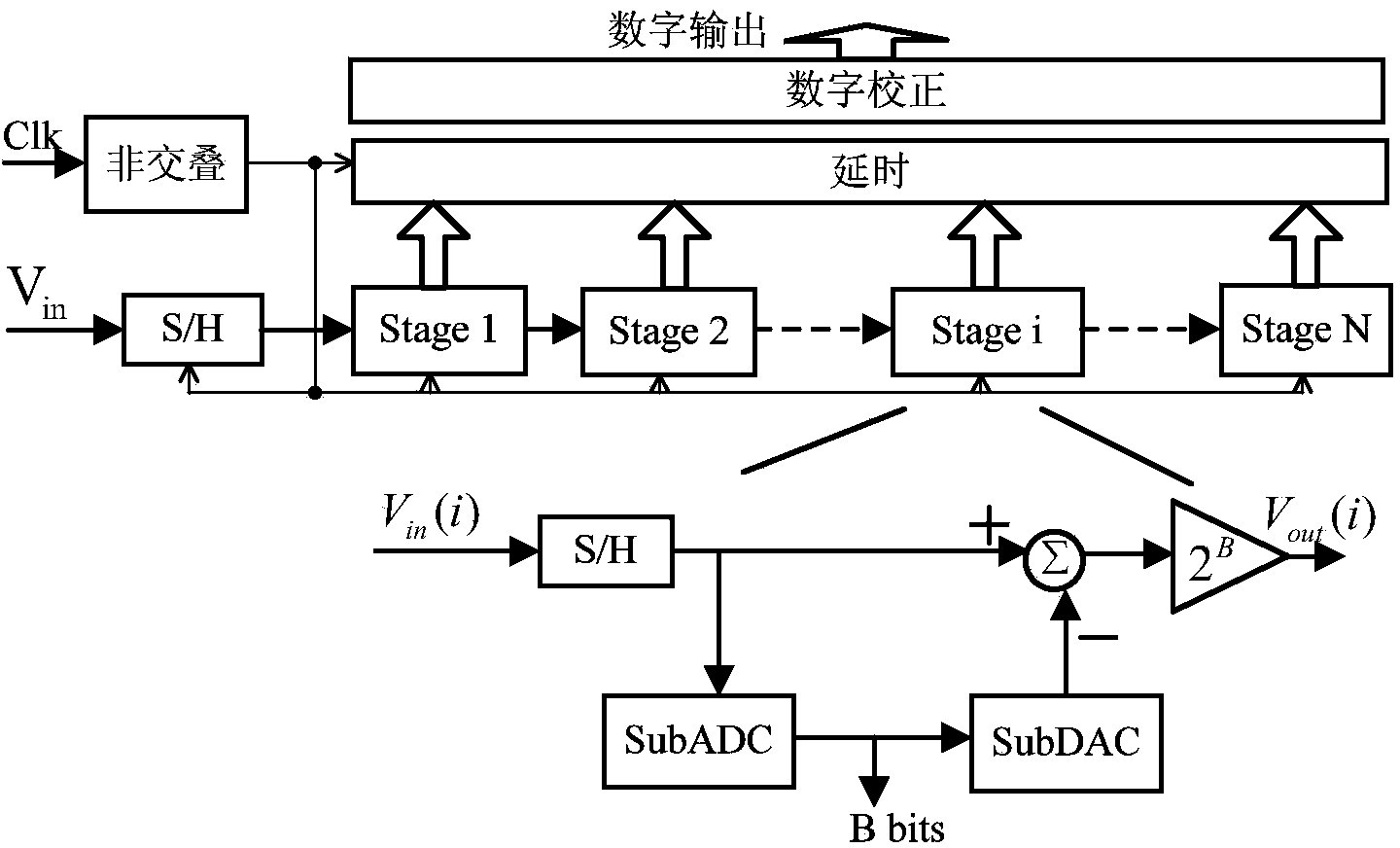

[0043] The pipeline ADC involved in the present invention adopts the pipeline ADC under 0.6μmBiCMOS technology, the pipeline ADC system adopts 2.5V power supply, the input range of the analog signal is -1V-1V, and the conversion rate is 2M / s. The pipeline ADC includes a sampling and holding circuit, a 9-level 10-bit pipeline unit processing module, an external clock generation circuit module, and a delay and digital correction circuit module.

[0044] The overall circuit design of the system is as figure 1 shown. The input analog quantity VIN passes through the sample and hold circuit (S / H), and is processed by 9-stage pipeline units. After the two-digit digital output of each stage unit is "aligned" in time by the delay module (DELAY), it is input in parallel to the digital correction module ( Digital Correction), generating 10-bit pipeline ADC output D9-D0. Among them, the external 4MHz clock CLK-IN generates 4-phase 2MHz non-overlapping clock output through the non-overla...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More