Oxide thin-film transistor with bottom-gate structure and manufacturing method thereof

A technology of oxide thin films and oxide semiconductors, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve the problems of TFT device failure and inability to form channel regions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

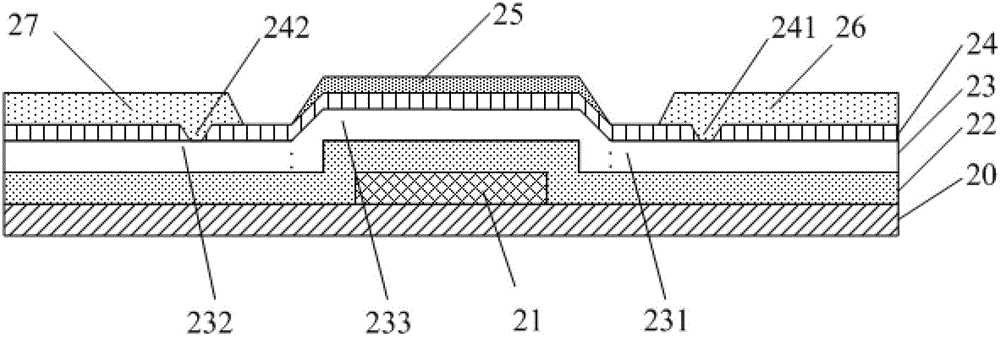

[0046] An embodiment of the present invention provides an oxide TFT with a bottom-gate and bottom-contact structure. The structure of the TFT is as follows: figure 2As shown, it includes: a substrate 20; a gate 21 formed on the substrate 20; a gate insulating layer 22 formed on the gate 21 and the substrate 20 and covering the gate 21; an active layer 23 formed of an oxide The semiconductor is formed on the gate insulating layer 22, including a source region 231, a drain region 232, and a channel region 233 corresponding to the gate 21. The source region 231 and the drain region 232 are doped with hydrogen ions; the hydrogen permeable layer 24 is formed on the On the source layer 23, it is used to control the amount of doped hydrogen ions in the source region 231 and the drain region 232; the etch barrier layer 25 is formed on the hydrogen permeable layer 24 at a position corresponding to the gate 21, and is used to prevent hydrogen ions from entering The channel region 233; ...

Embodiment 2

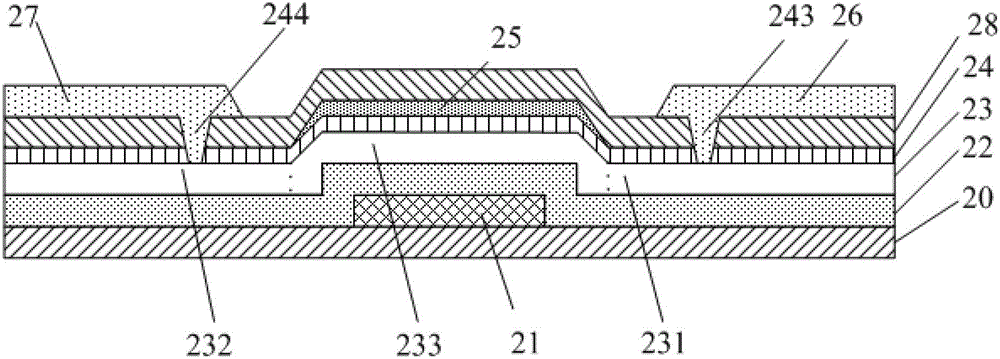

[0088] An embodiment of the present invention provides an oxide TFT with a bottom-gate top-contact structure. The structure of the TFT is as follows: Figure 15As shown, it includes: a substrate 20; a gate 21 formed on the substrate 20; a gate insulating layer 22 formed on the gate 21 and the substrate 20 and covering the gate 21; an active layer 23 formed of an oxide The semiconductor is formed on the gate insulating layer 22, including a source region 231, a drain region 232, and a channel region 233 corresponding to the gate 21. The source region 231 and the drain region 232 are doped with hydrogen ions; the hydrogen permeable layer 24 is formed on the On the source layer 23, it is used to control the amount of doped hydrogen ions in the source region 231 and the drain region 232; the etch barrier layer 25 is formed on the hydrogen permeable layer 24 at a position corresponding to the gate 21, and is used to prevent hydrogen ions from entering Channel region 233; source 26 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More