JFET (junction field-effect transistor) device and manufacturing method thereof

A device and substrate technology, which is applied in the field of JFET devices and its manufacturing, can solve the problems of not being able to meet the application of constant current source circuits and low cost, and achieve the effect of good constant current characteristics and small constant current accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

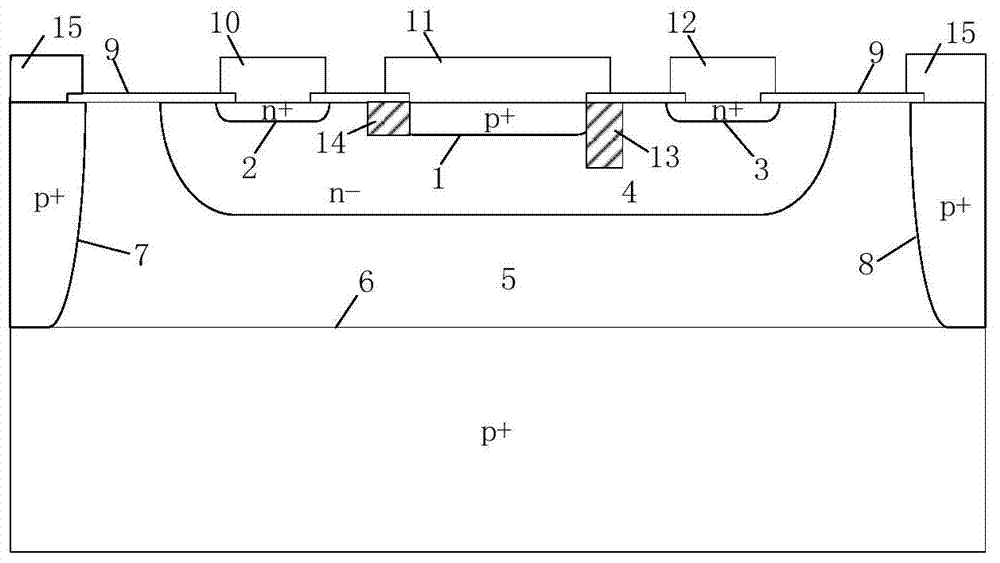

[0037] In this example, a shallow trench auxiliary layer is formed by digging a trench and filling a dielectric material layer, specifically:

[0038] Step 1: Select an NTD single wafer with fewer defects. The thickness of the single wafer ranges from 400 to 700 μm, and the resistivity ranges from 0.001 to 0.005Ω·cm. After marking, cleaning, and drying, it is ready to use, such as Figure 6 shown;

[0039] Step 2: grow an epitaxial layer on the surface of the silicon wafer, the temperature range is 1100 ° C ~ 1150 ° C, the thickness is 5 ~ 25 μ m, and the resistivity is 8 ~ 12 Ω·cm, such as Figure 7 shown;

[0040] Step 3: Thermally grow oxide layer with a thickness of

[0041] The fourth step: a photolithography, after the photolithography, the P+ isolation region is implanted, and the first P-type isolation region and the second P-type isolation region are formed on both sides of the epitaxial layer, such as Figure 8 Shown; Specifically, the glue-removing implant is u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More