Semiconductor structure and forming method thereof

A semiconductor and forming layer technology, which is applied in the direction of semiconductor devices, semiconductor/solid device manufacturing, semiconductor/solid device components, etc., can solve problems such as poor electrical performance, delamination, electromigration failure, etc., to improve adhesion, Effect of avoiding delamination, improving yield and electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

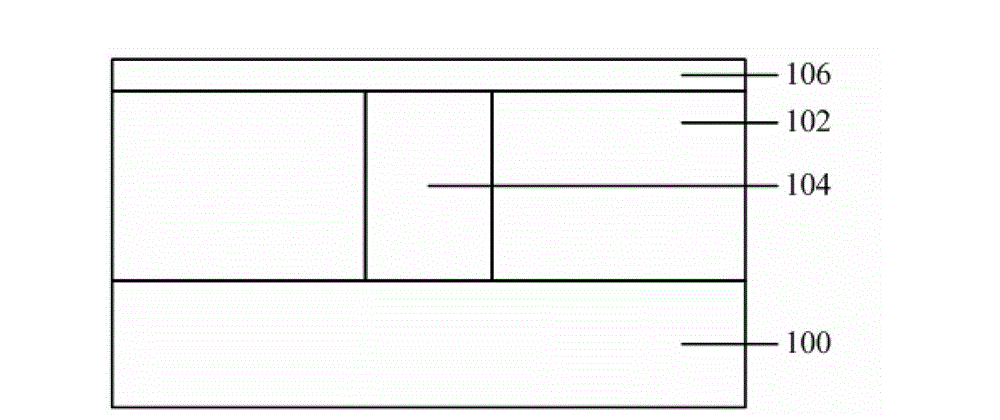

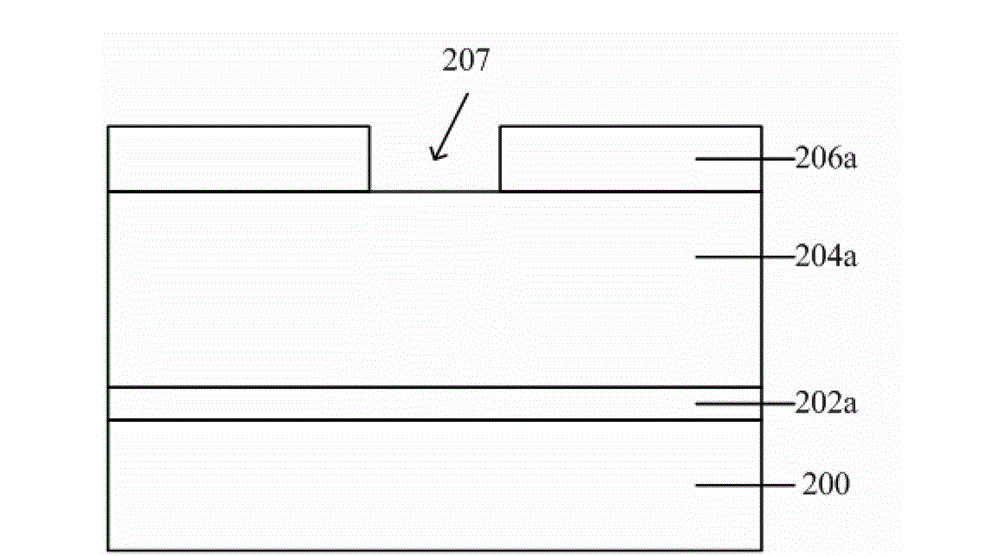

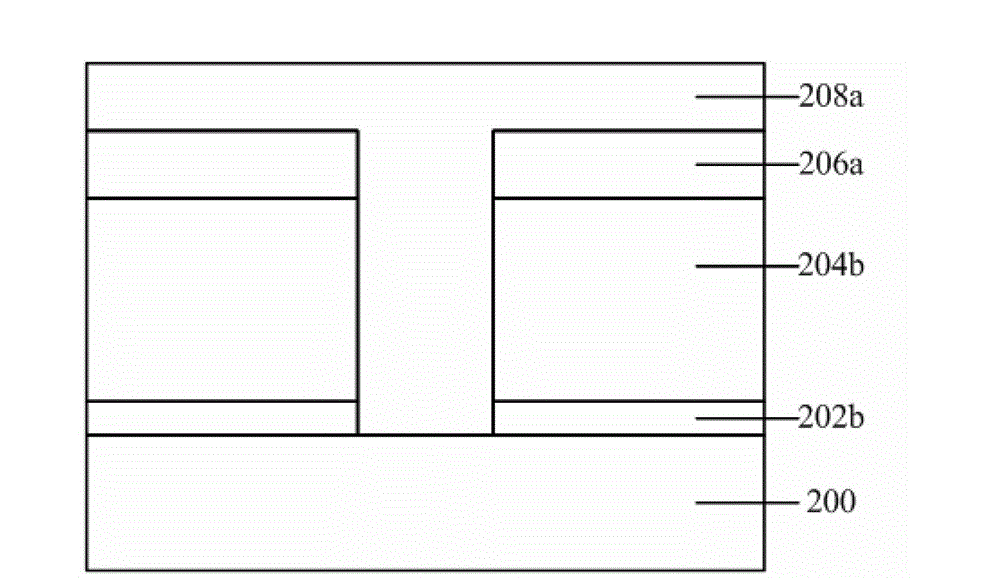

[0035] As mentioned in the background technology section, in the copper interconnection structure formed by the existing technology, the barrier layer is easily peeled off from the interlayer dielectric layer and the copper interconnection line, the yield of the formed copper interconnection structure is low, and electromigration is prone to occur invalidated.

[0036] The inventors have found through research that the barrier layer in the copper interconnection structure is easy to peel off from the interlayer dielectric layer and the copper interconnection because: the copper interconnection is a conductive material, the barrier layer is an insulating material, and the copper interconnection and the barrier layer Poor adhesion due to different materials, resulting in the barrier layer being easily peeled off from the copper interconnect. Similarly, when an insulating layer is formed on a metal layer of other materials, the above-mentioned problems must also exist.

[0037] ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More