Method for manufacturing PMOS transistor

A manufacturing method and transistor technology, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of poor performance of PMOS transistors and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] After research, the inventor found that the reasons for the poor performance of PMOS transistors are:

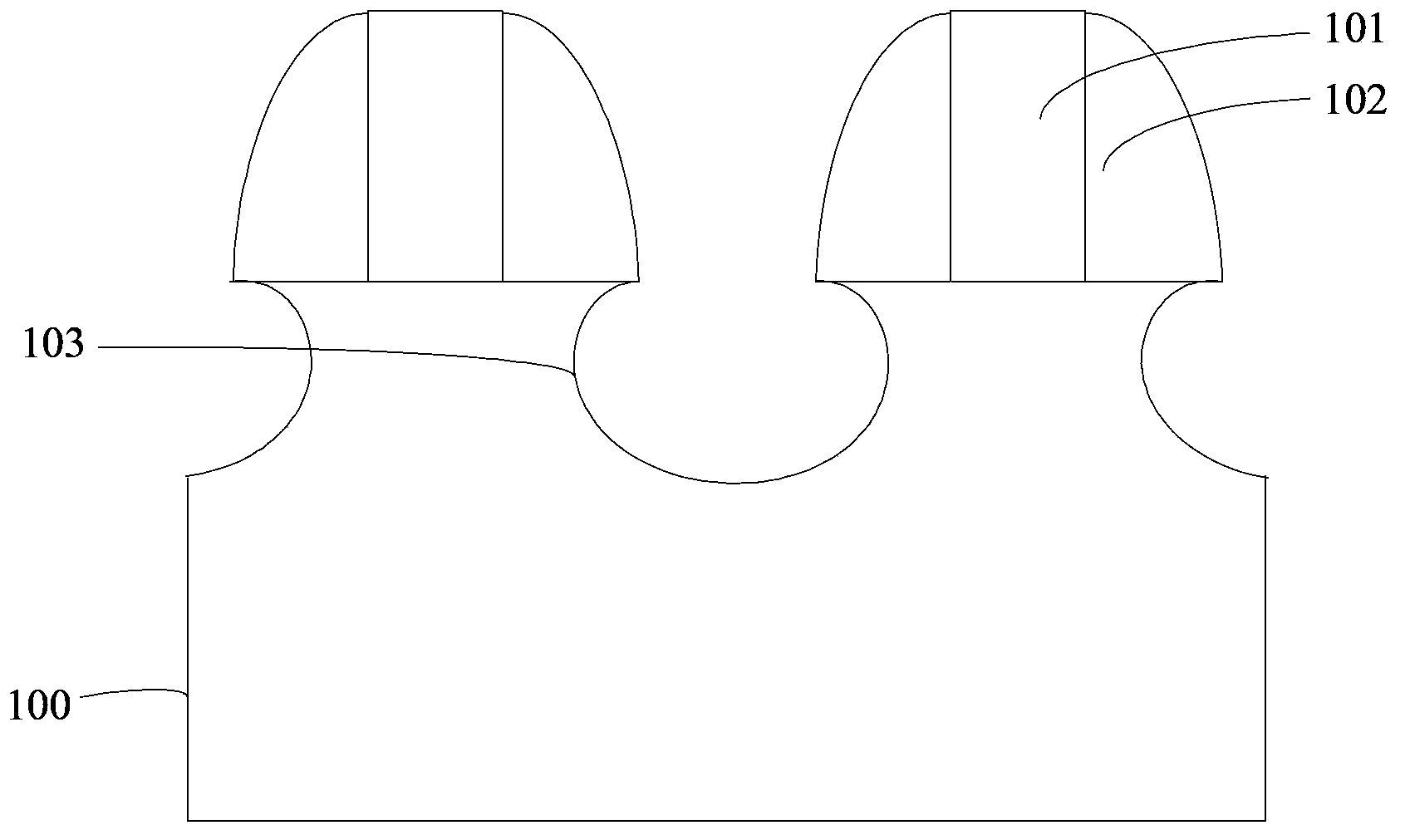

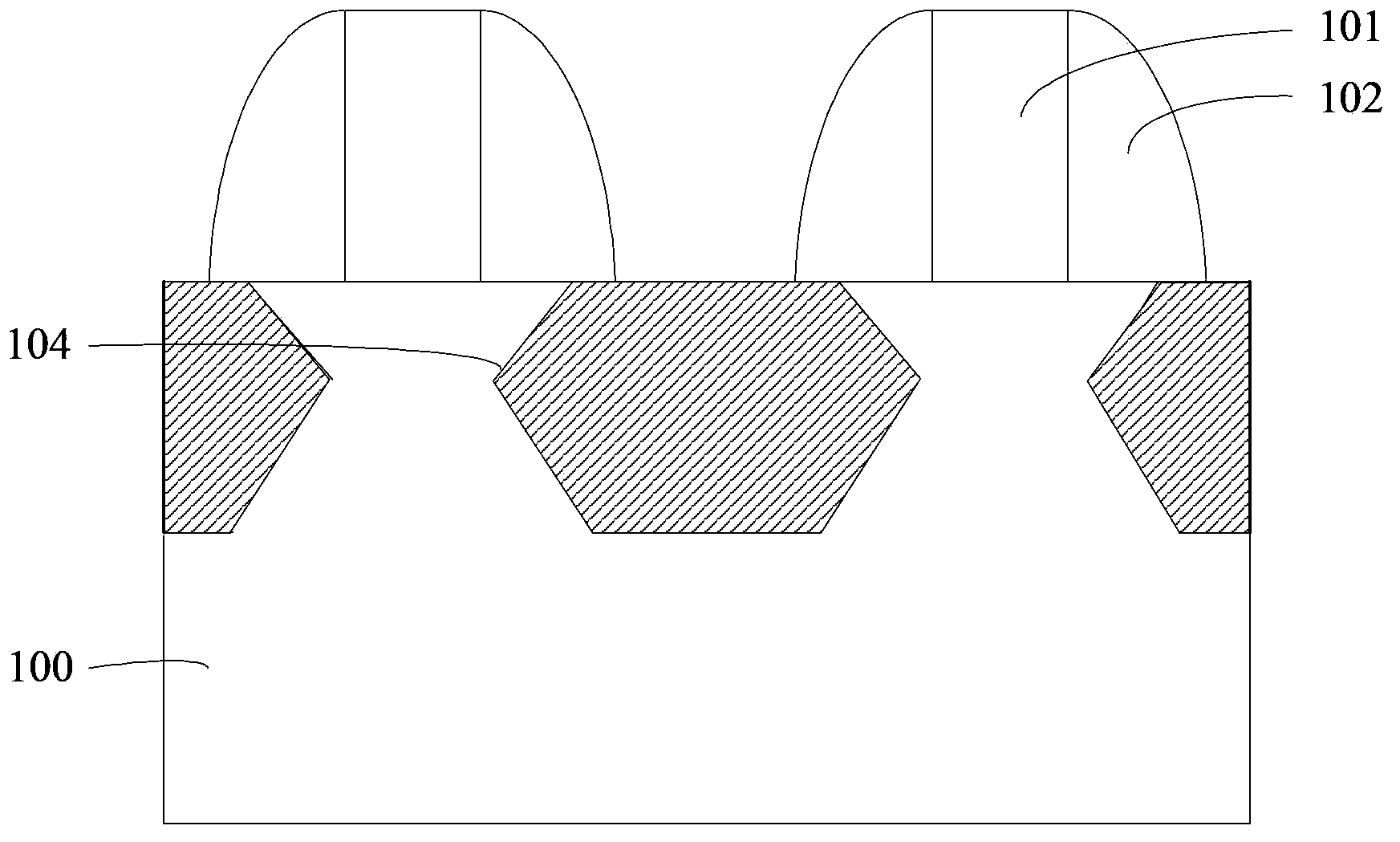

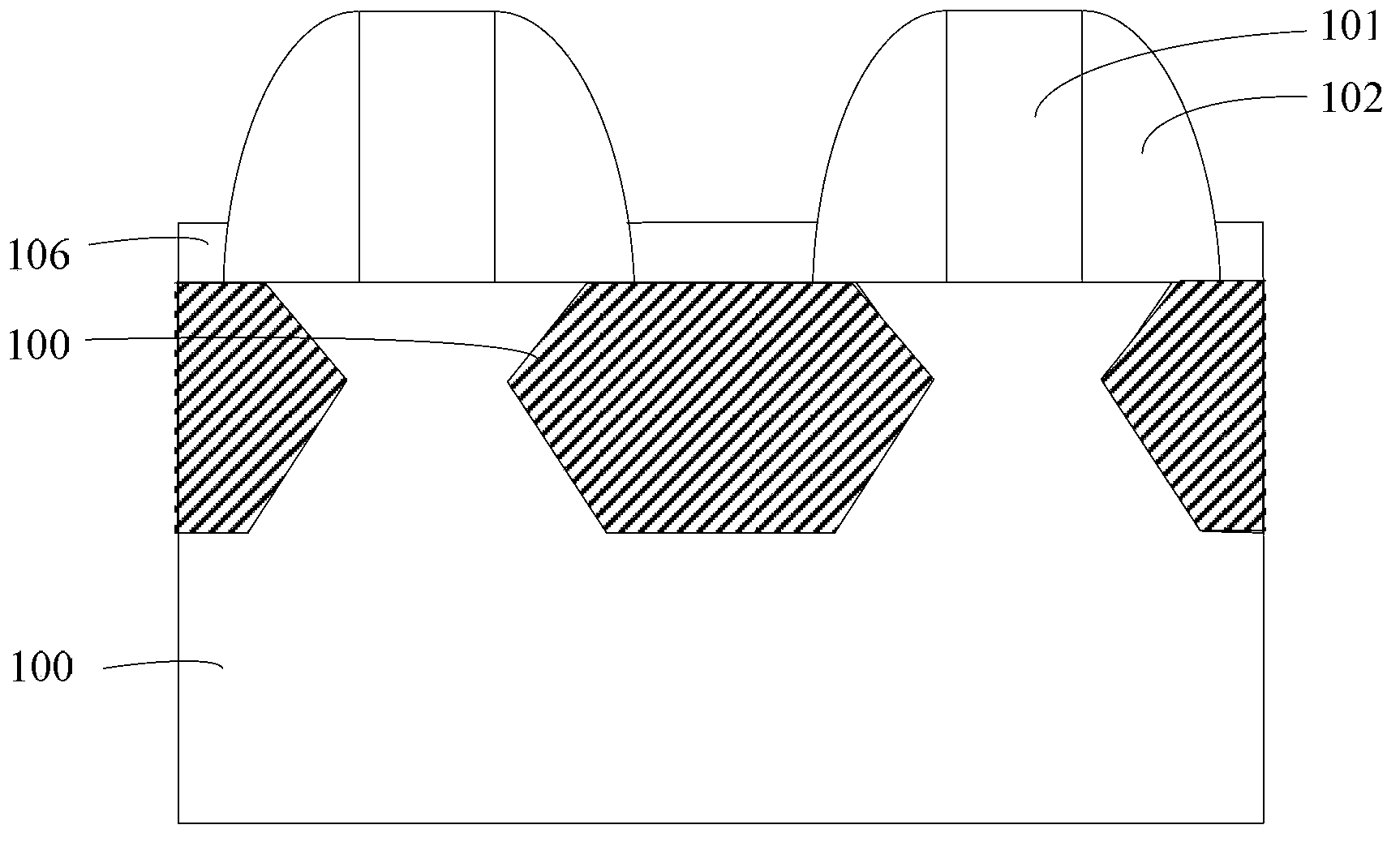

[0041] refer to figure 1 , the surface of the substrate 100 is easily oxidized in air to form an oxide (not shown in the figure), and the bottom of the sacrificial spacer 102 has the oxide. continue to refer figure 1 After the bowl-shaped groove 103 is formed, the surface of the bowl-shaped groove 103 will be oxidized in the air to form oxides. The dilute hydrofluoric acid solution can clean the oxides in the bowl-shaped groove 103 . During the process of cleaning the oxide in the bowl-shaped groove 103 , part of the oxide at the bottom of the sacrificial spacer 102 will also be removed, resulting in a gap between the sacrificial spacer 102 and the substrate. refer to figure 2 , because there is a gap between the sacrificial sidewall 102 and the substrate, when the bowl-shaped groove is etched to form the sigma-shaped groove 104, the substrate at the position o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More