A kind of semiconductor device and its forming method

A semiconductor and device technology, applied in the field of semiconductor devices and their manufacturing processes, can solve problems such as charge balance deterioration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

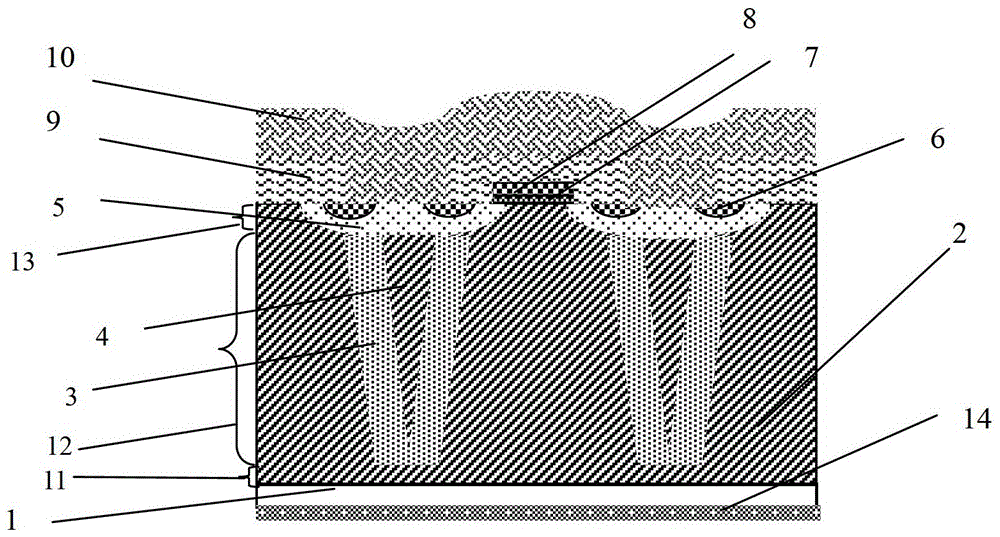

Embodiment 1

[0050] Such as Figure 3a-Figure 3f Shown, the technological process of this embodiment 1 is specifically as follows:

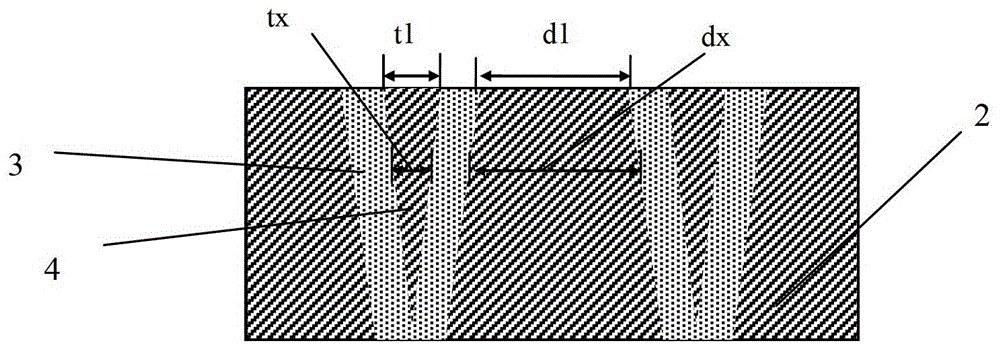

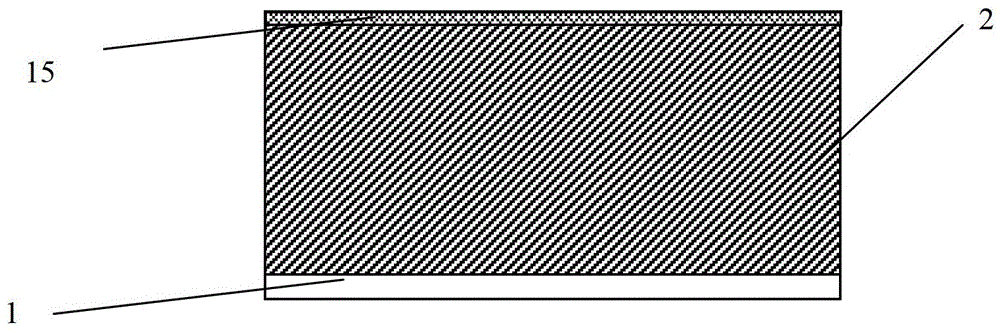

[0051] 1) The first semiconductor layer 2 and the dielectric layer 15 are sequentially grown on the semiconductor substrate 1, the first semiconductor layer 2 and the semiconductor substrate 1 have the first conductivity type, and the first semiconductor layer 2 and the semiconductor substrate 1 are made of Si, C, Ge , SiC, GaN or SiGe single crystal material, a typical first semiconductor layer 2 is an N-type silicon epitaxial layer, a typical semiconductor substrate 1 is an N-type silicon substrate, and the carrier concentration of the semiconductor substrate 1 is greater than that of the first semiconductor layer 2; the thickness of the first semiconductor layer 2 is 10-100 microns; the dielectric layer 15 is at least one of silicon oxide, silicon nitride or silicon oxynitride (see Figure 3a );

[0052] 2) Trench etching. A groove 16 is etched inside t...

Embodiment 2

[0068] The difference between Embodiment 2 and Embodiment 1 is that the conductivity types are opposite. In Embodiment 2, the first conductivity type is P-type, and the second conductivity type is N-type. That is, the semiconductor substrate 1 , the first semiconductor layer 2 , and the third semiconductor layer 4 in Embodiment 2 are P-type, the second semiconductor layer 3 is N-type, the base region 5 is N-type, and the source region 6 is P-type.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More