Patents

Literature

36results about How to "Reduce the difficulty of formation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

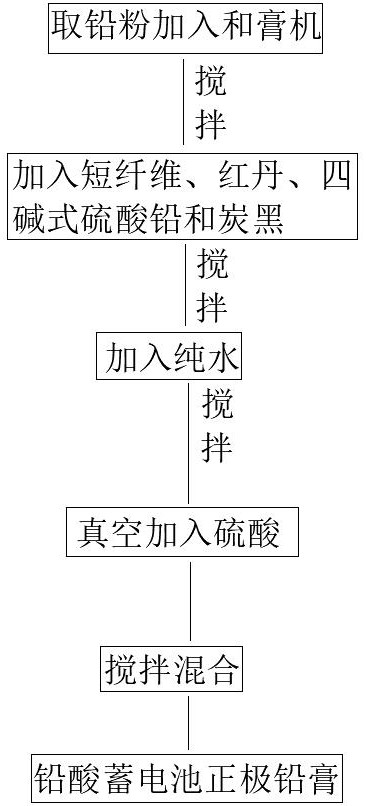

Positive lead plaster for lead-acid storage battery and preparation method of positive lead plaster

ActiveCN103762358APromote formationReduce the difficulty of formationCell electrodesPolyesterSulfuric acid

The invention discloses positive lead plaster for a lead-acid storage battery and a preparation method of the positive lead plaster. The positive lead plaster is characterized by consisting of the following raw materials by weight percent: 7 to 10 percent of 1.4g / ml dilute sulfuric acid, 8 to 12 percent of deionized water, 5 to 20 percent of red lead, 0.1 to 0.4 percent of colloid graphite, 0.1 to 0.3 percent of stannous sulfate, 0.1 to 0.3 percent of anhydrous sodium sulfate, 0.2 to 0.5 percent of 4BS, 0.1 to 0.3 percent of diantimony trioxide, 0.05 to 0.2 percent of polyester short fibers, and the balance being lead powder. After the lead plaster which is prepared by utilizing the formula and the preparation method is prepared into the storage battery, the storage battery has the characteristics of high primary capacity, long service life, good low-temperature performance and good charging capacity.

Owner:江苏海宝电池科技有限公司

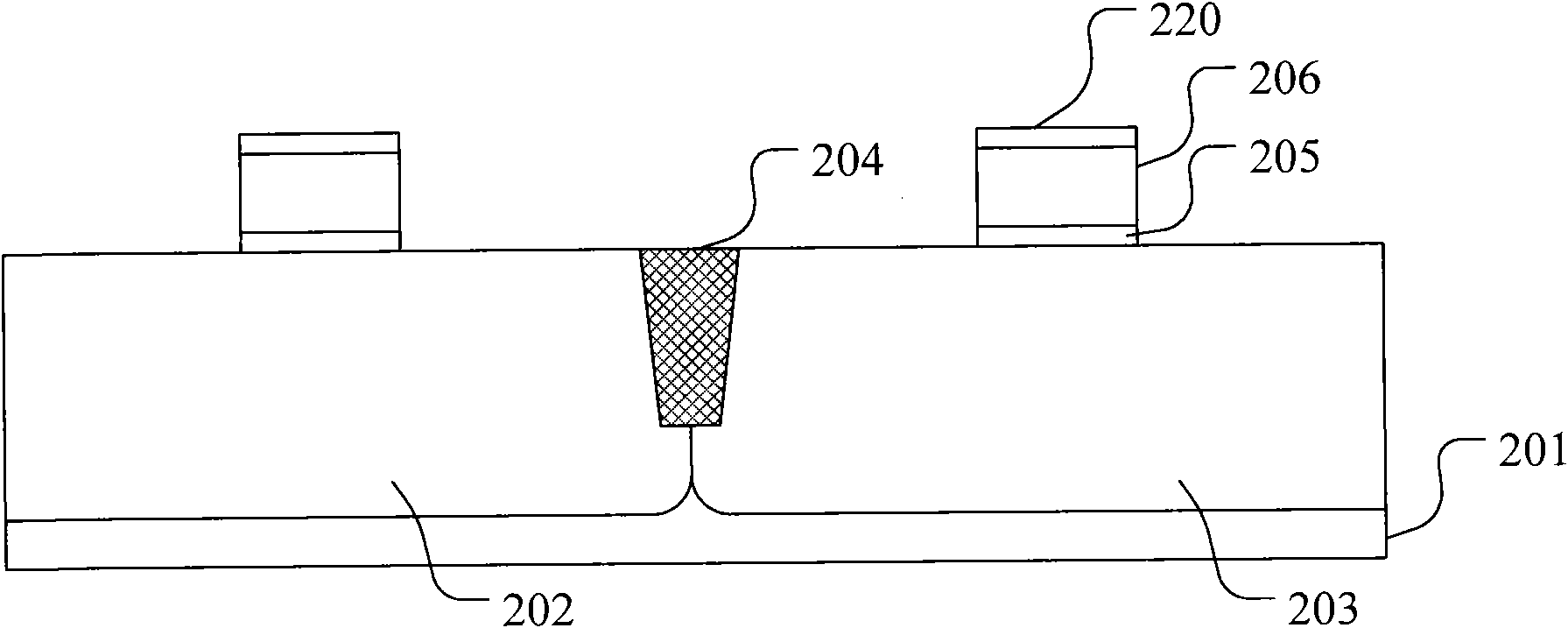

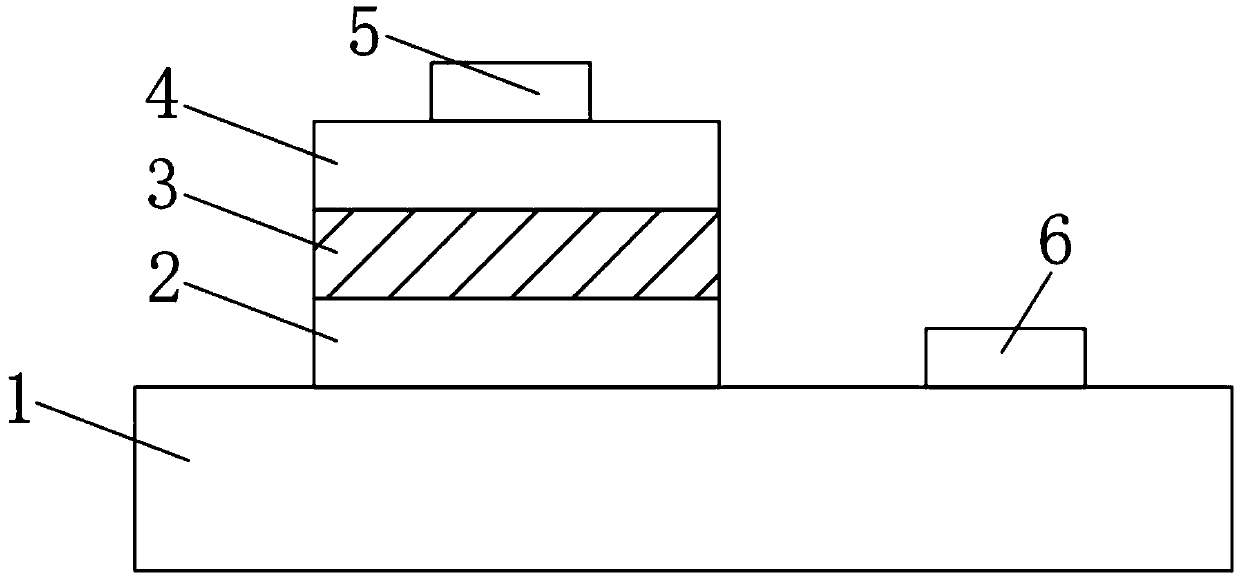

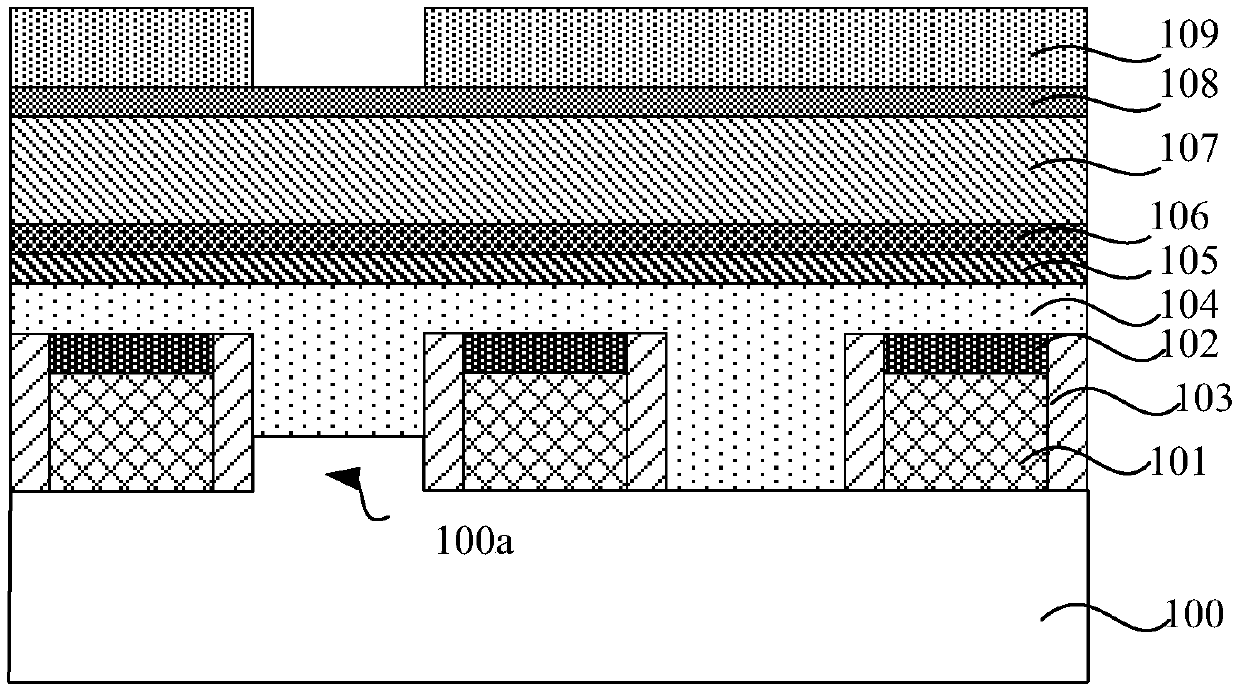

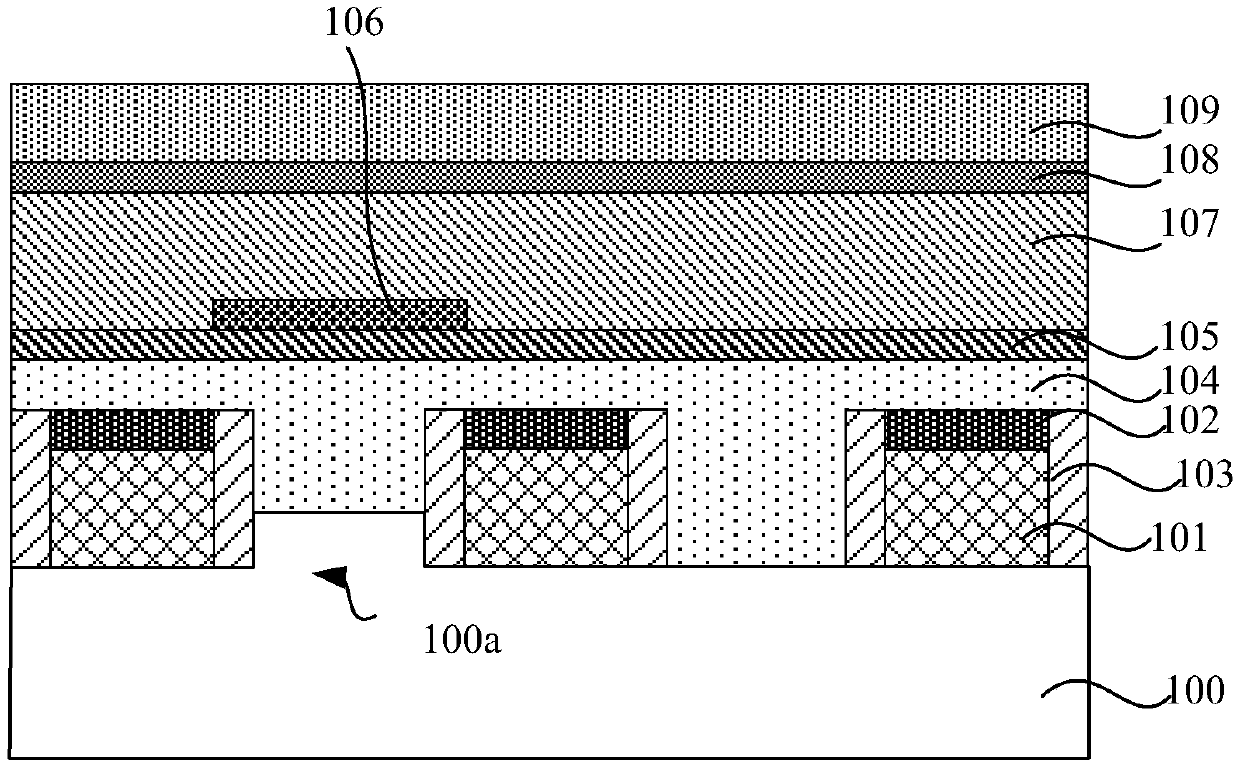

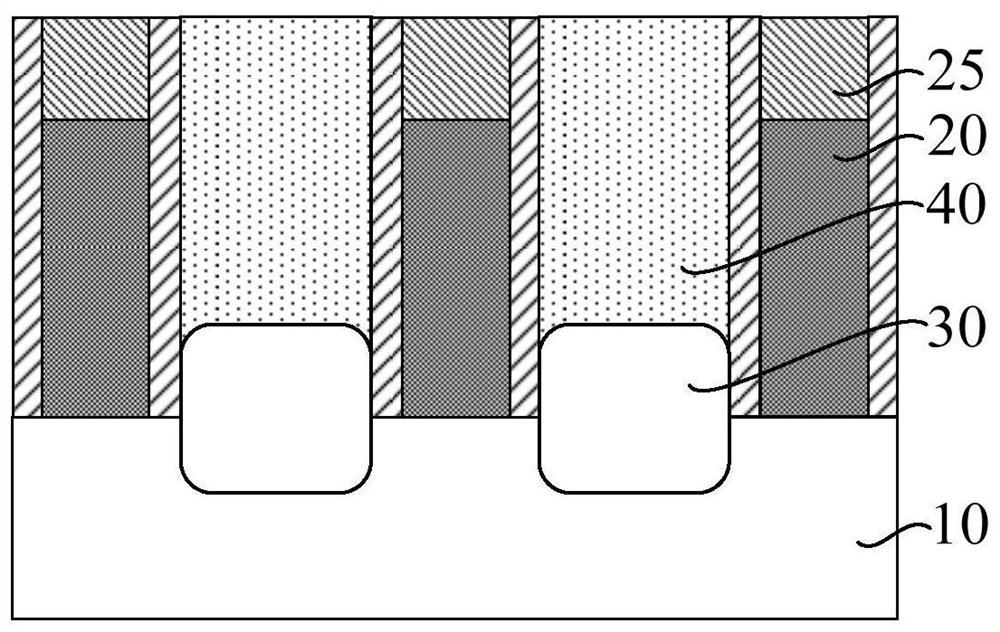

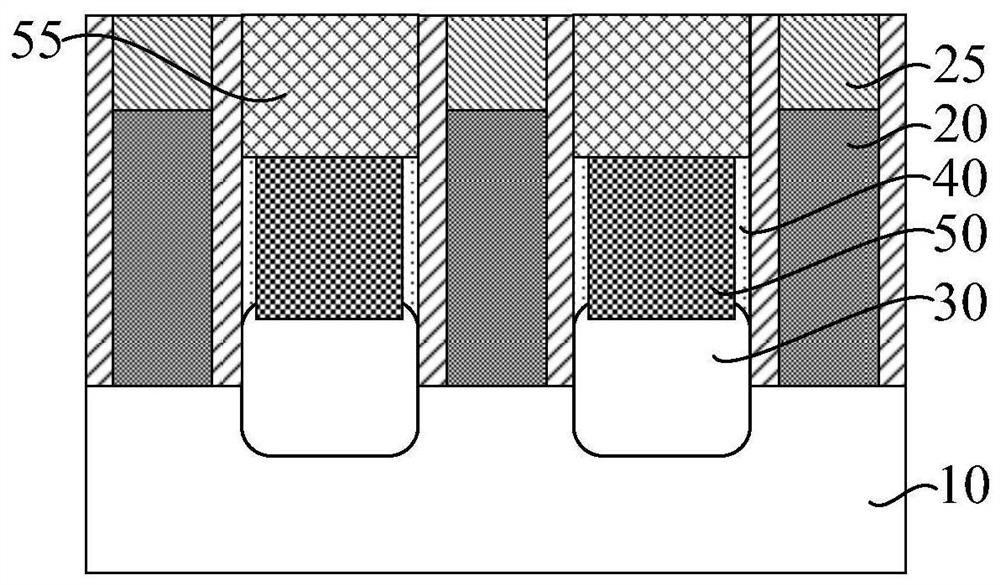

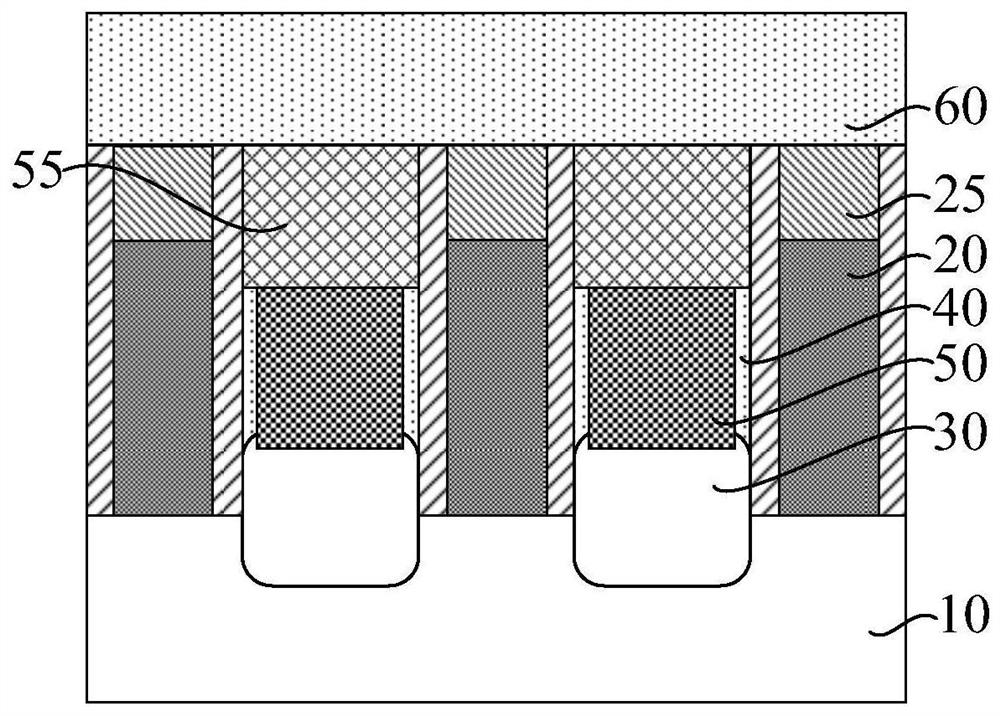

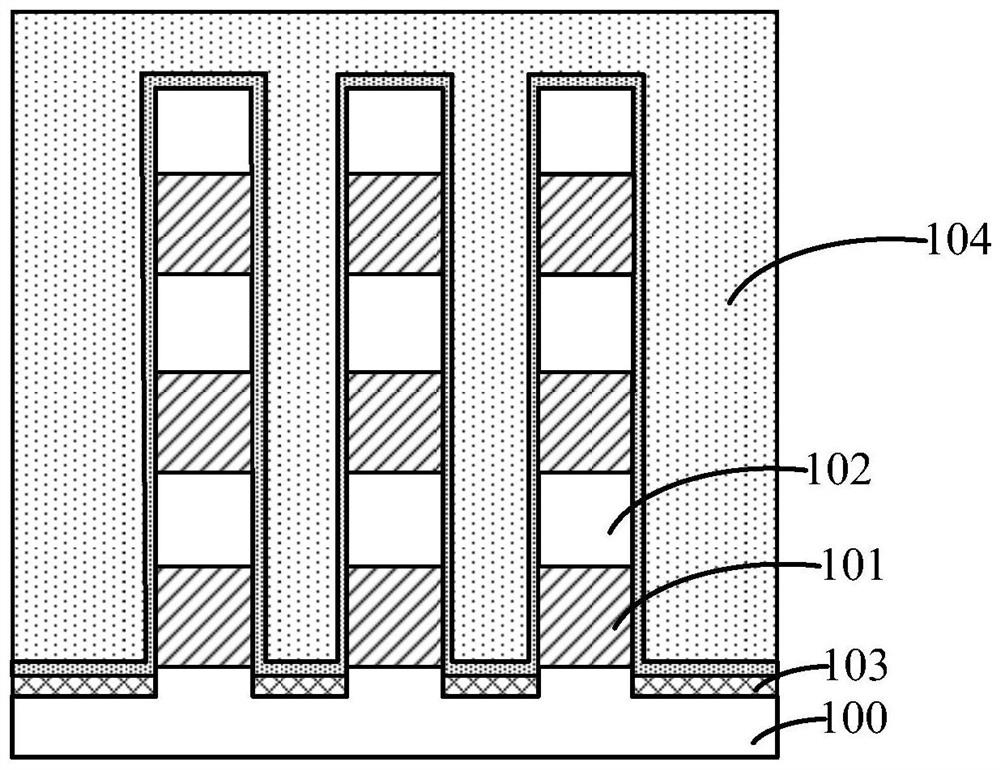

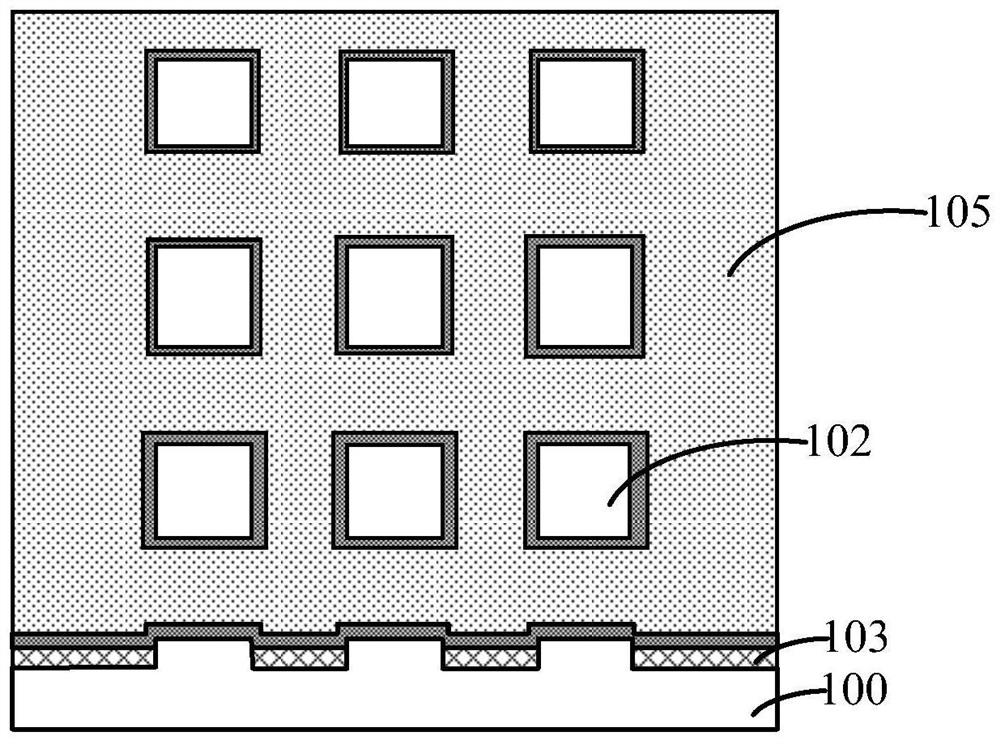

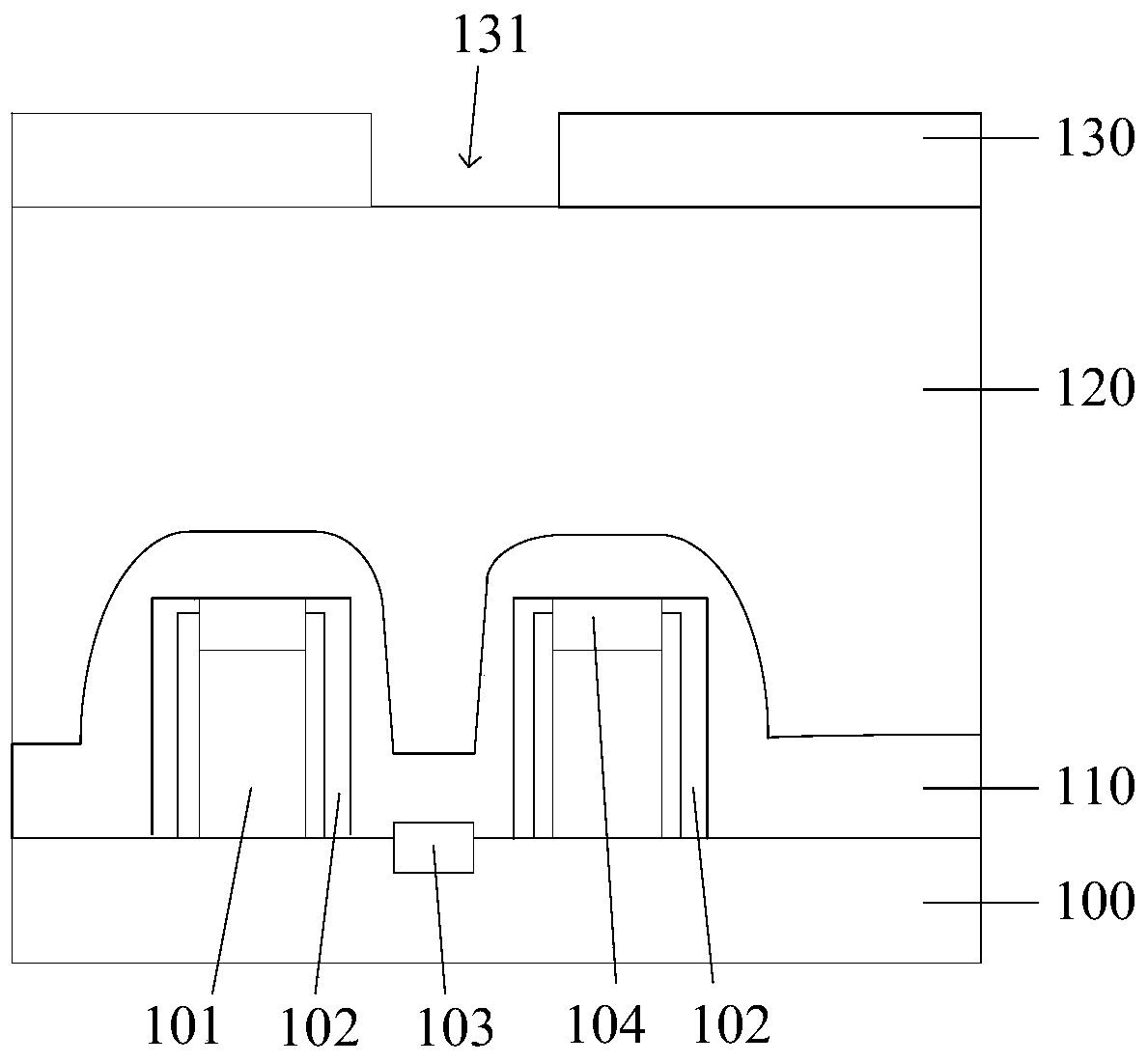

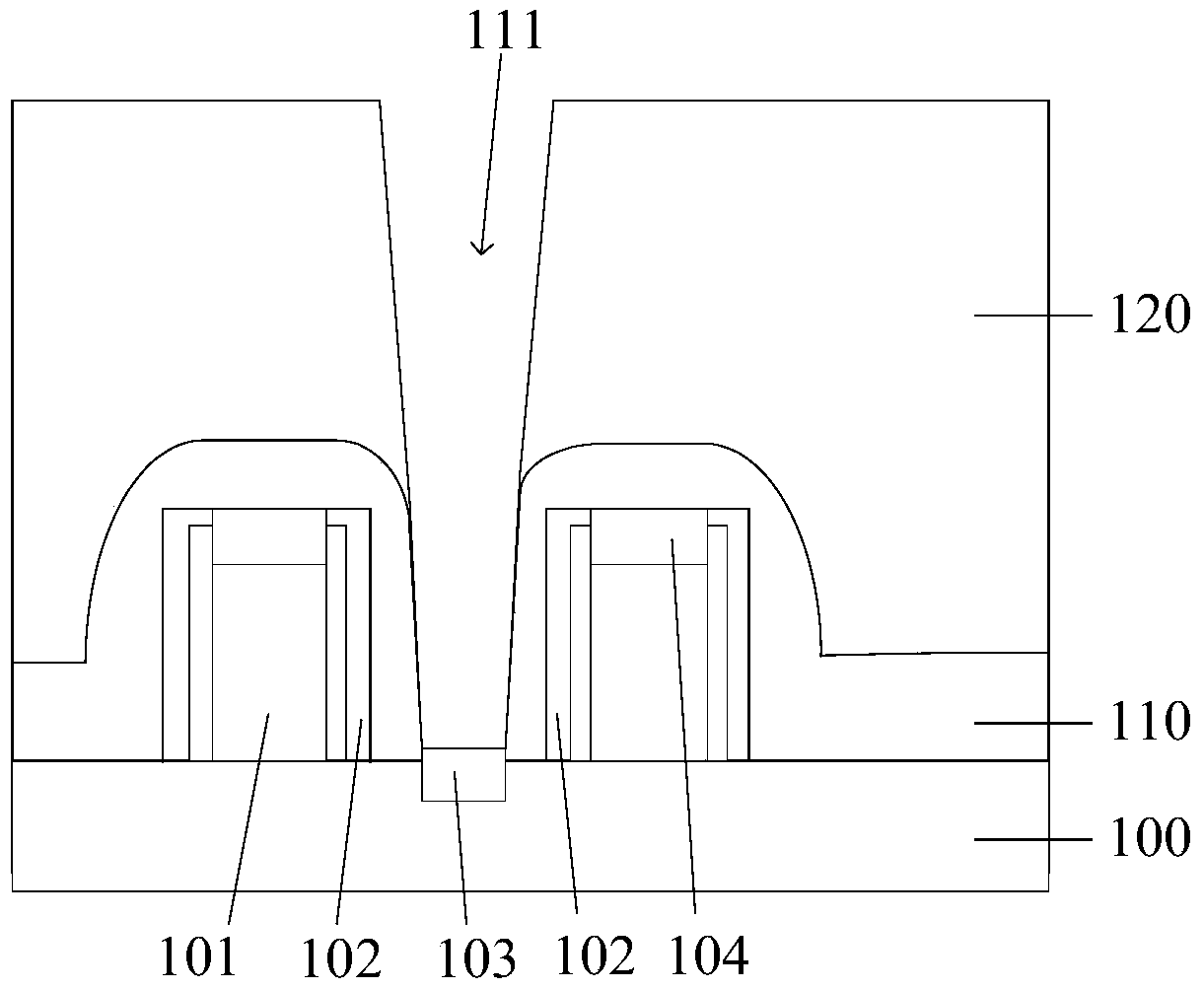

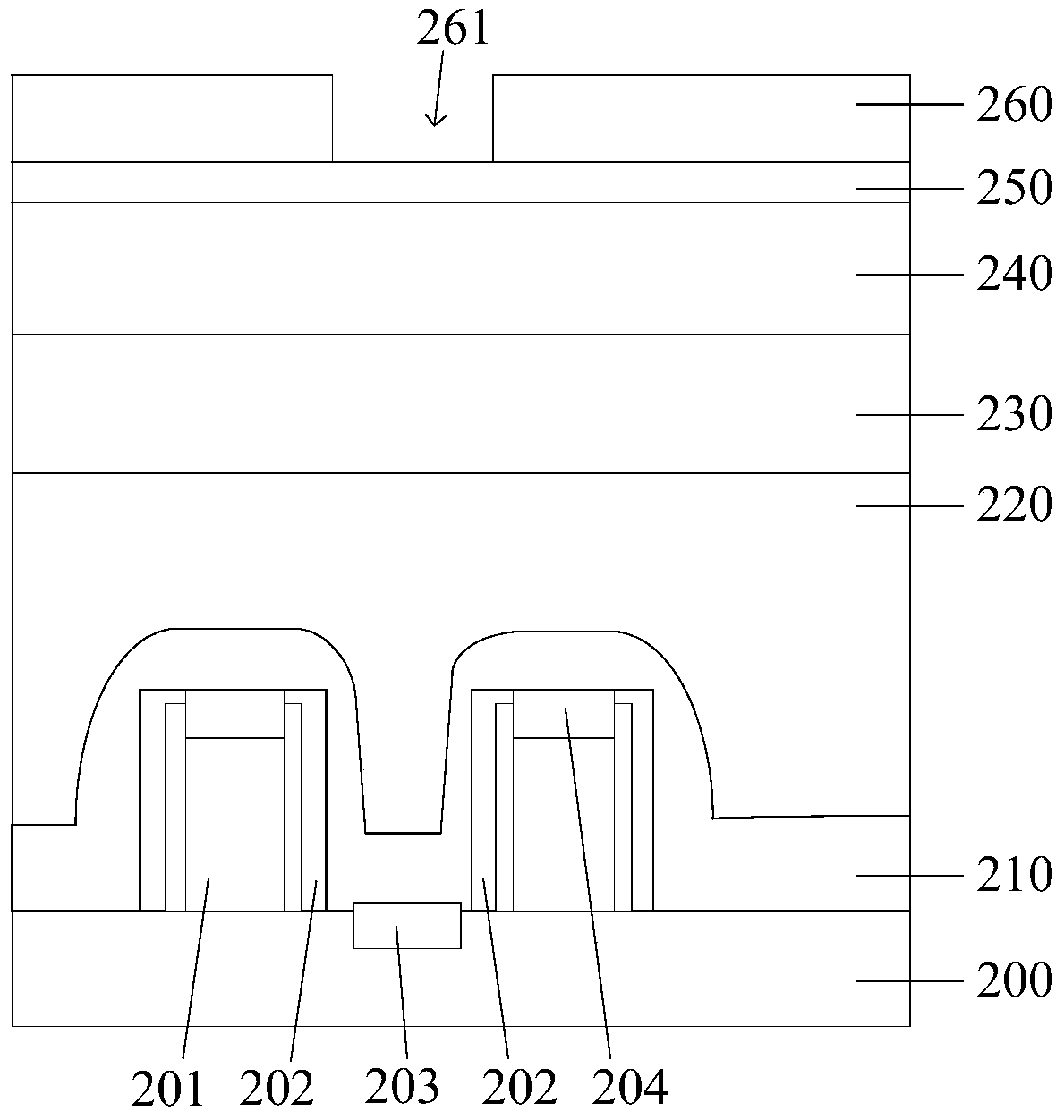

Formation method of contact plug

ActiveCN105097650AEasy to fillReduce the difficulty of formationSemiconductor/solid-state device manufacturingConductive materialsDielectric layer

A formation method of a contact plug comprises the steps of providing a substrate; forming an interlayer dielectric layer on the substrate; forming a high K dielectric layer on the interlayer dielectric layer; etching the high K dielectric layer and the interlayer dielectric layer orderly until the substrate is exposed to form a contact hole; continuously etching the high K dielectric layer along the contact hole until the diameter of the contact hole located at the high K dielectric layer is increased; adopting a conductive material to fill the contact hole. The formation method of the contact plug enables the formation difficulty of the contact plug to be reduced and also the quality of the formed contact plug to be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

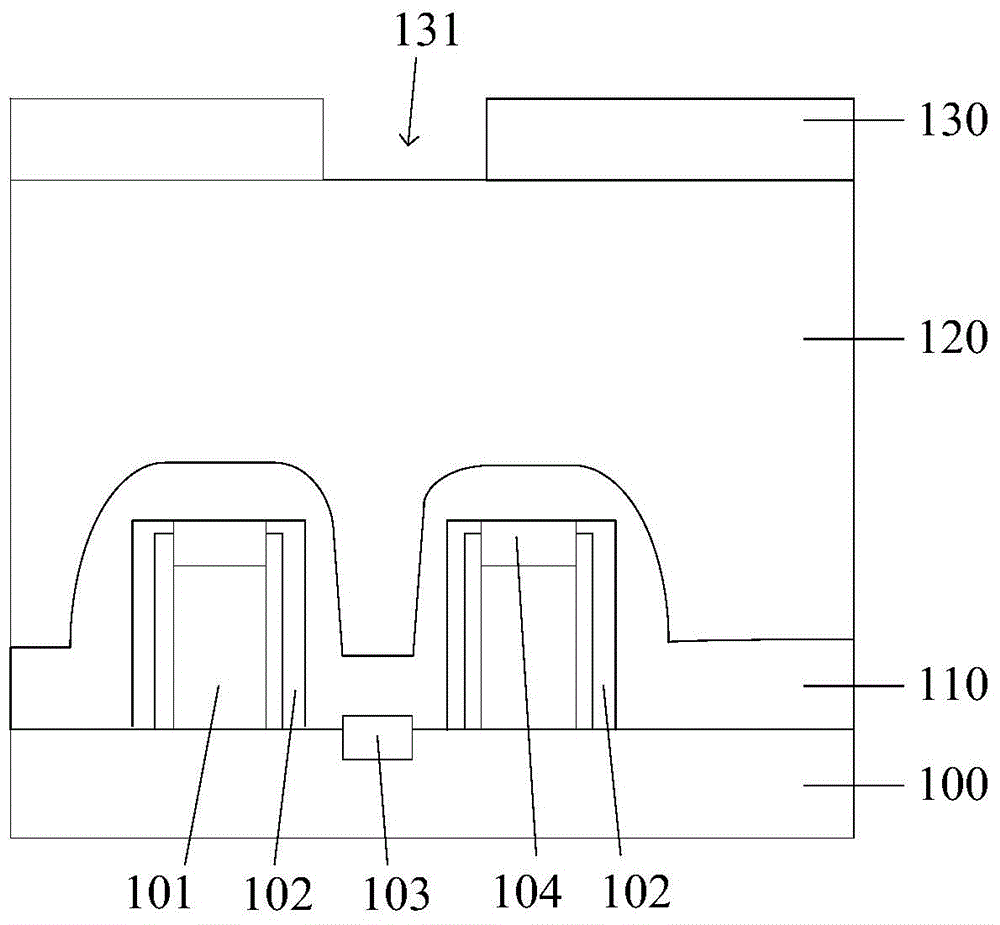

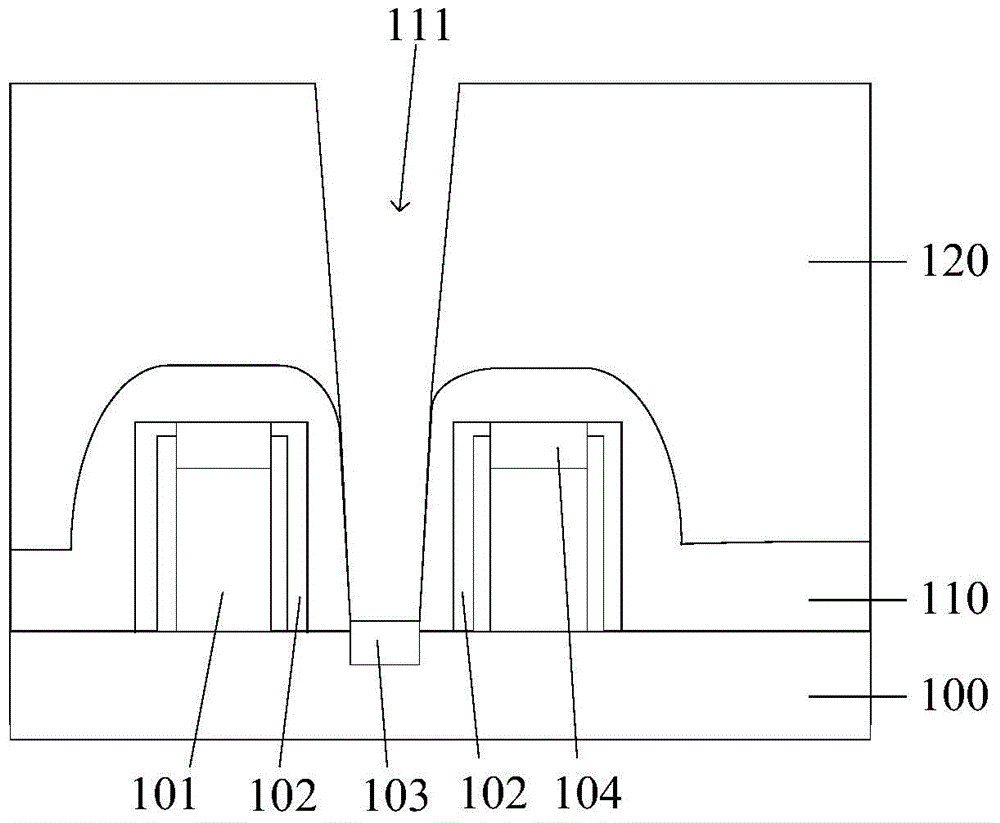

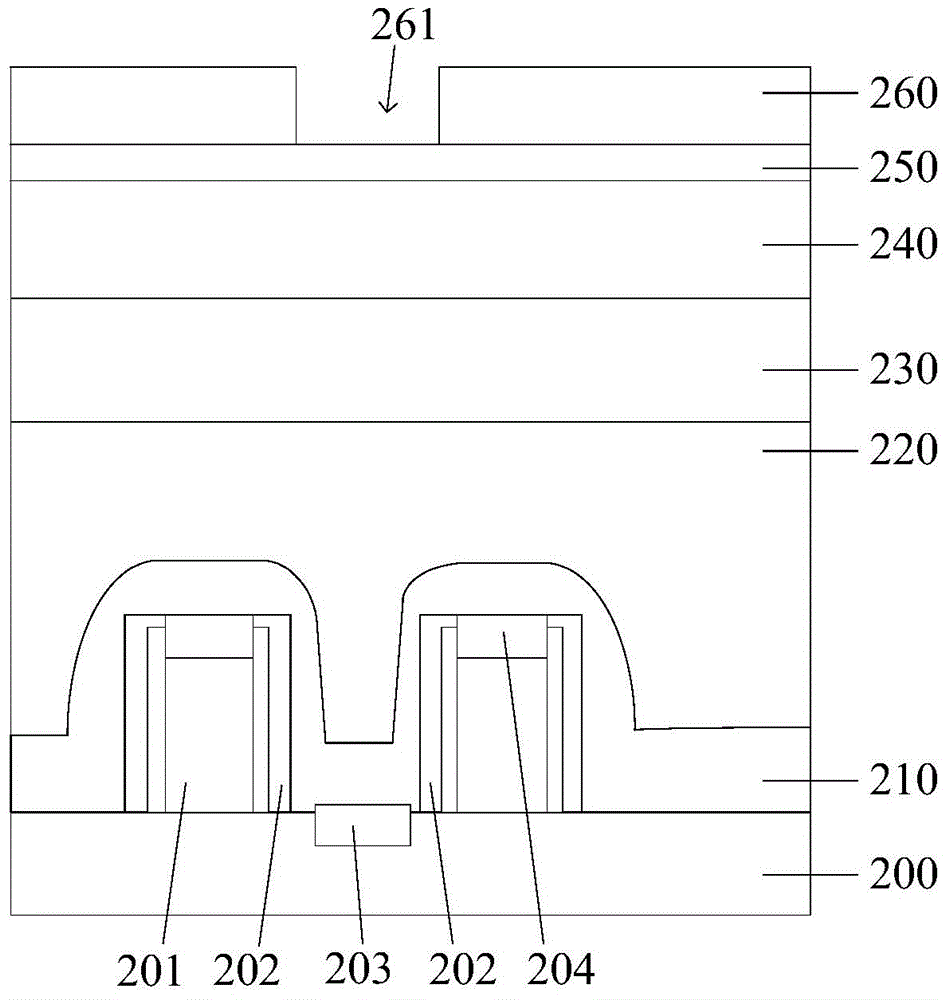

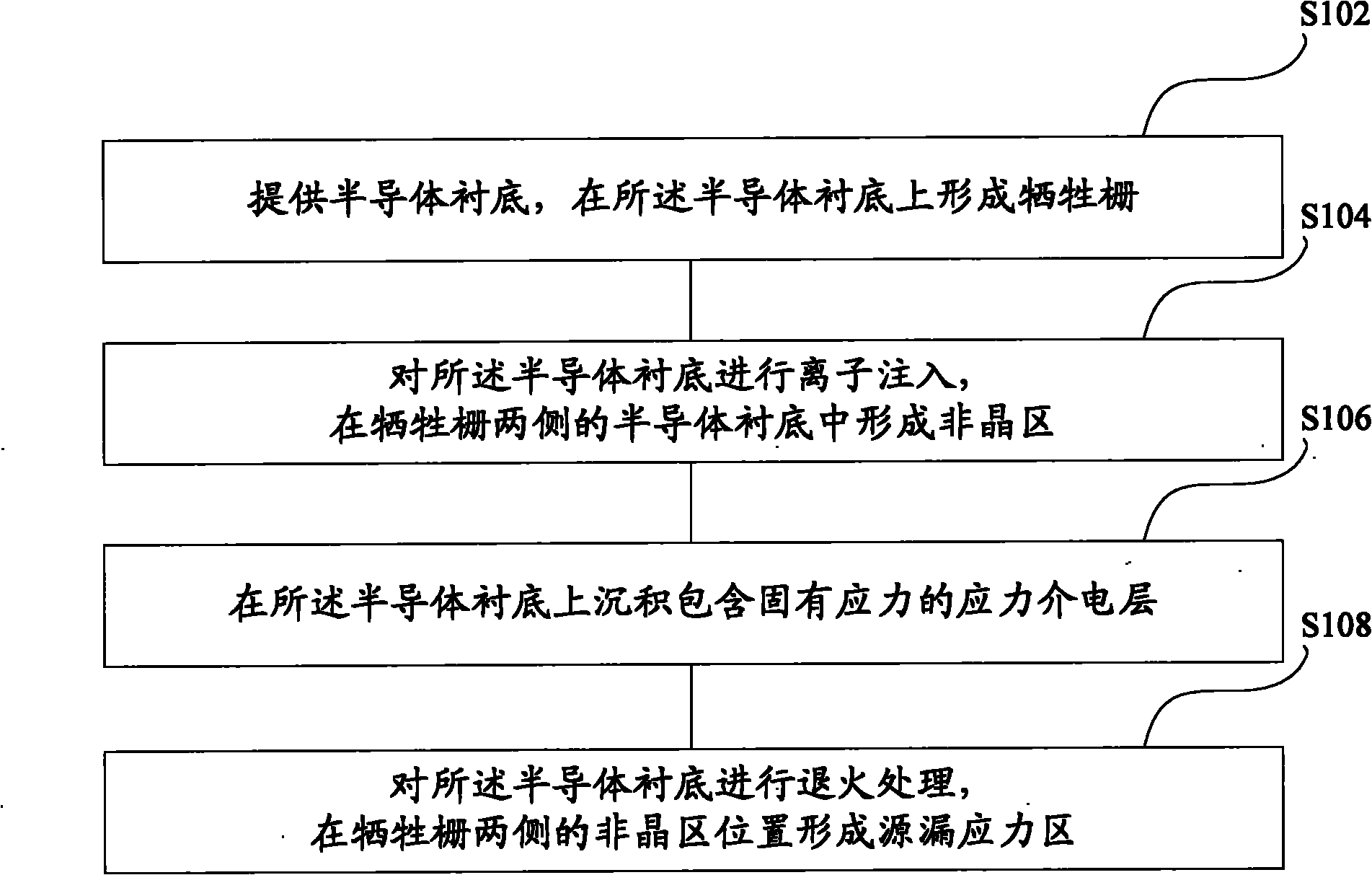

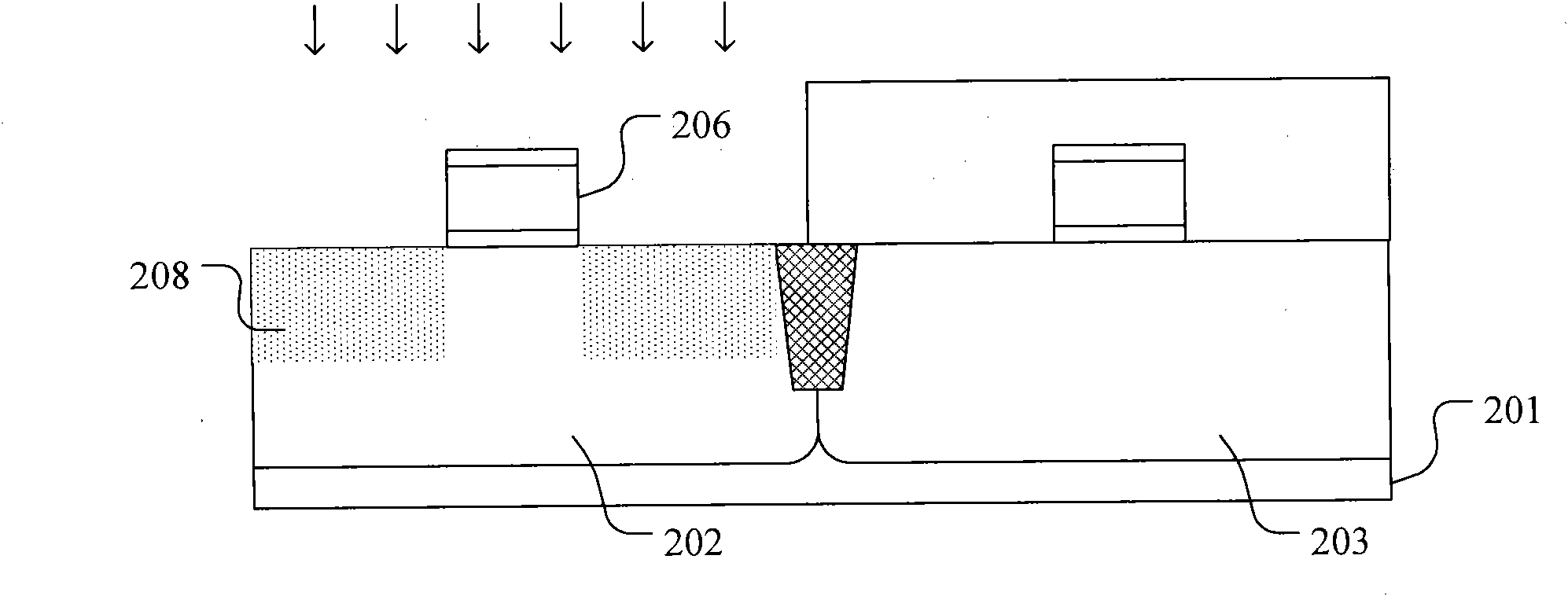

Forming method of metal-oxide semiconductor (MOS) transistor source drain stress area and manufacturing method of MOS transistor

InactiveCN102376575AReduce the difficulty of formationImprove mobilitySemiconductor/solid-state device manufacturingCharge carrier mobilityEngineering

The invention relates to a forming method of a metal-oxide semiconductor (MOS) transistor source drain stress area, which comprises the steps that: a semi-conductor substrate is provided, and a sacrifice grid is formed on the semi-conductor substrate; ions are implanted into the semi-conductor substrate, and an amorphous area is formed in the semi-conductor substrate on both sides of the sacrifice grid; a dielectric layer which contains inherent stress is formed on the semi-conductor substrate; the semi-conductor substrate is annealed; and a source drain stress area is formed in the amorphous area on both sides of the sacrifice grid. The forming method of the MOS transistor source drain stress area reduces the difficulty in filling a stress film above a source drain is reduced and greatly improves the stress conversion proportion to a channel by directly forming the dielectric layer which contains the inherent stress on the source drain area on both sides of a grid to introduce stress. Simultaneously, the semi-conductor substrate which is pre-amorphousized in the source drain area transfers the stress into the source drain area, so that the stress of an original etched dielectric layer and a channel area after a side wall is formed is still maintained, and the stress changes improve the carrier mobility.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

A kind of positive lead paste for lead-acid storage battery and preparation method thereof

The invention discloses positive lead plaster for a lead-acid storage battery and a preparation method of the positive lead plaster. The positive lead plaster is characterized by consisting of the following raw materials by weight percent: 7 to 10 percent of 1.4g / ml dilute sulfuric acid, 8 to 12 percent of deionized water, 5 to 20 percent of red lead, 0.1 to 0.4 percent of colloid graphite, 0.1 to 0.3 percent of stannous sulfate, 0.1 to 0.3 percent of anhydrous sodium sulfate, 0.2 to 0.5 percent of 4BS, 0.1 to 0.3 percent of diantimony trioxide, 0.05 to 0.2 percent of polyester short fibers, and the balance being lead powder. After the lead plaster which is prepared by utilizing the formula and the preparation method is prepared into the storage battery, the storage battery has the characteristics of high primary capacity, long service life, good low-temperature performance and good charging capacity.

Owner:江苏海宝电池科技有限公司

Small-pore-diameter narrow-distribution polytetrafluoroethylene microporous membrane and preparation method thereof

InactiveCN109224885AWell packagedImprove wettabilitySemi-permeable membranesPore diameterSurface-active agents

The invention discloses a preparation method of a small-pore-diameter narrow-distribution polytetrafluoroethylene microporous membrane. By mixing of dispersible polytetrafluoroethylene resin, solventoil and a surface active agent and adopting the processes of ageing, blank manufacture, pushing and squeezing, calendaring, oil removal, longitudinal pulling treatment, horizontal pulling treatment, sintering and sizing and the like, the polytetrafluoroethylene microporous membrane with the pore diameter being 10-50nm and the bubble-point pore diameter being less than 80nm is manufactured; the surface active agent is added into a formula, and by the action of the surface active agent, the wettability of the solvent oil is obviously improved, and the wrapping degree of the solvent oil to the polytetrafluoroethylene resin is obviously improved, so that the formation degree of micropores in the drawing and expanding processes is greatly reduced; under the action of same shearing force, the formed micropores are more and smaller, so that the microporous membrane with small pore diameter and narrow distribution is obtained; the preparation method is easy in industrial production, can utilize the existing manure equipment only in need of proper process adjustment, and has strong practicability and wide applicability.

Owner:华设设计集团环境科技有限公司

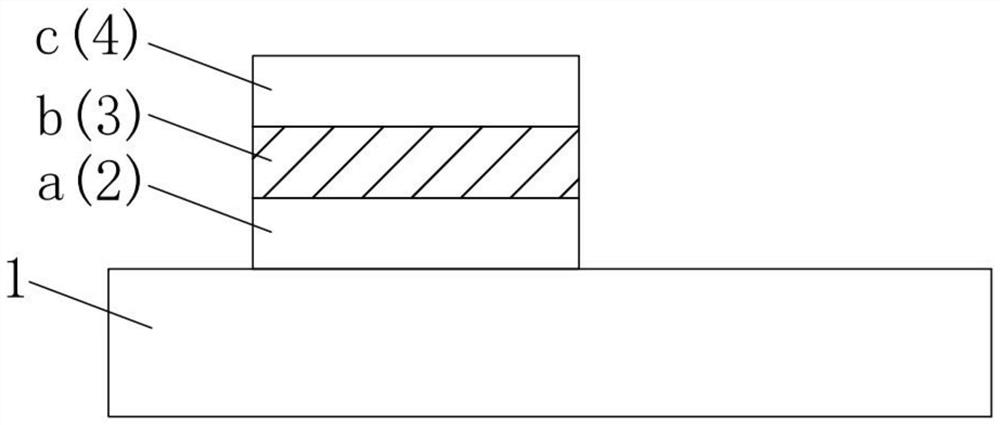

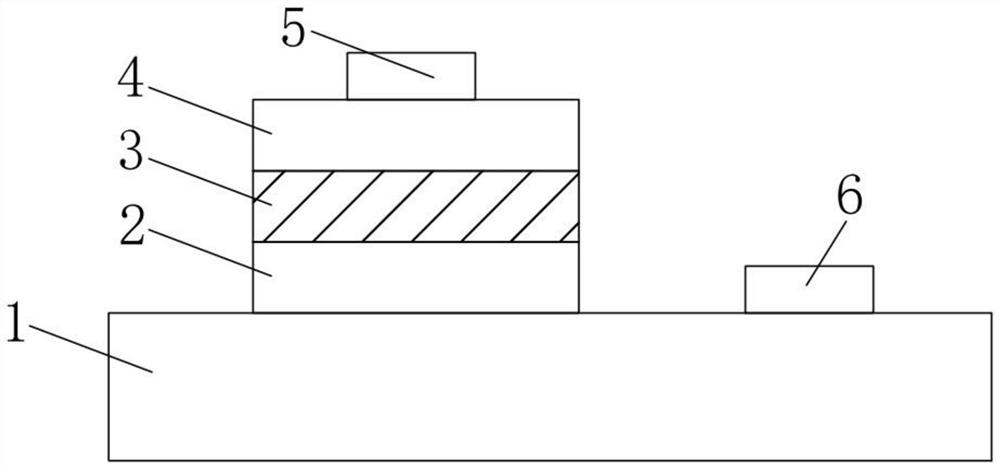

GaN-based HEMT low-temperature gold-free ohmic contact electrode and preparation method thereof

PendingCN112670336AEnhanced ohmic contactMitigate Electronic LeakageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEtching

The invention discloses a GaN-based HEMT low-temperature gold-free ohmic contact electrode. The GaN-based HEMT low-temperature gold-free ohmic contact electrode comprises a GaN-based HEMT epitaxial layer, wherein a GaN channel layer is arranged in the GaN-based HEMT epitaxial layer. The electrode comprises a first metal layer Ti, a second metal layer Al and a third metal layer TiW which are sequentially arranged on the upper surface of the GaN-based HEMT epitaxial layer from bottom to top, or a first metal layer Ti, a second metal layer Al, a third metal layer Ti and a fourth metal layer TiW which are sequentially arranged from bottom to top. The invention also correspondingly discloses a preparation method of the electrode. According to the invention, the annealing temperature of GaN-based HEMT ohmic contact is effectively reduced, 2DEG leakage caused by overall etching of an AlGaN barrier layer and current reduction during ohmic contact forming are improved, ohmic contact forming difficulty is reduced, and the appearance and edge of an ohmic contact surface after low-temperature alloy annealing are smoother. Meanwhile, the manufacturing cost of a GaN-based HEMT device can be reduced.

Owner:ZHONGSHAN INST OF MODERN IND TECH SOUTH CHINA UNIV OF TECH +1

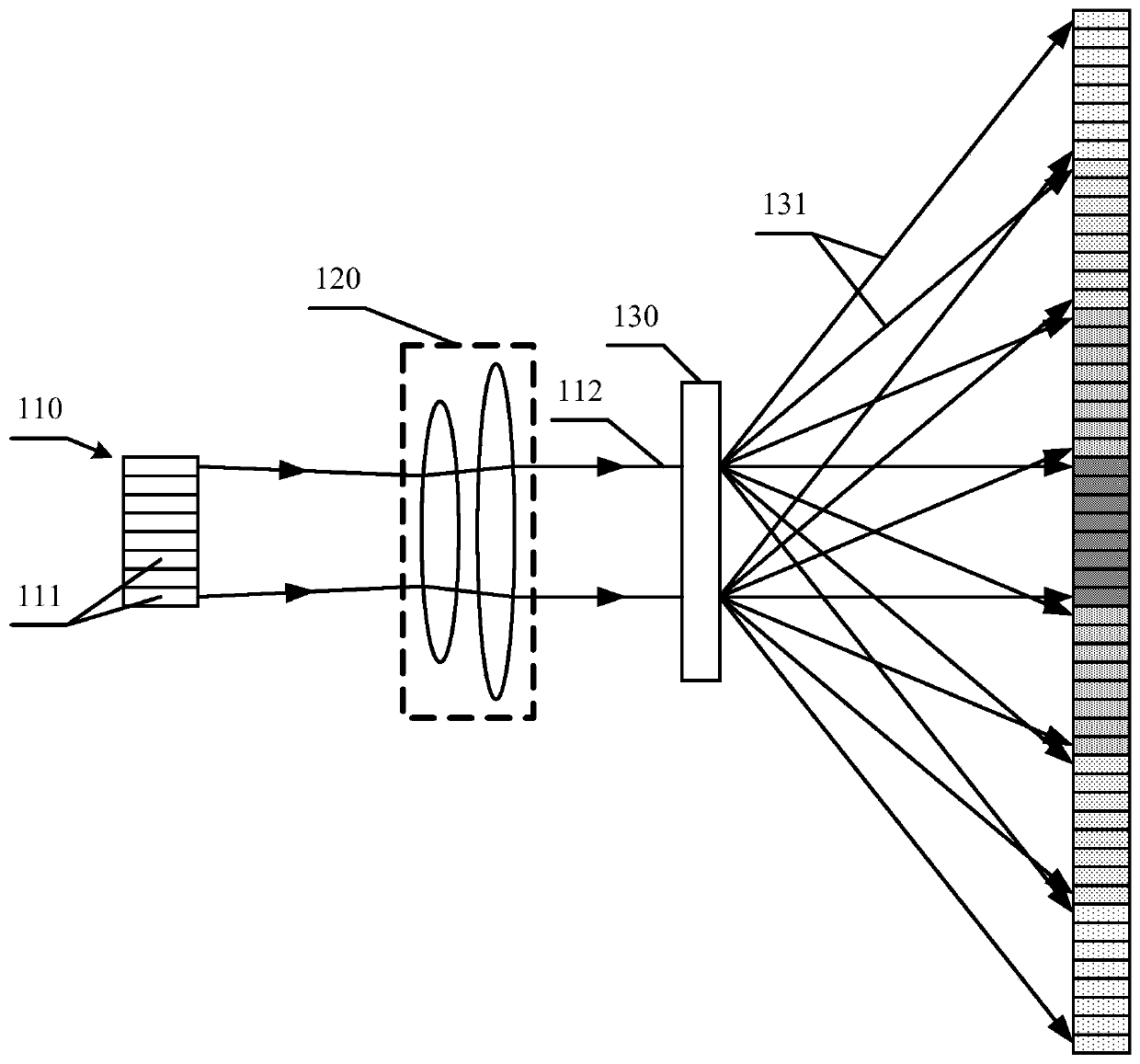

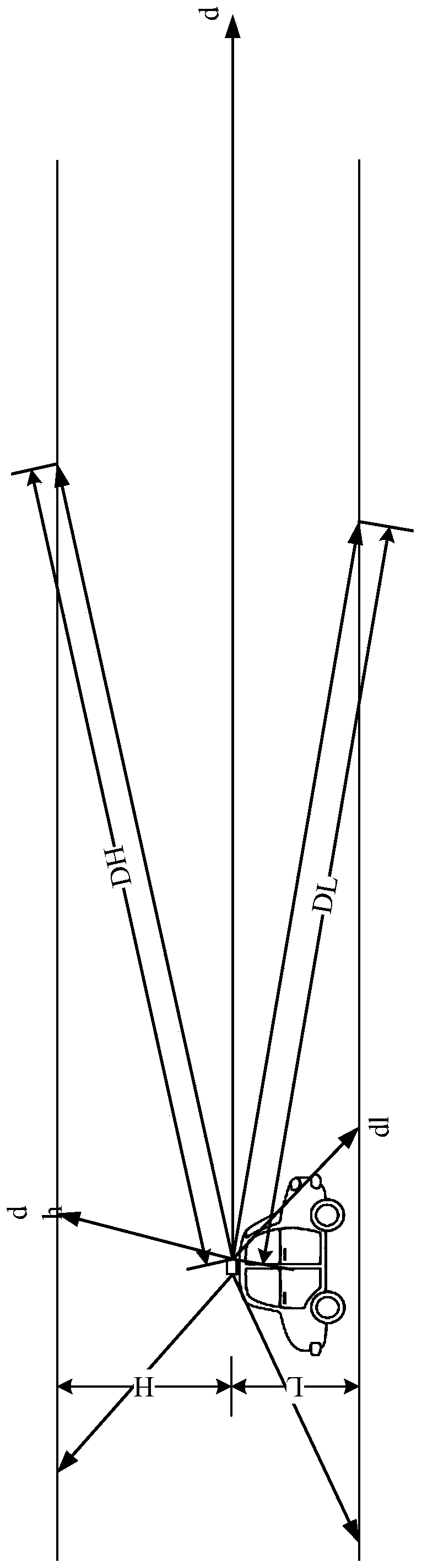

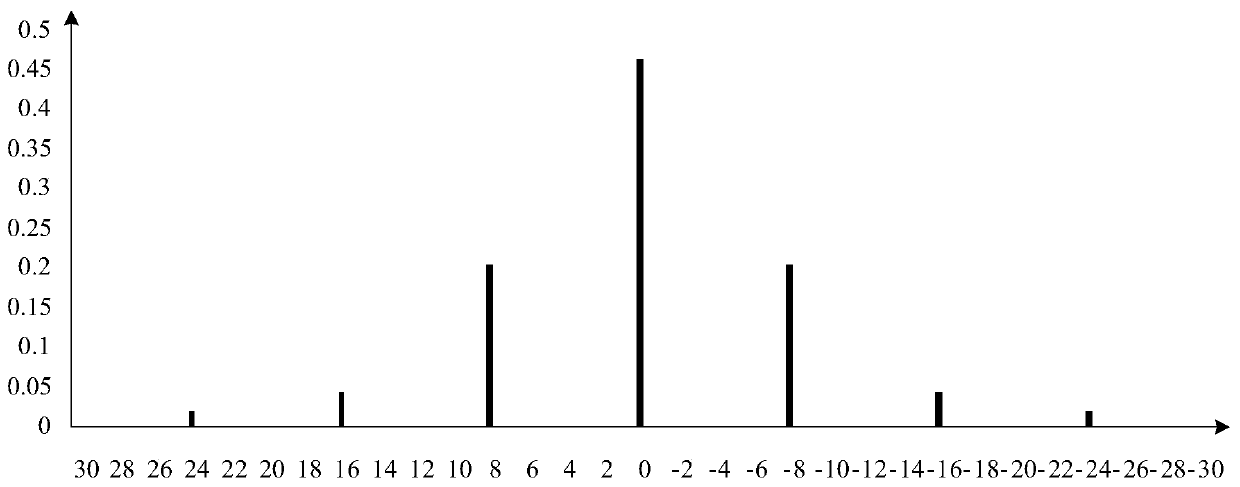

Laser radar transmitting system, design method thereof, and laser radar

InactiveCN109917352AReduce in quantityEffective control of transmit powerElectromagnetic wave reradiationBeam splittingRadar

A laser radar transmitting system, a design method thereof, and a laser radar are provided. The laser radar transmitting system comprises a light source including at least one laser for transmitting first detection light beams; a transmitting optical component used for collimating the first detection light beams into parallel light; a diffractive optical element that splits each collimated first detection light beam into N second detection light beams in the vertical field-of-view direction of the laser radar, wherein the beam splitting ratio among the respective diffraction angles of the diffractive optical element is set as the ratio of the respective predetermined detection distances in the vertical field-of-view direction corresponding to the respective diffraction angles. The technical solution of the invention can not only effectively reduce the number of lasers in the laser radar, but also can take account of both the detection distance and the energy consumption control.

Owner:HESAI TECH CO LTD

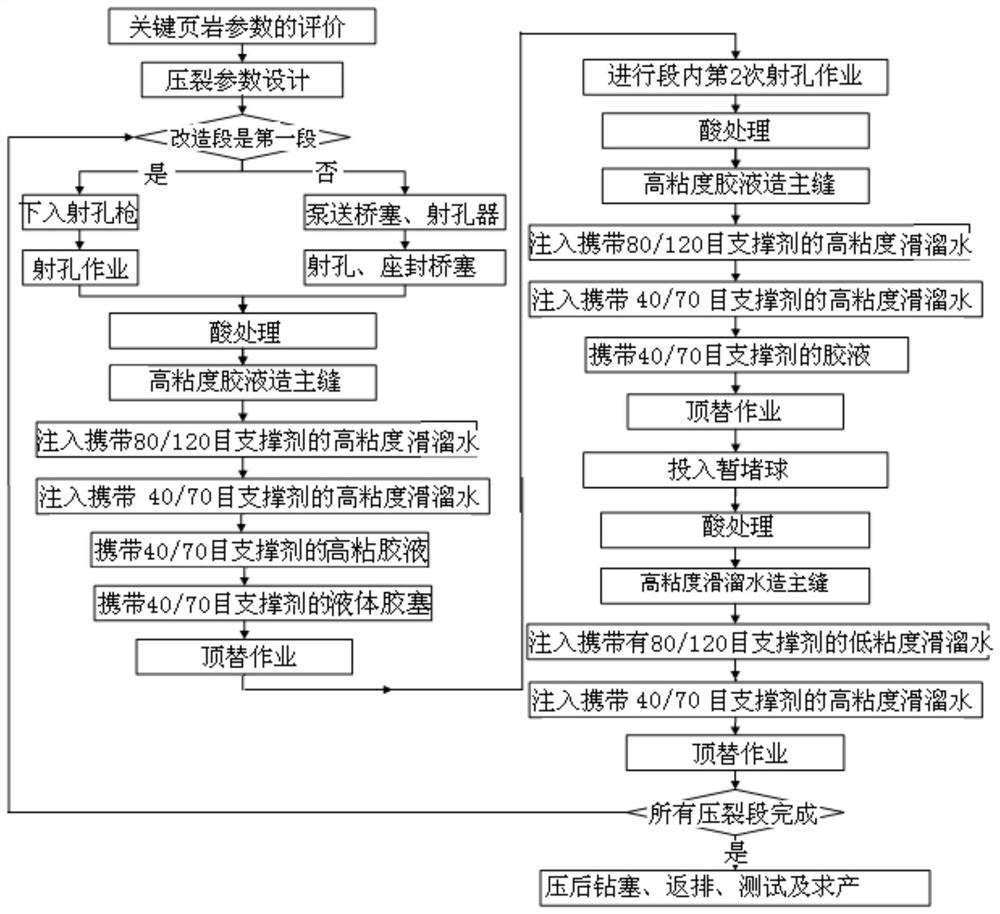

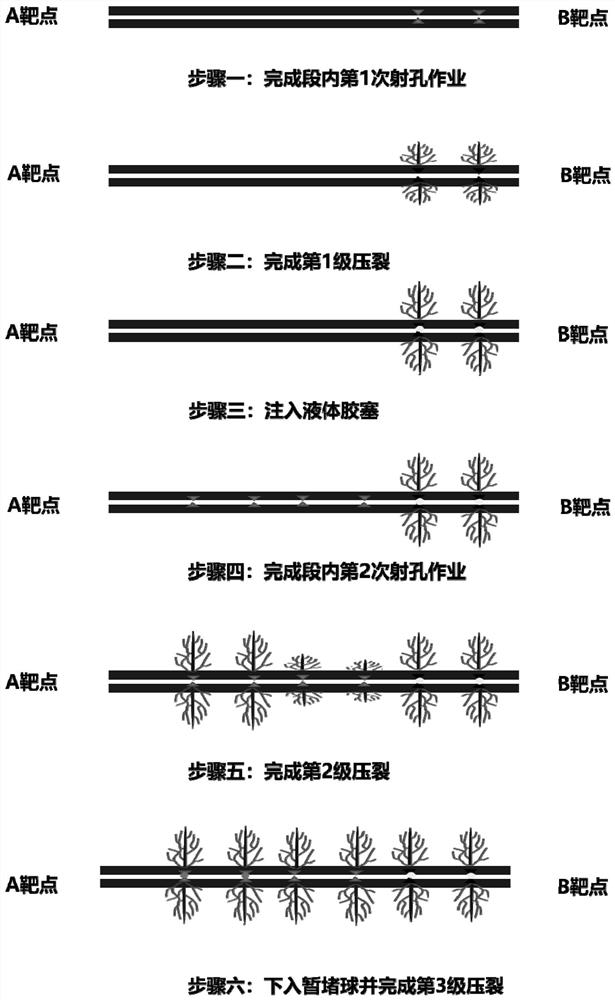

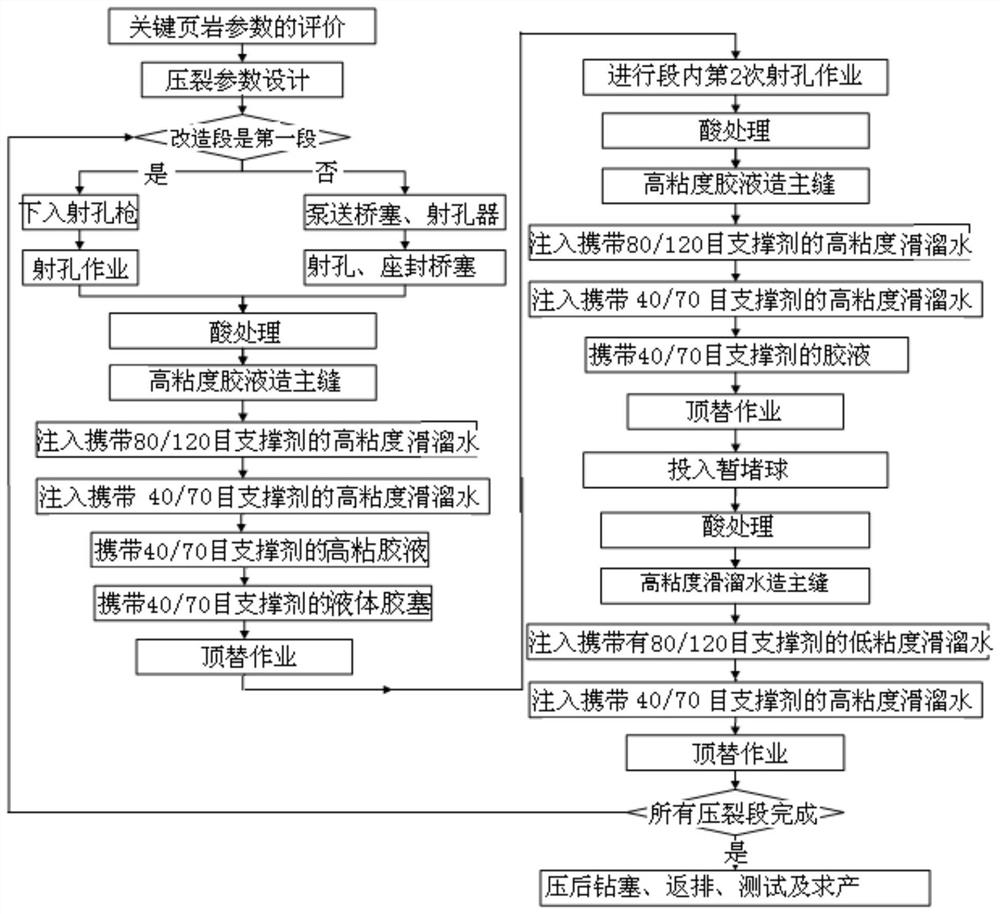

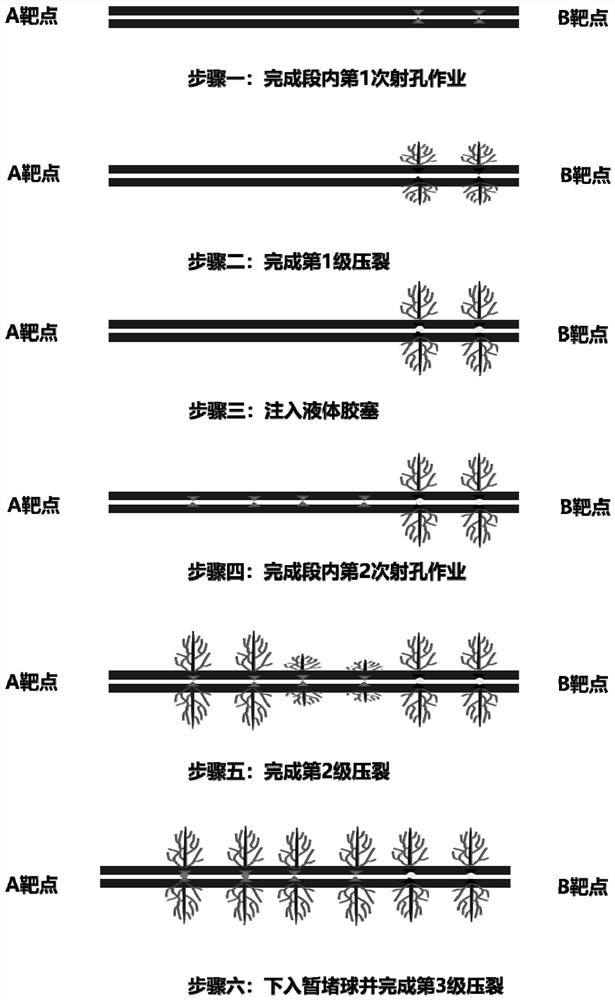

Close cutting fracturing method

ActiveCN112177583AIncrease the amount of liquidRealize centralized liquid intakeFluid removalThermodynamicsSingle stage

The invention relates to a close cutting fracturing method. The method comprises the steps that shale parameters are evaluated, and fracture parameters and fracturing construction parameters are optimized; perforation operation of the first time is carried out; fracturing treatment is carried out, and a liquid rubber plug carrying a propping agent is injected after fracturing treatment is finished; displacement operation is carried out; perforation operation of the second time is carried out; fracturing treatment and displacement operation are carried out; ball throwing temporary plugging is carried out on transformed perforation clusters; fracturing treatment is carried out on perforation clusters which are not transformed; displacement operation is carried out; a bridge plug is tripped in, and the above steps are repeated until construction of all sections is completed; and plug drilling after pressing, flowback, testing and production are carried out. 5-8 clusters of high-difficultyoperation are converted into 3-stage fracturing operation through two times of perforation operation and ball throwing temporary plugging in a single section, and therefore conventional 3-6 clustersof the single section are reduced into 1-2 clusters of the single stage fracturing operation, the liquid inlet amount of a single cluster is increased, the requirement of fracturing construction for displacement is reduced, and a construction pressure window is enlarged; and meanwhile, the horizontal principal stress difference is reduced through the stress shadow effect, the fracture complexity is improved, and the transformation size of a deep shale gas well is increased.

Owner:CHINA PETROLEUM & CHEM CORP +1

Infrared detector and manufacturing method thereof

ActiveCN111106203AImprove quantum efficiencyIncrease flexibilityFinal product manufactureVacuum evaporation coatingHeterojunctionEngineering

The invention discloses a manufacturing method of an infrared detector. The manufacturing method comprises the following steps: forming a detector mesa on an N-type substrate, wherein the detector mesa comprises an N-type InAsP / InAsSb superlattice absorption layer, an InPSb barrier layer and an N-type InAsP / InAsSb superlattice contact layer, which are sequentially formed on the N-type substrate ina stacked manner; and forming a first electrode on the N-type InAsP / InAsSb superlattice contact layer of the detector mesa, and forming a second electrode corresponding to the detector mesa on the N-type substrate. The invention also discloses the infrared detector manufactured by the manufacturing method. According to the invention, the problem that a heterojunction structure is difficult to form in the manufacturing process of the infrared detector is solved.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

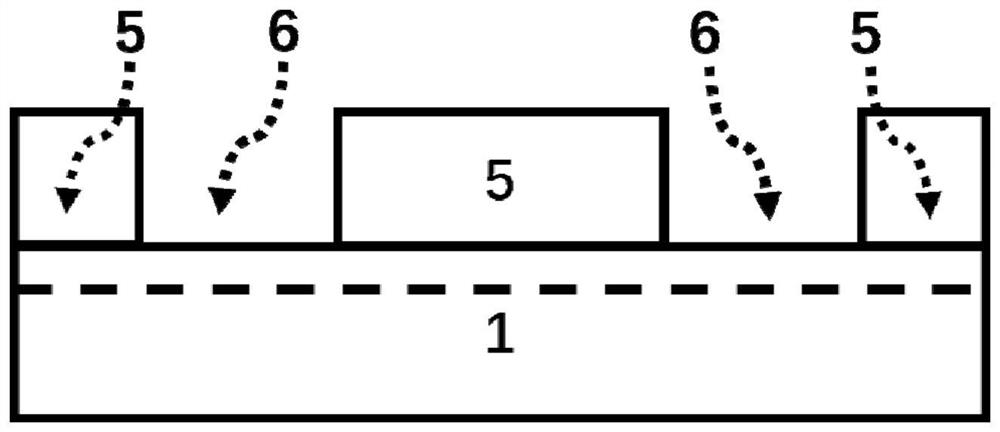

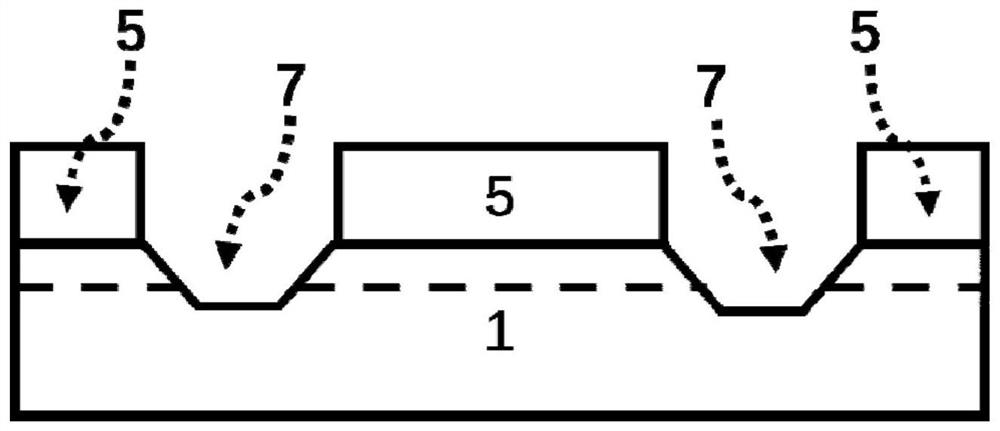

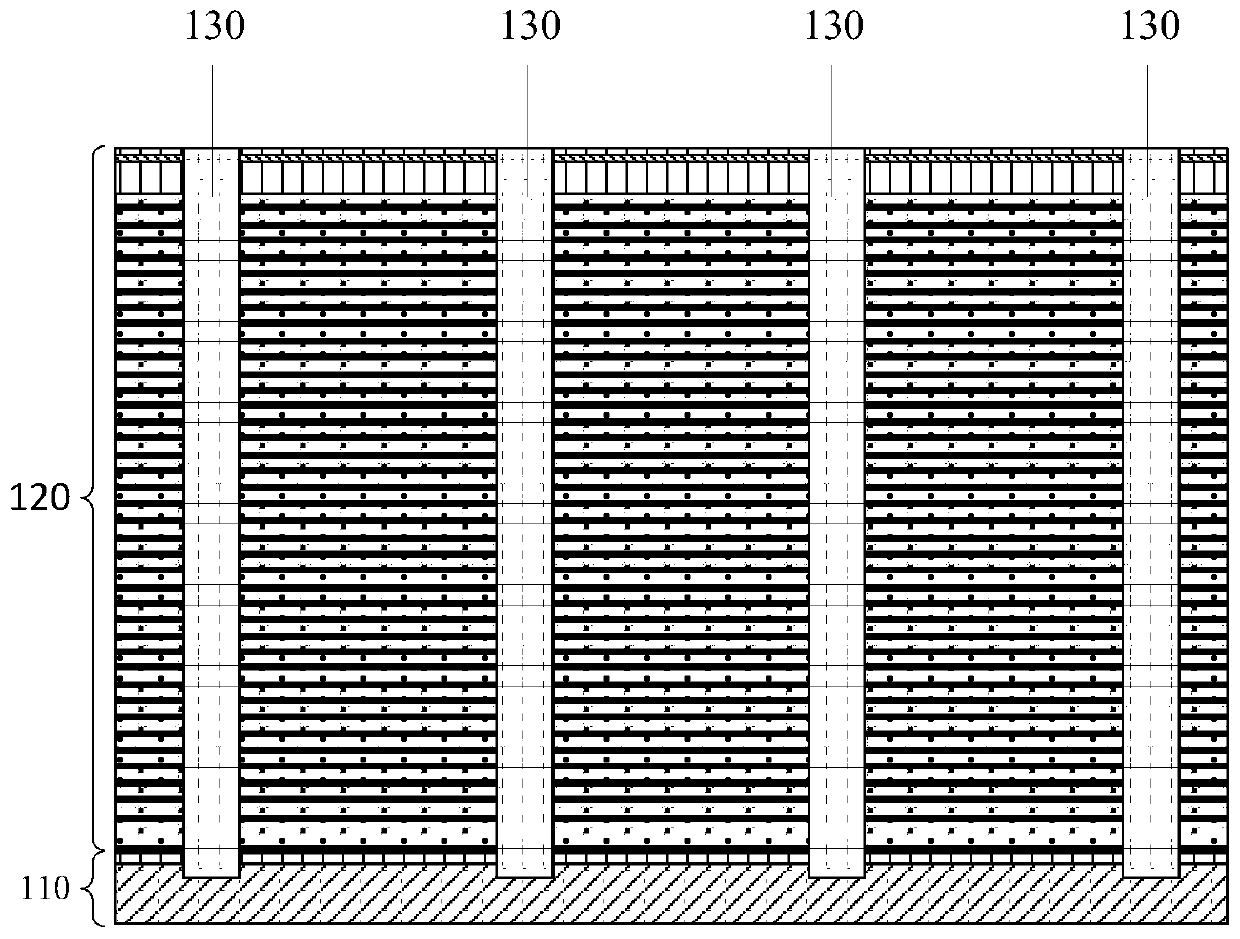

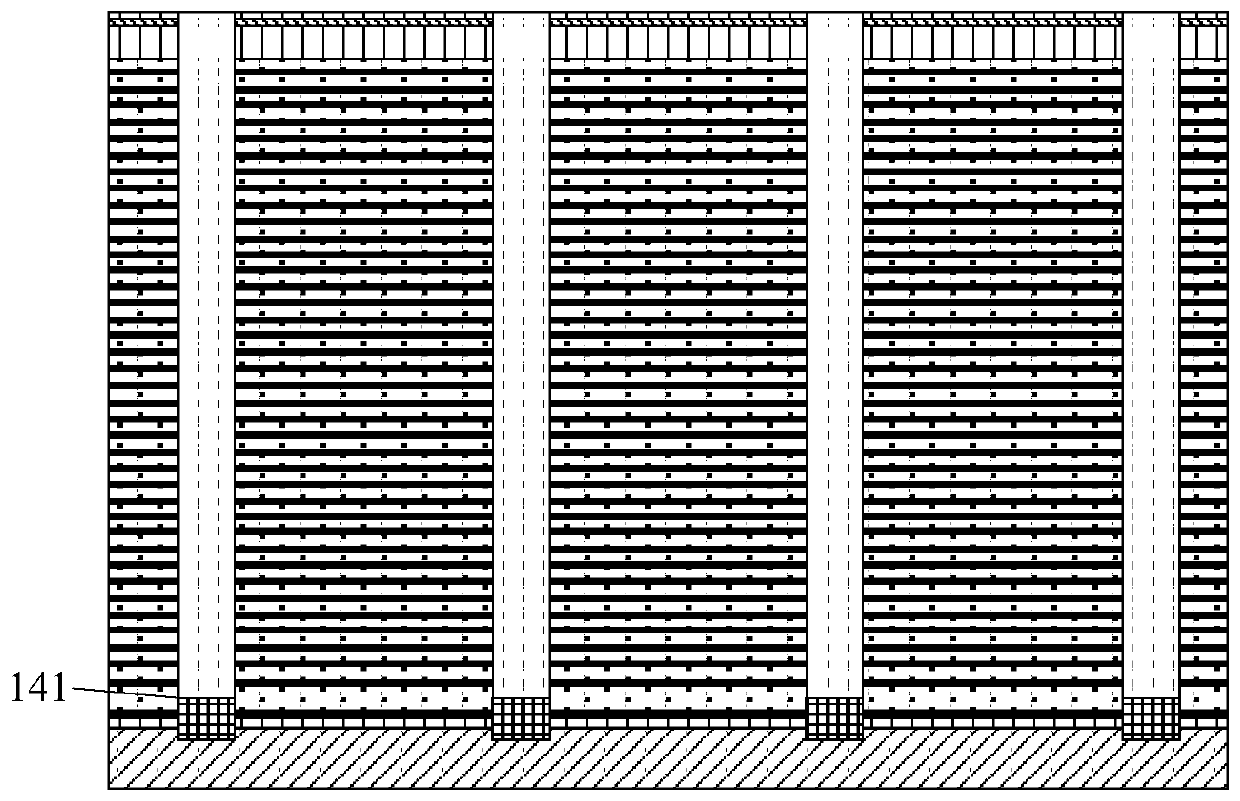

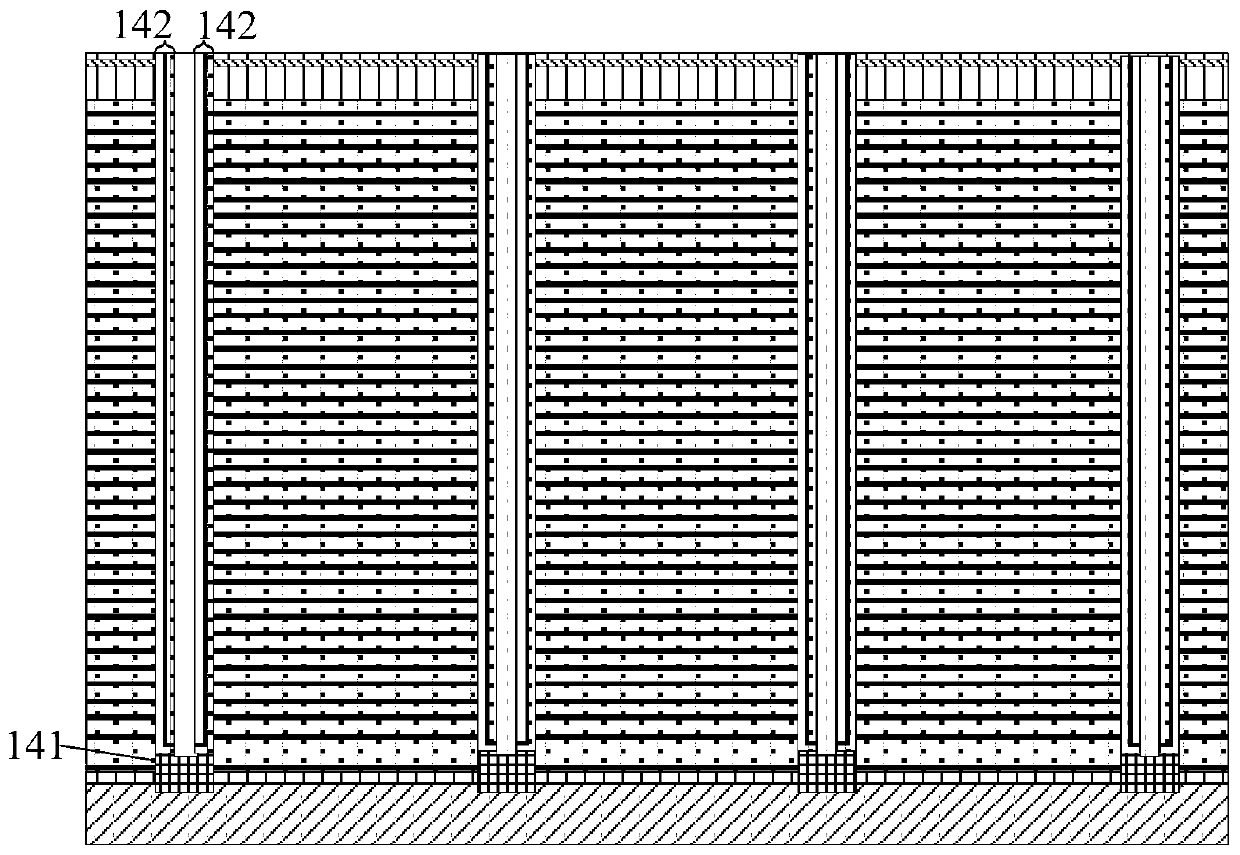

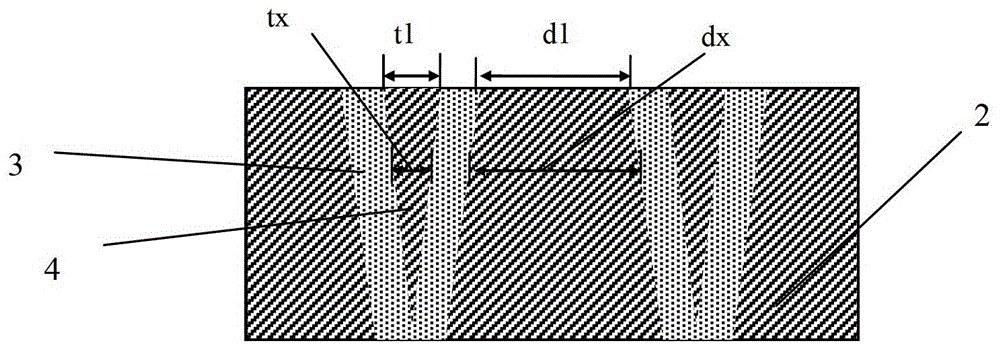

Memory and forming method thereof

ActiveCN109817573AIncrease spacingReduce the difficulty of formationSemiconductor/solid-state device detailsSolid-state devicesInterconnectionComputer science

The invention relates to a memory and a forming method thereof. The formation method of the memory comprises the following steps of: providing a storage substrate, wherein the storage substrate comprises a substrate and a device layer; the device layer is formed on the front surface of the substrate; a storage structure and an interconnection structure are formed in the device layer; the interconnection structure is electrically connected with the storage structure; an insulating layer is formed in the substrate; at least part of the interconnection structure is formed on the surface of the insulating layer; the top surface of the insulating layer is flush with the front surface of the substrate; and the bottom surface of the insulating layer is flush with the back surface of the substrate; forming a dielectric layer positioned on the back surface of the substrate and the bottom surface of the insulating layer; and forming a through contact part penetrating through the dielectric layerand the insulating layer, wherein the through contact part is electrically connected with at least part of the interconnection structure. The method can save the process steps and reduce the cost.

Owner:YANGTZE MEMORY TECH CO LTD

Durable lead-acid storage battery positive electrode lead paste and preparation method thereof

InactiveCN113540441AReduce the difficulty of formationImprove efficiencyLead-acid accumulator electrodesElectrical batteryLead sulfate

The invention discloses a durable lead-acid storage battery positive electrode lead paste, and belongs to the technical field of lead storage battery paste mixing processes. The durable lead-acid storage battery positive electrode lead paste comprises 100 parts of lead powder, 0.2 part of short fibers, 9 parts of red lead, 13-14 parts of pure water, 11 parts of sulfuric acid, 1 part of tetrabasic lead sulfate (4BS) and 1.5 parts of carbon black. Th concentration of the sulfuric acid is 50%. According to the invention, by adding the 4BS and the carbon black, on the basis of the same curing process, the content of 4BS in the lead-acid storage battery polar plate can be increased, the size of 4BS crystals can be improved, the battery formation difficulty can be reduced, and the battery performance and the production efficiency can be improved.

Owner:SHUANGDENG GRP

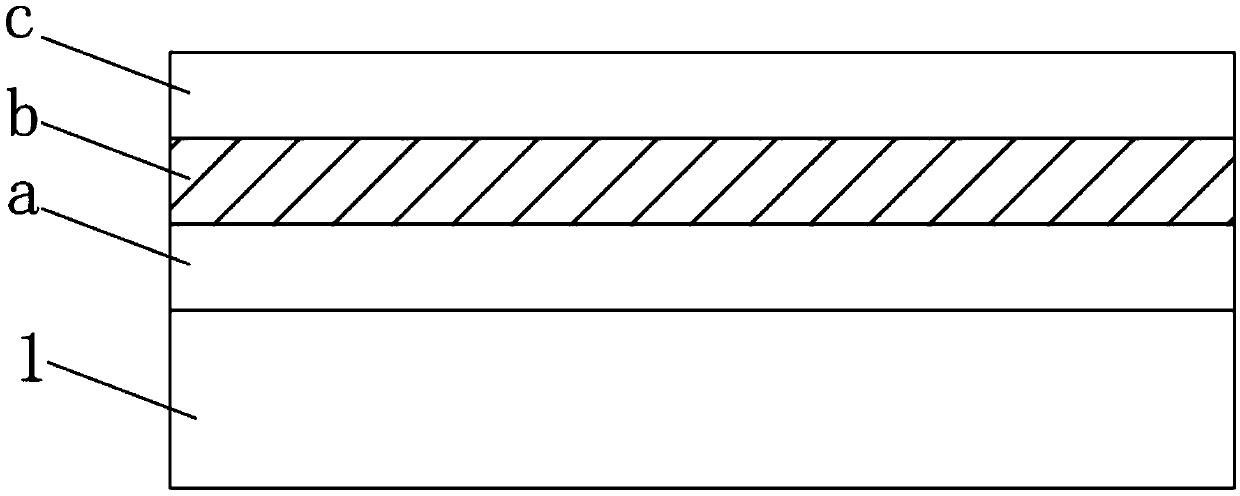

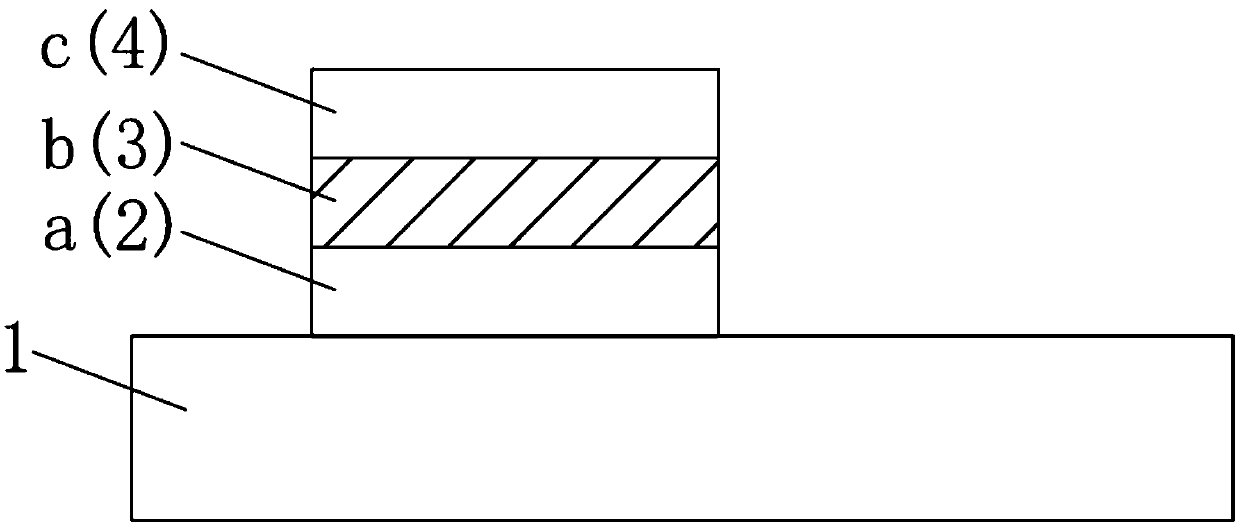

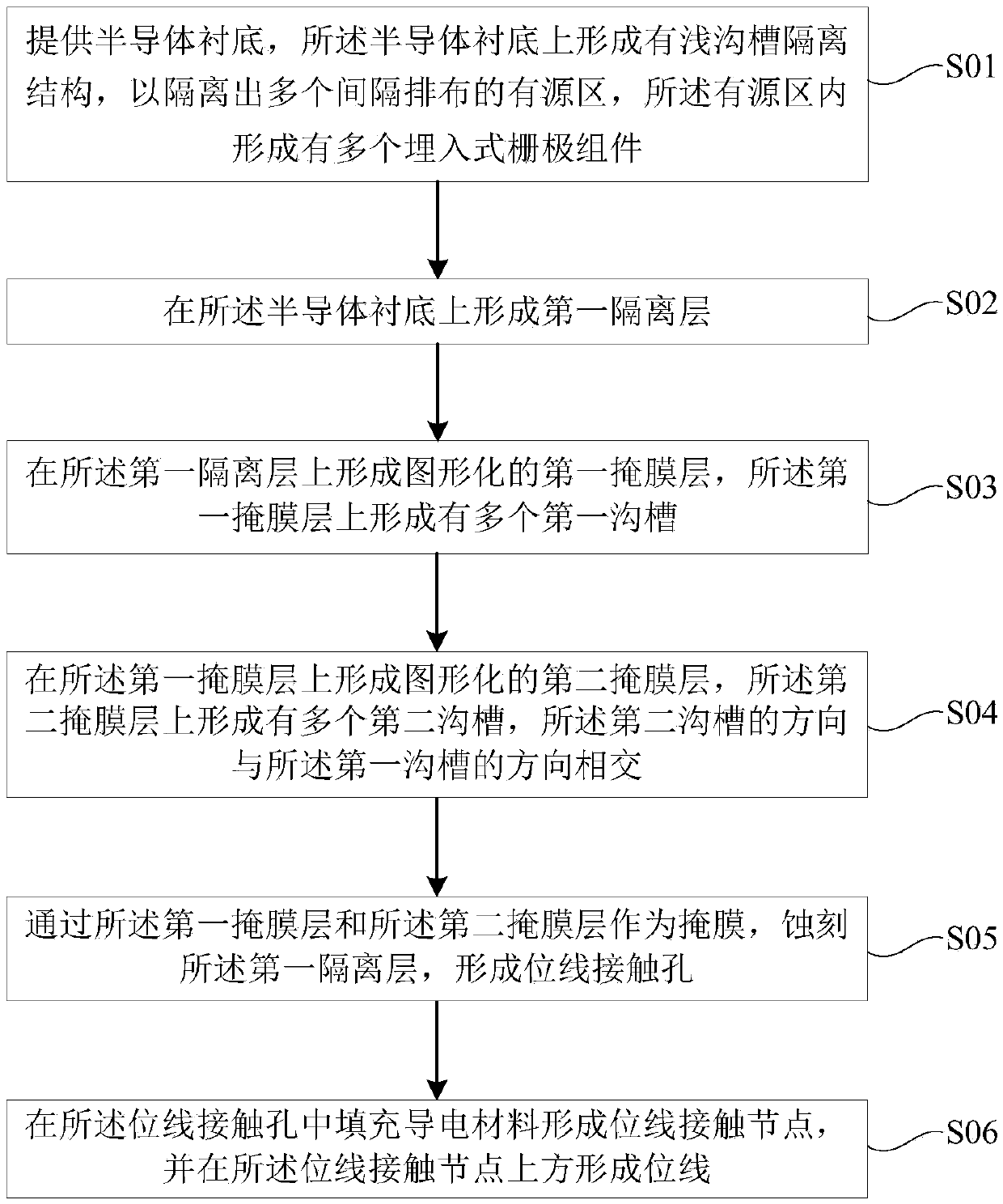

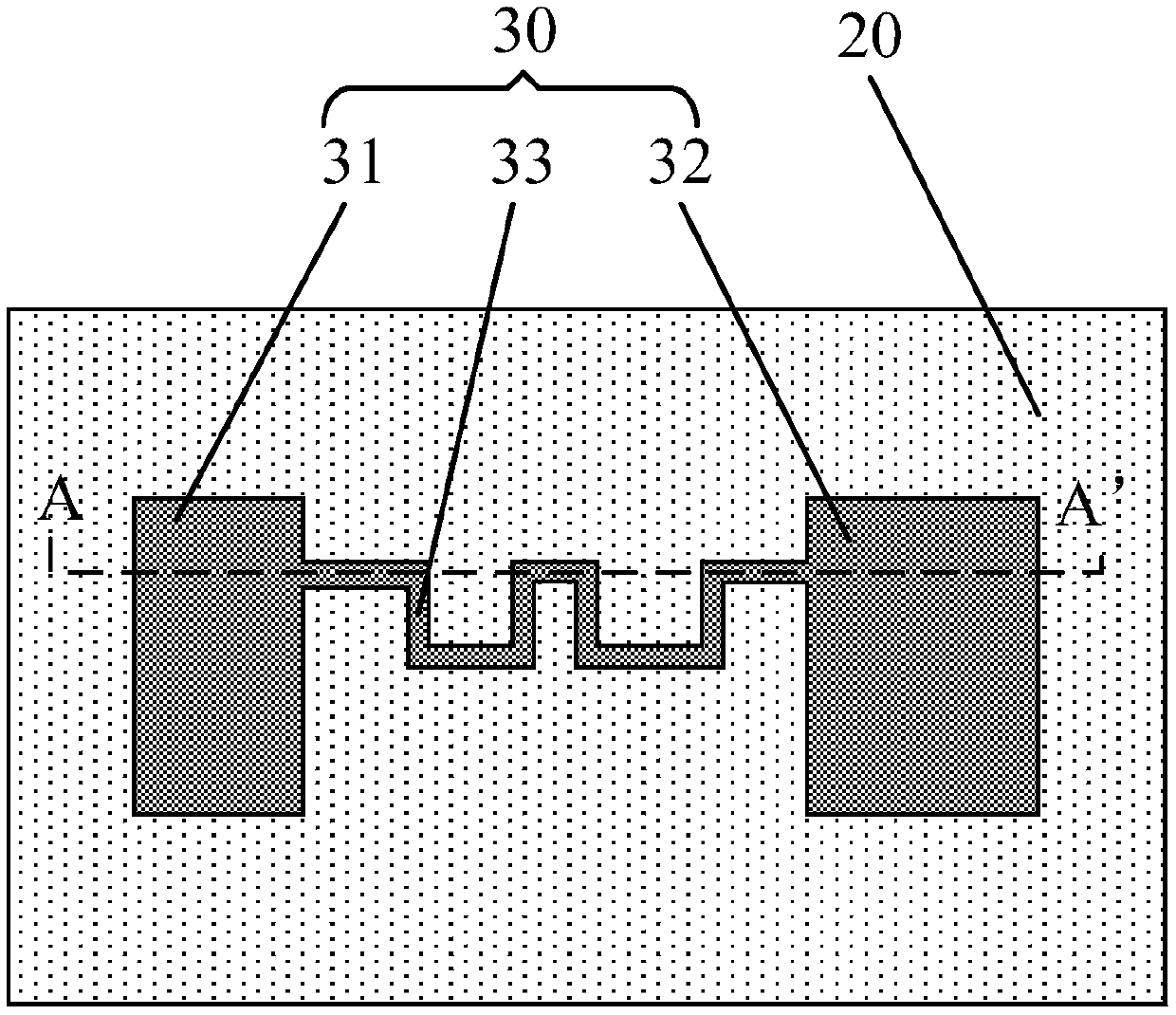

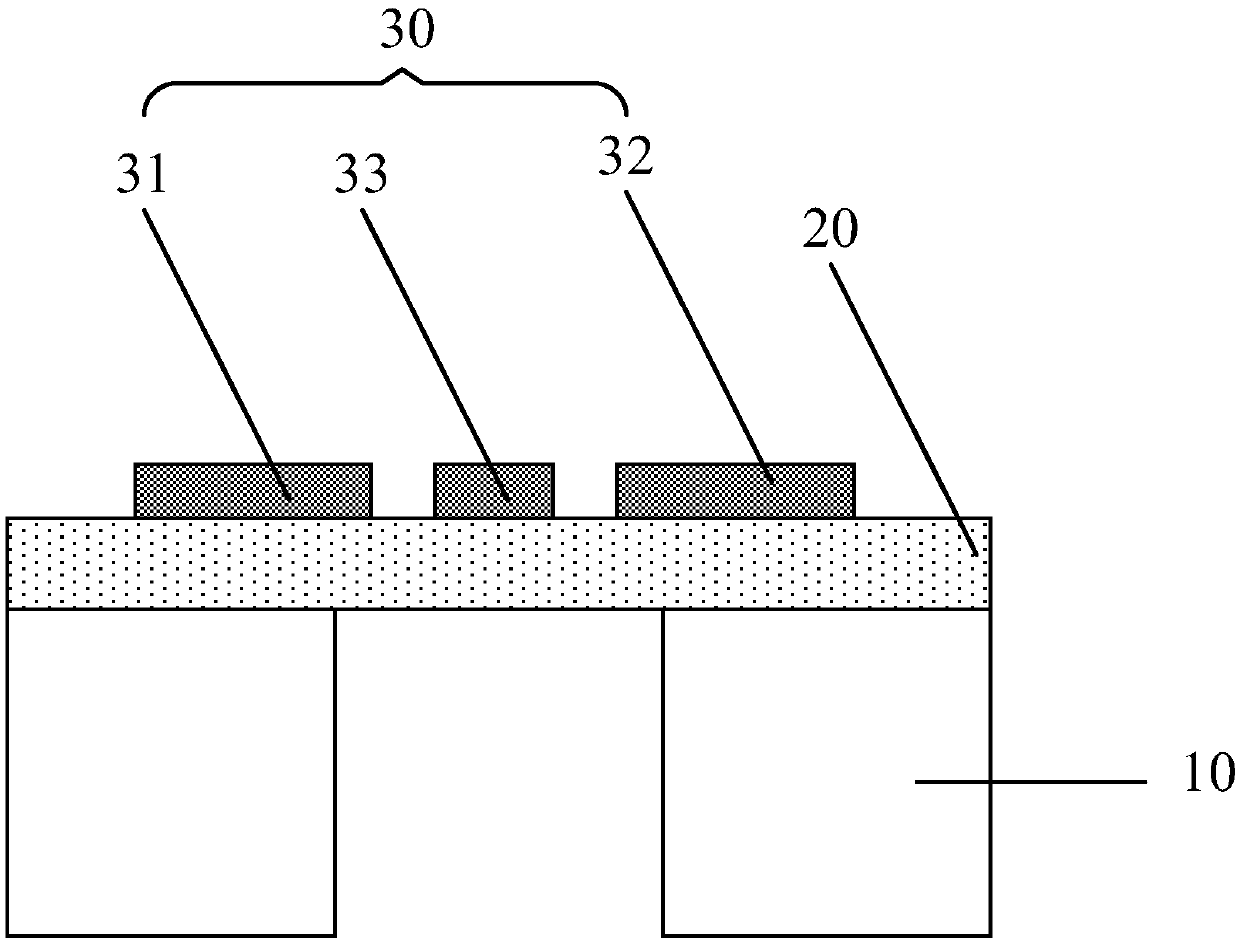

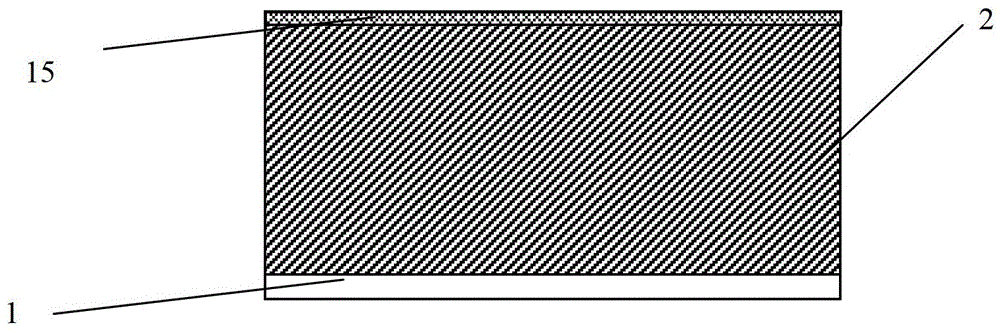

Semiconductor structure and preparation method thereof

PendingCN110943045AReduce parasitic resistanceIncrease contactTransistorSemiconductor/solid-state device manufacturingCapacitanceSemiconductor structure

The invention provides a semiconductor structure and a preparation method thereof, and the method at least comprises the steps: forming a plurality of active regions which are arranged at intervals ona semiconductor substrate, and forming a plurality of embedded gate assemblies in the active regions; forming a first isolation layer on the substrate; etching the first isolation layer to form a bitline contact hole; filling the line contact hole with a conductive material to form a bit line contact node having a first width, with a linear bit line having a second width less than the first width is formed over the bit line contact node. The bit line contact hole covers at least part of the active regions and part of the shallow trench isolation structure between the adjacent gate assembliesin the same active regions. The formed bit line is in good contact with a bit line contact node and well avoids a capacitor contact region. The optical proximity effect correction difficulty in the bit line forming process is reduced, the forming difficulty is reduced, and meanwhile the parasitic resistance in the bit line is effectively reduced. Reduction of the size of a memory is facilitated,and good functionality of the memory is ensured.

Owner:CHANGXIN MEMORY TECH INC

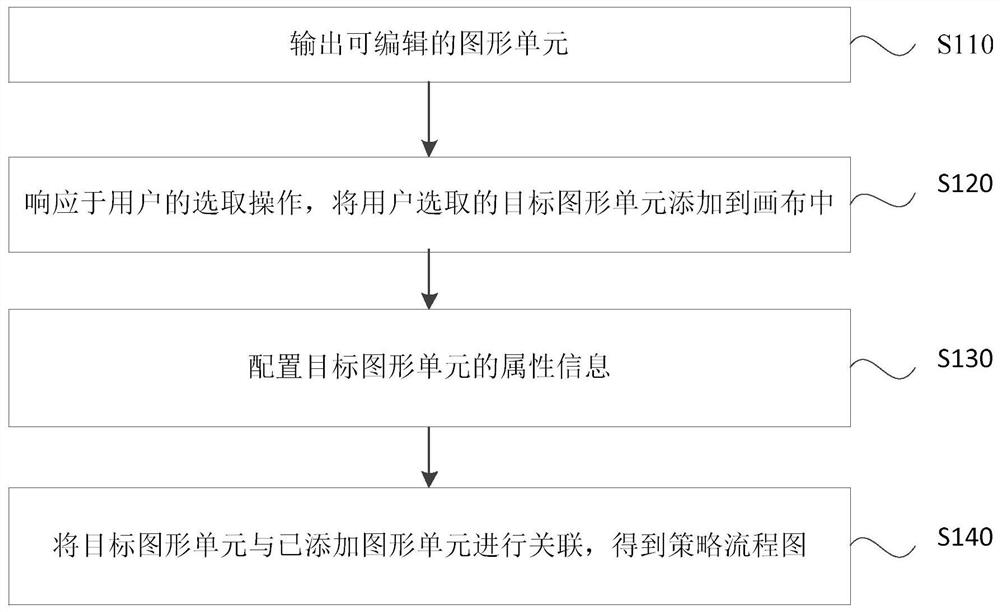

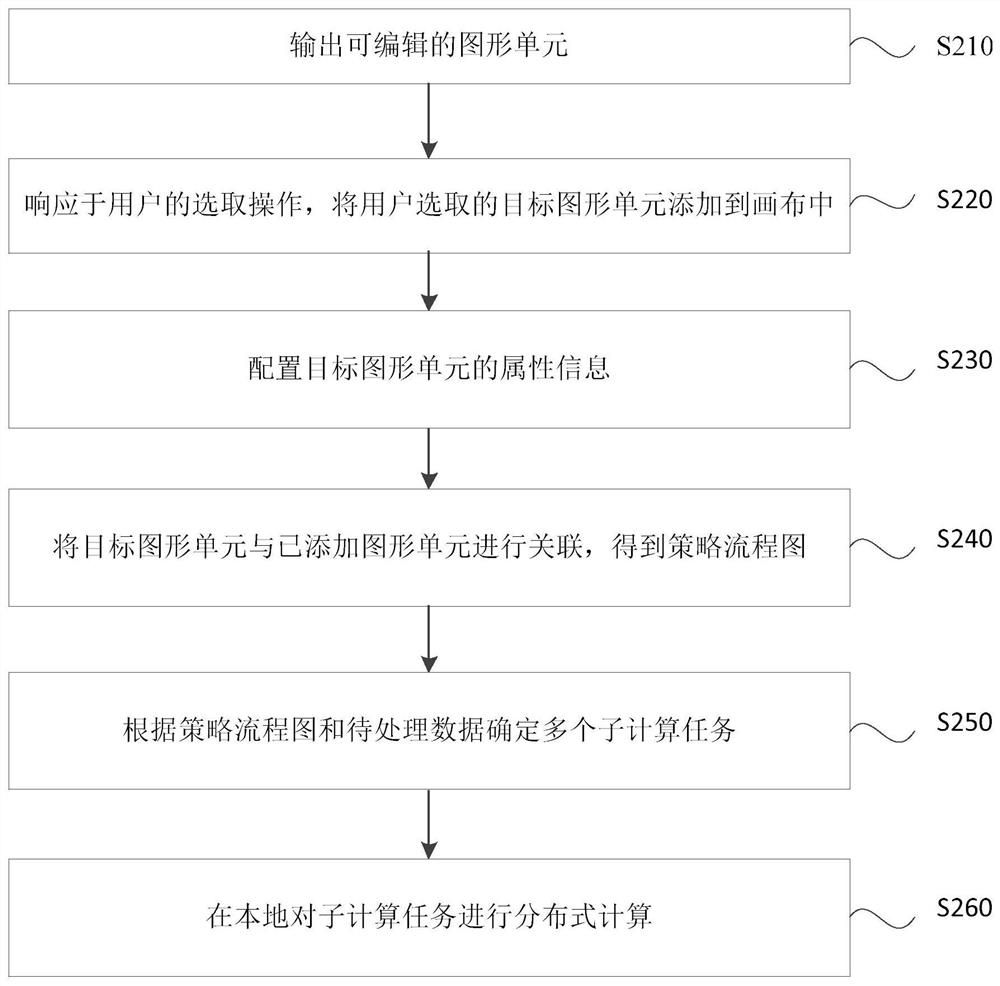

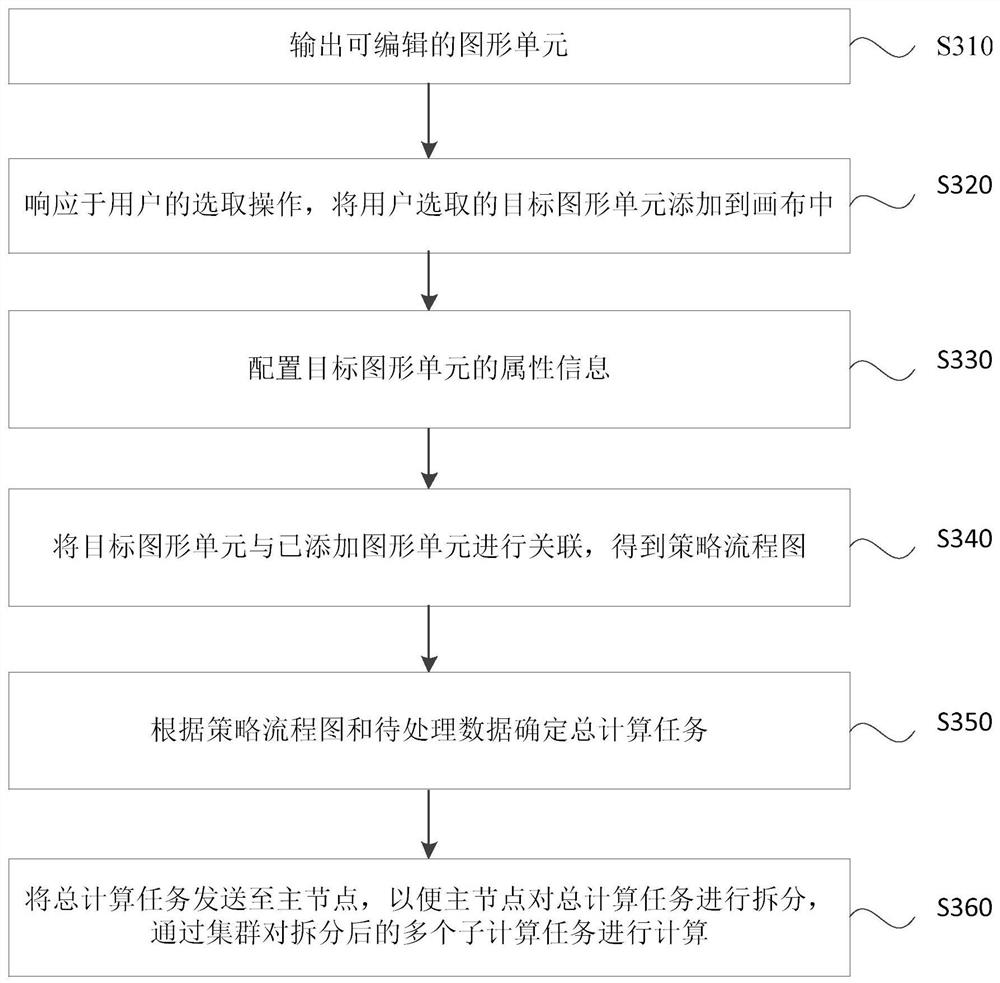

Strategy process processing method and device, computer equipment and storage medium

PendingCN112988305AImprove usabilityReduce the difficulty of formationSoftware engineeringExecution for user interfacesComputer equipmentComputer hardware

The invention discloses a strategy process processing method and device, computer equipment and a storage medium. The method comprises the following steps: outputting an editable graphic unit; in response to a selection operation of the user, adding a target graphic unit selected by the user into the canvas; configuring attribute information of the target graphic unit; and associating the target graph unit with the added graph unit to obtain a strategy flow chart. An editable graphic unit can be provided for a user, and the user can add a target graphic unit into a canvas through a selection operation. And the user configures attribute information of the target graphic unit and configures association between the target graphic unit and the added graphic unit to obtain the strategy flow chart. According to the technical scheme, a user does not need to edit codes, the user can quickly select the target graphic unit from the output editable graphic units through the visual graphic interface, the forming difficulty of the screening strategy process is reduced, and the usability of generation of the strategy process is improved.

Owner:CHINA CONSTRUCTION BANK

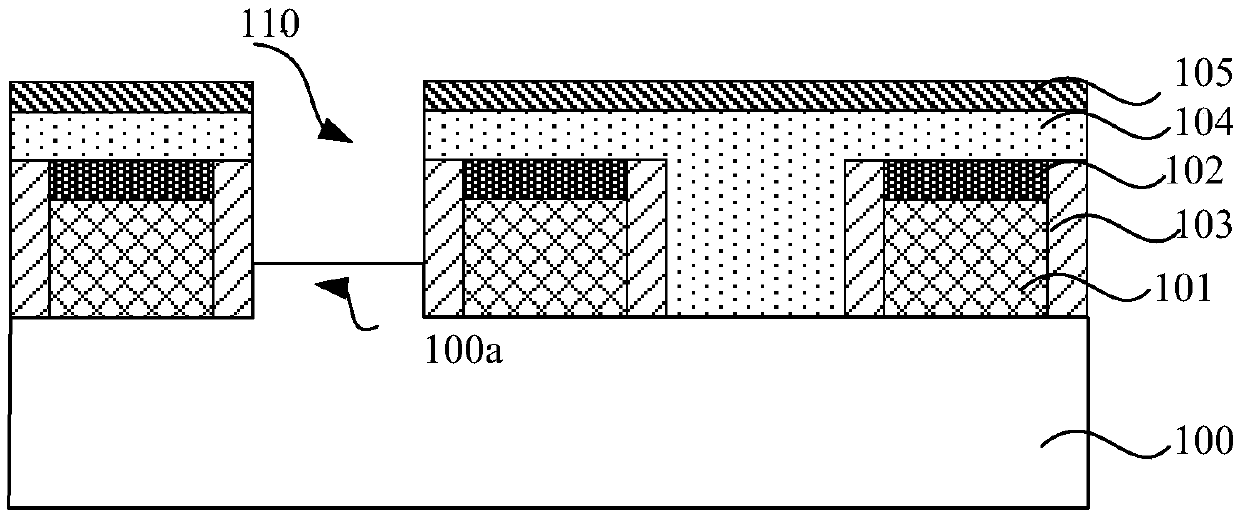

Contact plug, semiconductor device and manufacturing method thereof

ActiveCN110571188AReduce the difficulty of formationQuality improvementSemiconductor/solid-state device detailsSolid-state devicesDielectricEngineering

The invention provides a contact plug, a semiconductor device and a manufacturing method thereof to realize the manufacture of an alternative contact plug. A virtual contact only covering above a to-be-contacted region of a to-be-contacted structure can be removed with the assistance of a filling layer, in order to form a contact trench at the position of the virtual contact. A dielectric spacer is formed on the sidewall of the contact trench, and then a conductive material layer fills the space of the contact trench surrounded by the dielectric spacer to form the contact plug. This alternative process can reduce the difficulty in forming the contact plug, improve the quality of the formed contact plug, and increase the contact area of the formed contact plug by reducing the thickness of the dielectric spacer, reduce contact resistance, is applicable to the manufacture of the contact plug on a to-be-contacted structures such as gates, source-drain regions, and body regions, and can improve the performance of corresponding contact plugs and semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Heater structure, preparation method thereof and hydrogen sensor

PendingCN111278175AImproving the accuracy of structure detectionReduce the difficulty of formationOhmic-resistance heating detailsMaterial resistanceConductive pasteScreen printing

The invention discloses a heater structure, a preparation method thereof and a hydrogen sensor. An insulating film layer of the heater structure comprises a second pattern; the height of the second pattern is smaller than that of other areas of the insulating film layer; a formation region is defined for the heating structure formed in the second pattern, therefore, whenthe heating structure is prepared by utilizing a silk-screen printing process, only the conductive paste forming the heating structure needs to be printed in the second pattern, the forming difficulty of the heating structure is reduced, the shape precision of the formed heating structure is improved, the situation that the heating structure obtained through silk-screen printing is much larger than a designed pattern is avoided, and the detection precision of the heater structure is improved.

Owner:SAIC MOTOR

Cooling process for green pole plate of lead-acid storage battery after curing

ActiveCN107068984AIncrease difficulty of formationReduce capacityLead-acid accumulator electrodesRoom temperatureEngineering

The invention discloses a cooling process for a green pole plate of a lead-acid storage battery after curing, and aims to overcome the defects that the cooling time is long after the pole plate of the storage battery is cured and a lattice structure between an active substance on a surface of the pole plate and a grid is not stable so as to improve defective rate of the pole plate, and the surface of the pole plate is easy to carbonize so as to improve the formation difficulty of the pole plate and reduce the capacity and the cycle lifetime of the battery. The cooling process comprises the following steps of (a) placing the green pole plate which is cured just now in a curing chamber under a normal-temperature environment for normal-temperature cooling for 0.5-1.5 hours; (b) performing temperature reduction on the curing chamber placed with the green pole plate, adjusting a temperature to 5-10 DEG C, simultaneously blowing air by a fan, and controlling time for 2-3 hours; and (c) placing the green pole plate in the curing chamber under a room-temperature ventilation environment for 0.5-1 hour, wherein pole separation and brush can be performed.

Owner:CHAOWEI POWER CO LTD

A close-cut fracturing method

ActiveCN112177583BReduced displacement requirementsFacilitate control of the opening sequenceFluid removalThermodynamicsPrincipal stress

The invention relates to a close-cut fracturing method. The method includes: evaluation of shale parameters and optimization of fracture parameters and fracturing construction parameters; performing a first perforation operation; fracturing treatment; liquid rubber plug of the agent; replacement operation; carry out the second perforation operation; fracturing treatment, replacement operation; temporary plugging of the reconstructed perforation cluster; fracturing treatment for the unmodified perforation cluster; replacement operation; next Insert the bridge plug, repeat the above until all constructions are completed; drill the plug after pressing, flow back, test and produce. Through two perforation operations and temporary plugging in a single stage, the difficult operation of 5-8 clusters was transformed into a 3-stage fracturing operation, thereby reducing the conventional single-stage 3-6 clusters to a single-stage 1-2 cluster fracturing operation, increasing the single-cluster fluid intake, reducing the demand for displacement in fracturing construction, and increasing the construction pressure window; at the same time, the horizontal principal stress difference is reduced through stress shadowing, which increases the complexity of fractures and increases the depth of Shale gas well stimulation volume.

Owner:CHINA PETROLEUM & CHEM CORP +1

Cooling treatment process after solidification of raw plate of lead-acid battery

ActiveCN107068984BReduce humidityEasy to operateLead-acid accumulator electrodesRoom temperatureTime control

The invention discloses a cooling process for a green pole plate of a lead-acid storage battery after curing, and aims to overcome the defects that the cooling time is long after the pole plate of the storage battery is cured and a lattice structure between an active substance on a surface of the pole plate and a grid is not stable so as to improve defective rate of the pole plate, and the surface of the pole plate is easy to carbonize so as to improve the formation difficulty of the pole plate and reduce the capacity and the cycle lifetime of the battery. The cooling process comprises the following steps of (a) placing the green pole plate which is cured just now in a curing chamber under a normal-temperature environment for normal-temperature cooling for 0.5-1.5 hours; (b) performing temperature reduction on the curing chamber placed with the green pole plate, adjusting a temperature to 5-10 DEG C, simultaneously blowing air by a fan, and controlling time for 2-3 hours; and (c) placing the green pole plate in the curing chamber under a room-temperature ventilation environment for 0.5-1 hour, wherein pole separation and brush can be performed.

Owner:CHAOWEI POWER CO LTD

Semiconductor structure and forming method thereof

PendingCN114792683AImprove performanceLower resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductor structureElectrical connection

The invention discloses a semiconductor structure and a forming method thereof. The semiconductor structure comprises a substrate; the gate structure is separated from the substrate and comprises a gate contact region which is in contact with the gate plug; the source-drain doped region comprises a source-drain contact region and a source-drain connection region; the dielectric structure layer is positioned on the substrate at the side part of the gate structure and covers the source-drain doped region and the gate structure; the source-drain contact structure is in contact with the source-drain doped region, the source-drain contact structure is of an integrated structure and comprises a source-drain plug penetrating through the dielectric structure layer of the source-drain contact region and a source-drain contact layer located in the dielectric structure of the source-drain connection region, and the top surface of the source-drain contact layer is lower than the top surface of the source-drain plug; the source-drain contact structure and the dielectric structure layer enclose an interval opening; the interval dielectric layer is filled in the interval opening; and the gate plug is positioned at the top of the gate structure of the gate contact region and is in contact with the gate structure. According to the embodiment of the invention, the source-drain contact structure is an integrated structure, and the electrical connection performance between the source-drain plug and the source-drain contact layer is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Contact plug, semiconductor device and method of manufacturing the same

ActiveCN110571188BReduce the difficulty of formationQuality improvementSemiconductor/solid-state device detailsSolid-state devicesDielectricDevice material

The invention provides a contact plug, a semiconductor device and a manufacturing method thereof, which can realize the manufacture of a replacement contact plug, and can cover only the area to be contacted of the structure to be contacted with the assistance of a filling layer. The dummy contact is removed to form a contact trench at the position of the dummy contact, and a dielectric spacer is formed on the sidewall of the contact trench, and then a conductive material layer is filled in the space of the contact trench surrounded by the dielectric sidewall , to form contact plugs, this alternative process can reduce the difficulty of forming contact plugs, improve the quality of the formed contact plugs, and can increase the contact area of the formed contact plugs by reducing the thickness of the dielectric sidewall , reducing contact resistance, suitable for the manufacture of contact plugs on gates, source and drain regions, body regions and other contact structures, and can improve the performance of corresponding contact plugs and semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

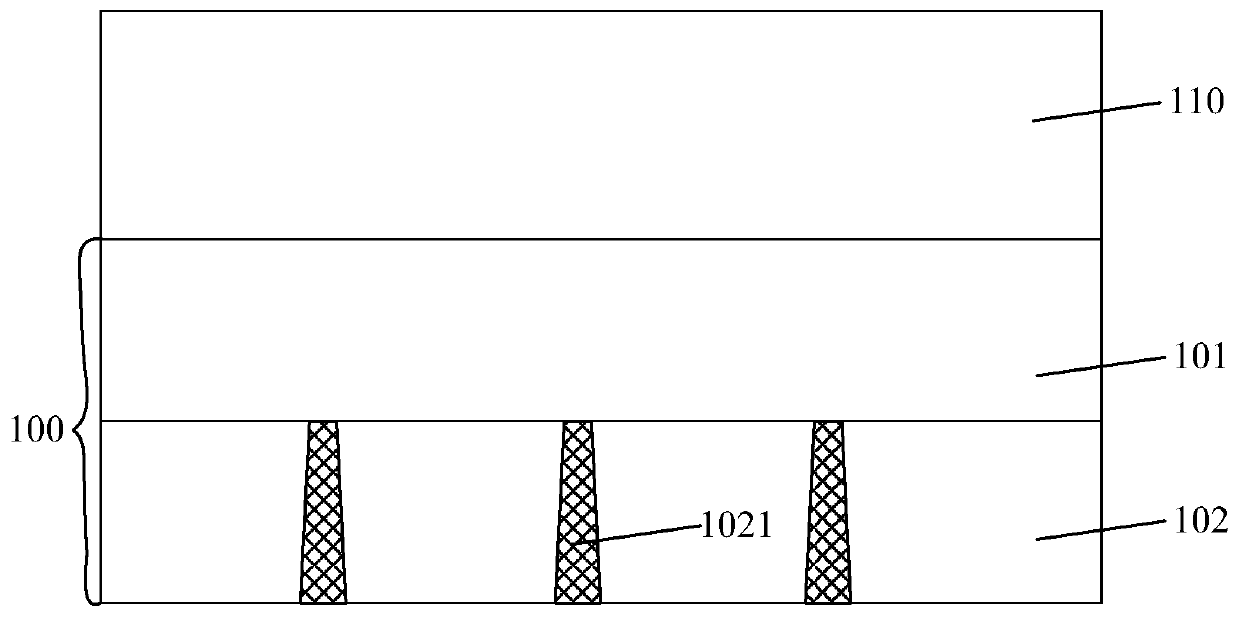

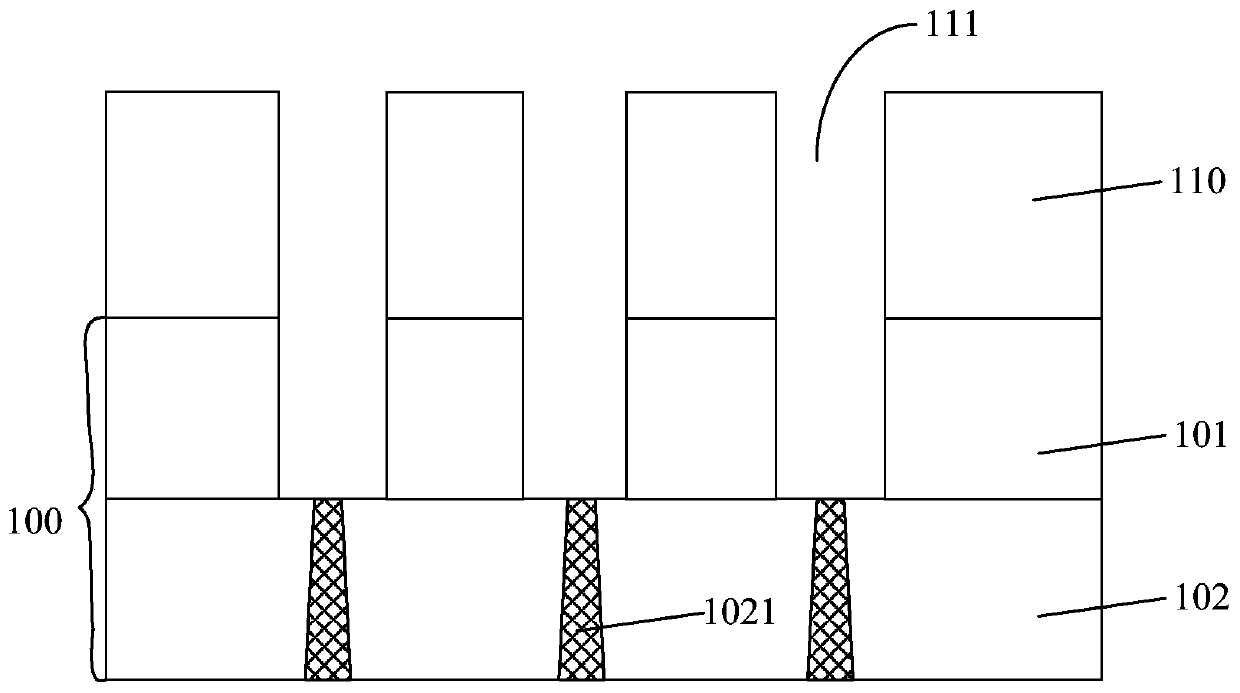

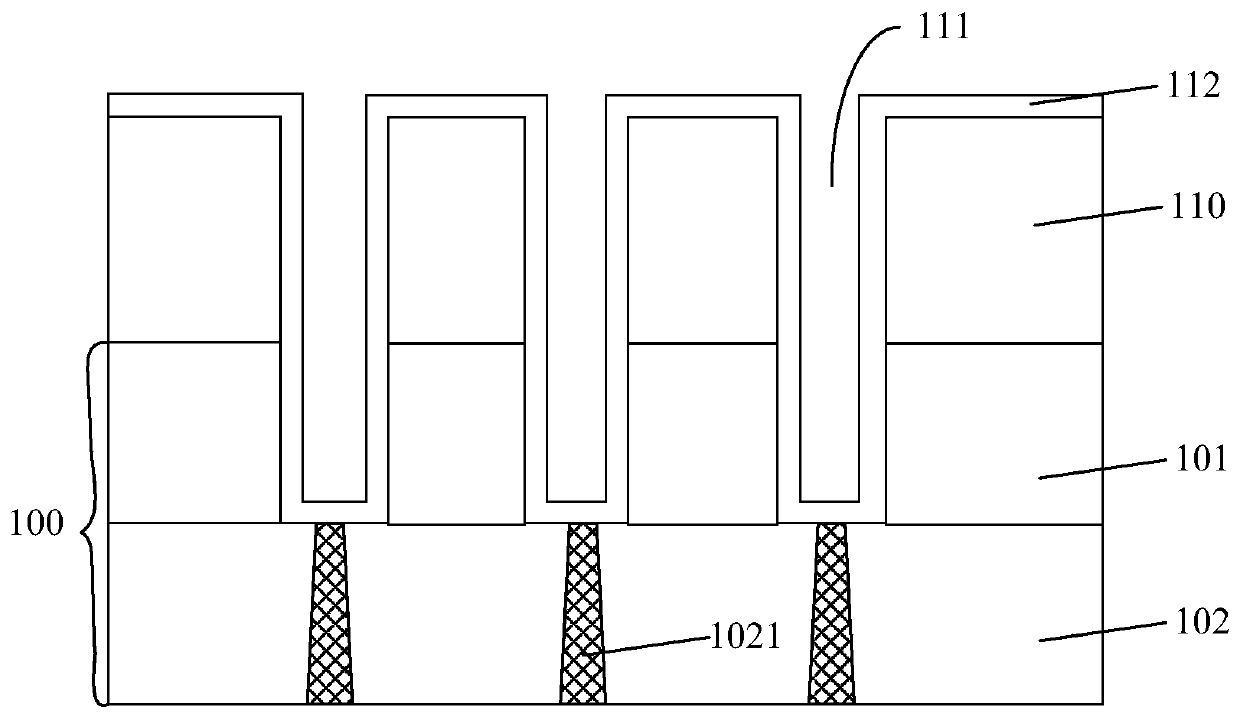

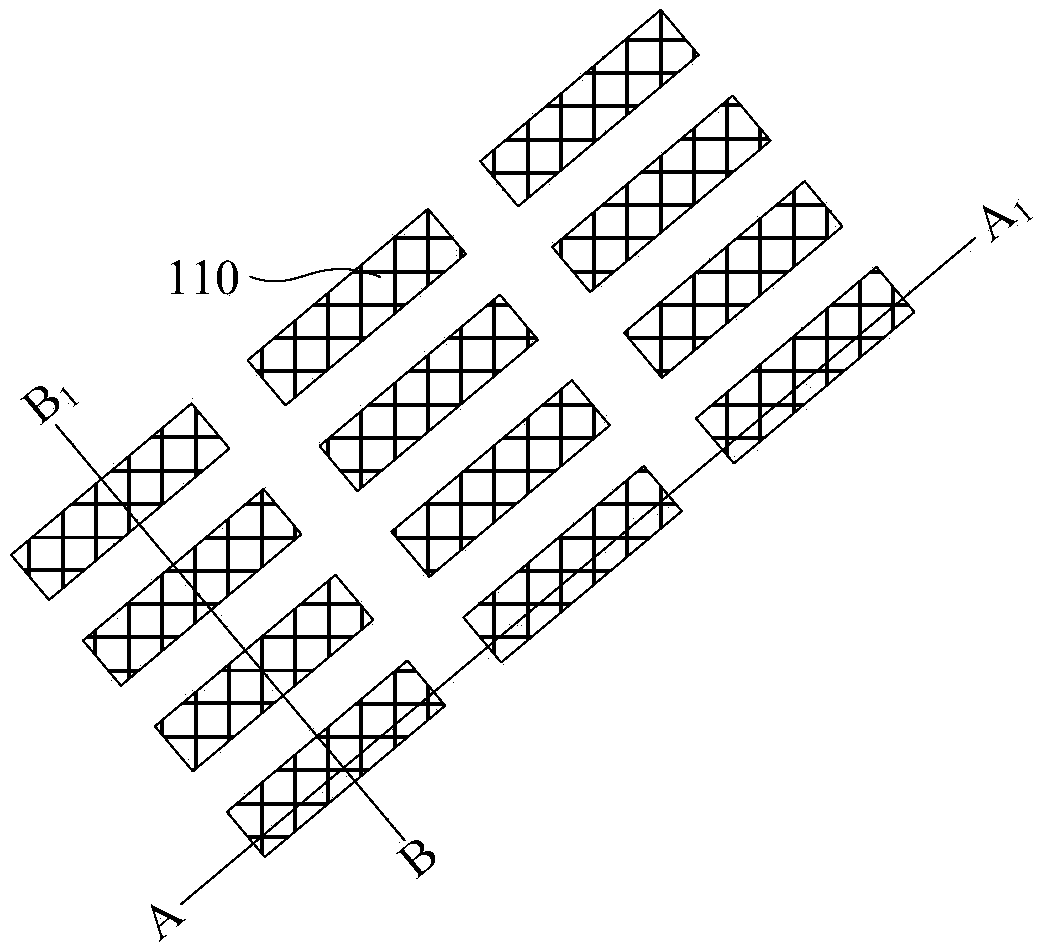

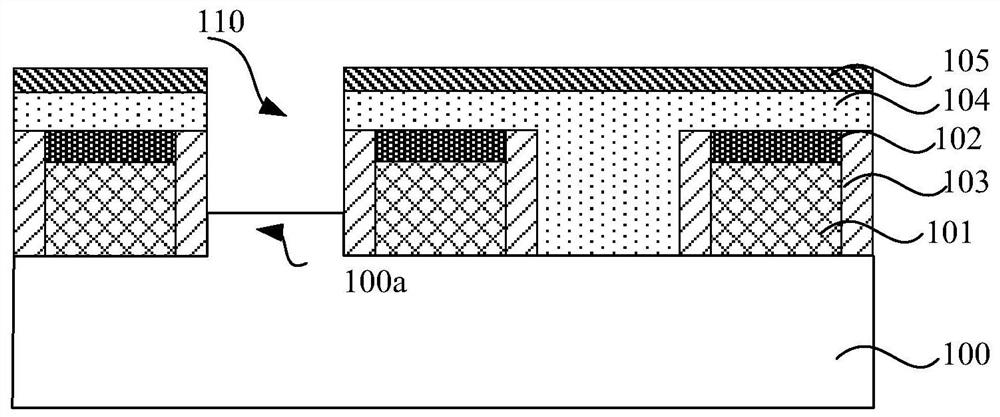

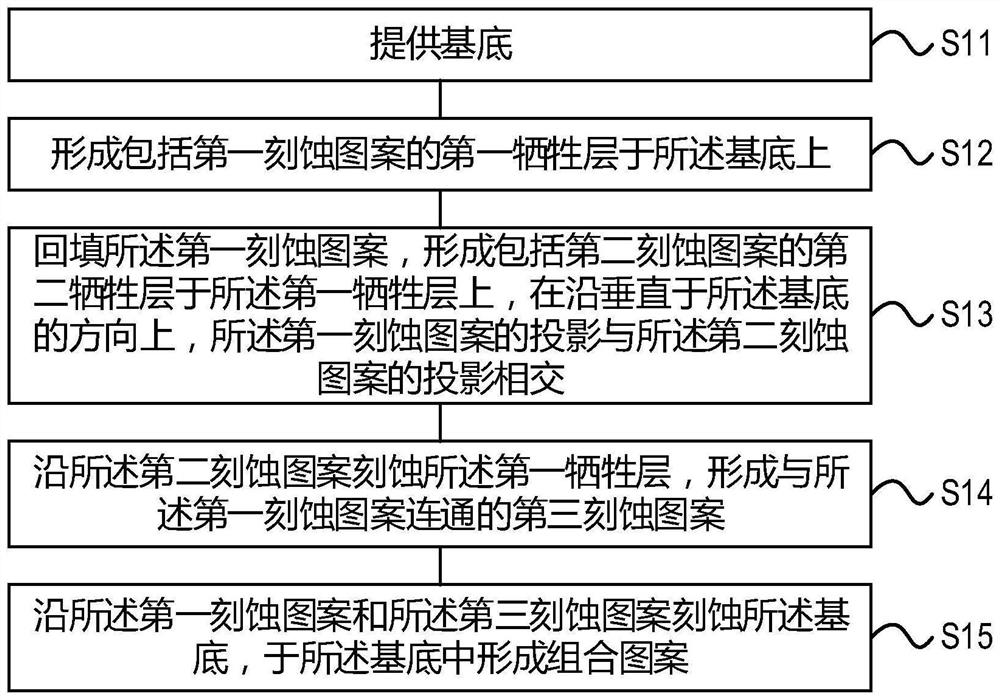

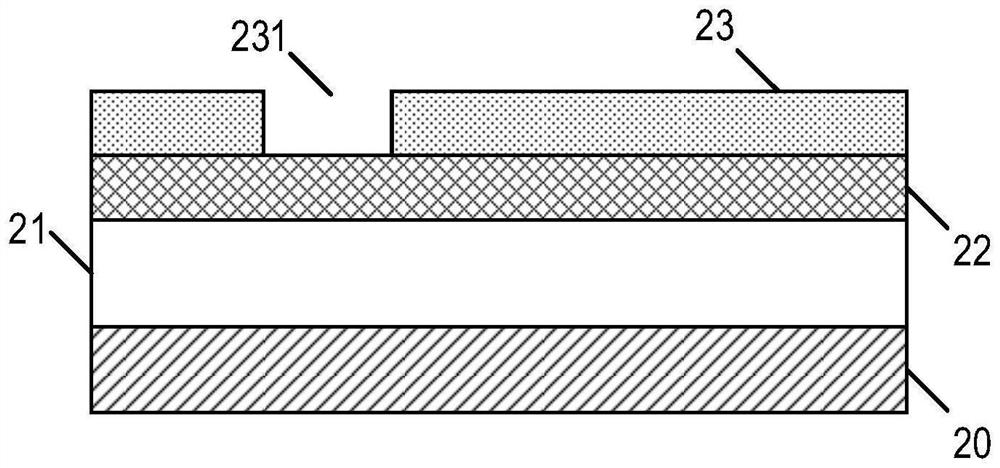

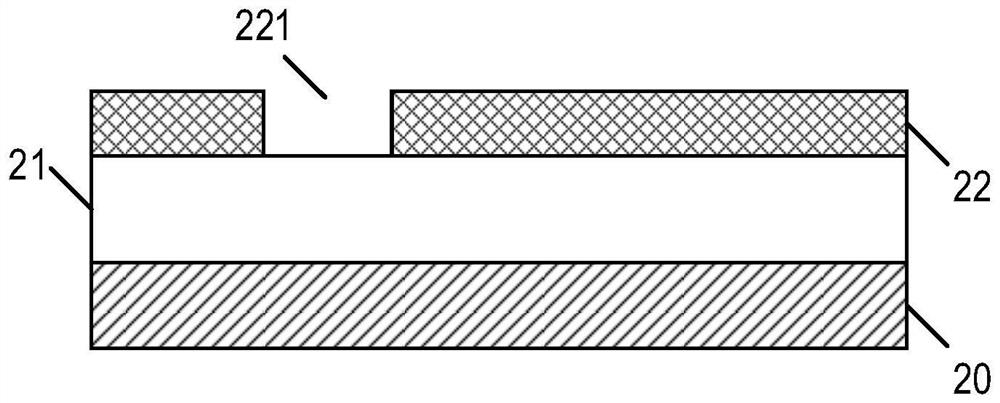

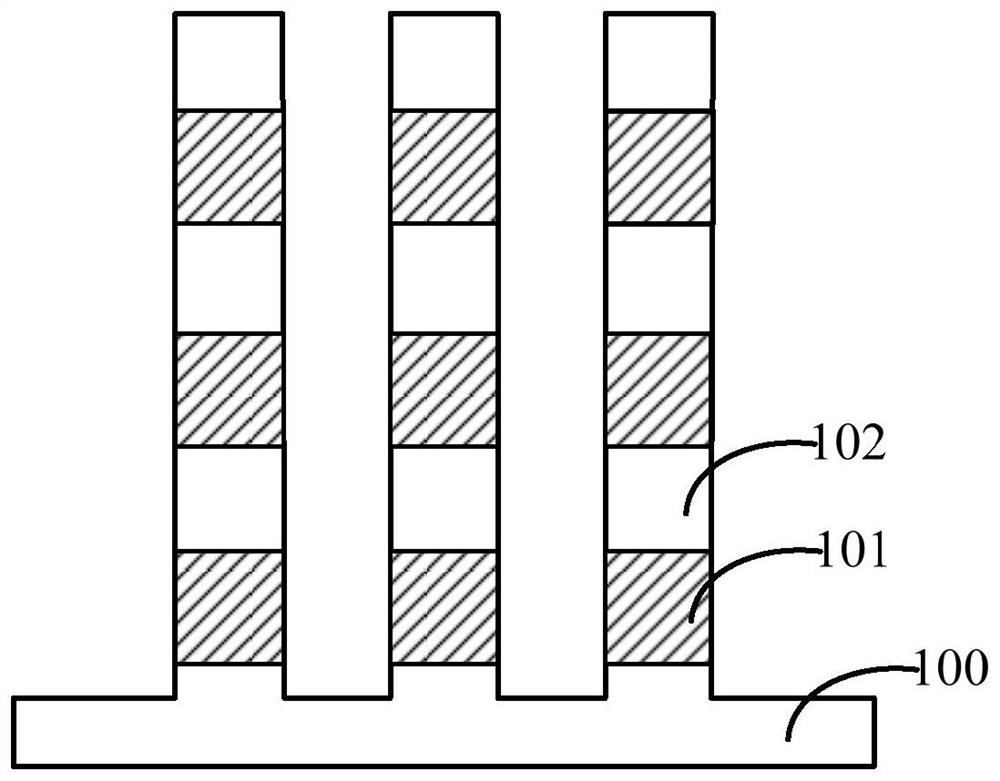

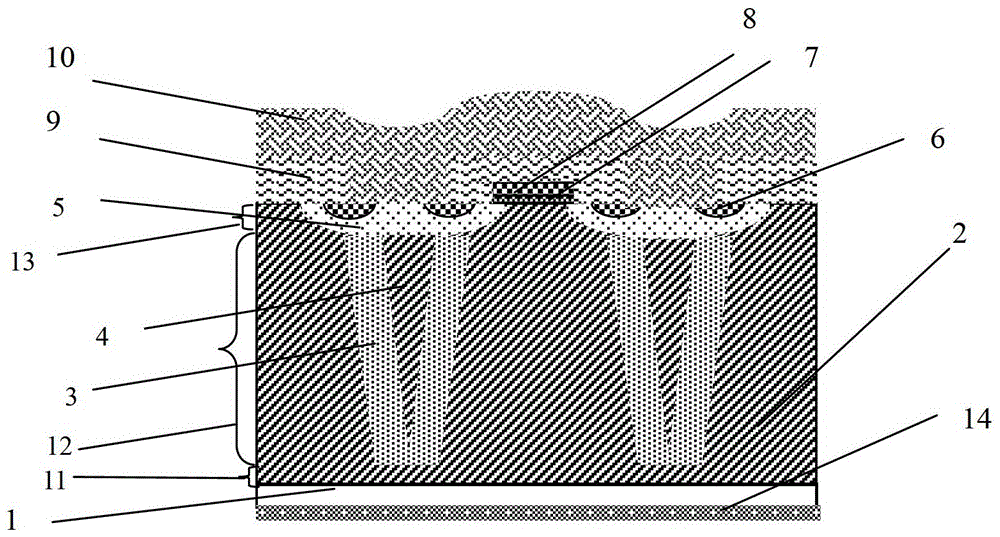

Three-dimensional memory and forming method thereof

PendingCN114121981AImprove performanceReduce the difficulty of formationSolid-state devicesSemiconductor devicesEngineeringMaterials science

The invention relates to a three-dimensional memory and a forming method thereof. The forming method of the three-dimensional memory comprises the following steps: providing a substrate; forming a first sacrificial layer including a first etching pattern on the substrate; the first etching pattern is backfilled, a second sacrificial layer comprising a second etching pattern is formed on the first sacrificial layer, and the projection of the first etching pattern intersects with the projection of the second etching pattern in the direction perpendicular to the substrate; etching the first sacrificial layer along the second etching pattern to form a third etching pattern communicated with the first etching pattern; and etching the substrate along the first etching pattern and the third etching pattern, and forming a combined pattern in the substrate. According to the invention, the morphology of the finally formed combined pattern is improved.

Owner:YANGTZE MEMORY TECH CO LTD

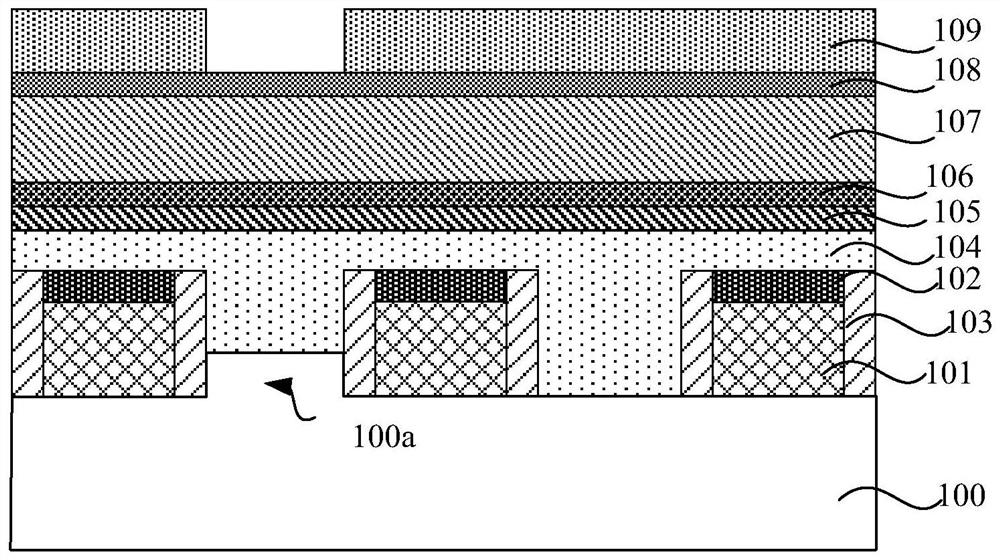

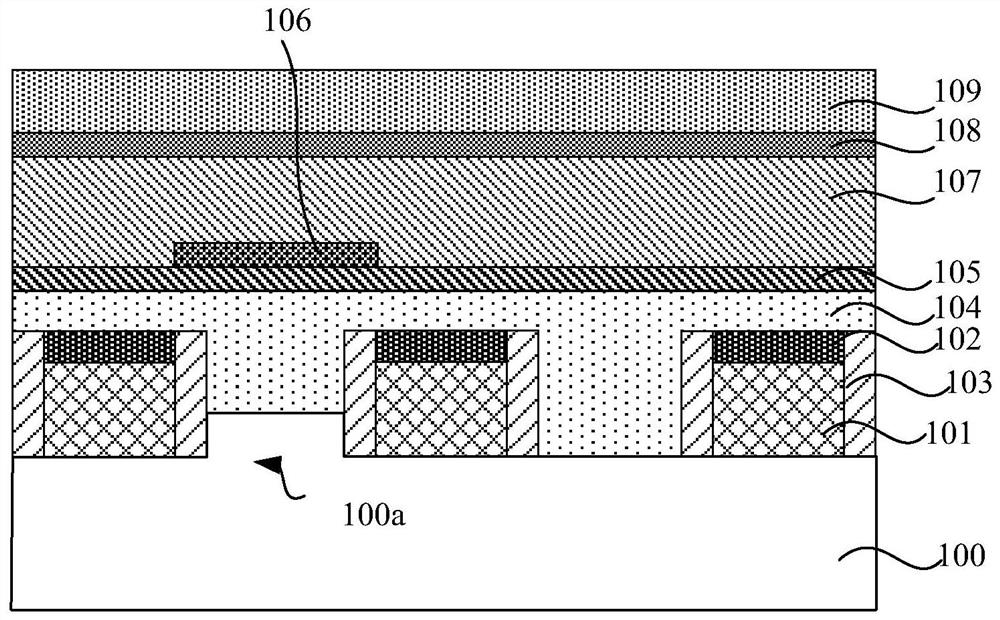

Memory and manufacturing method thereof

InactiveCN110600480AReduce the difficulty of formationQuality improvementSolid-state devicesSemiconductor devicesProtection layerElectrical and Electronics engineering

The embodiment of the invention discloses a memory and a manufacturing method thereof. The method comprises the steps of forming an epitaxial layer in a groove of a substrate; forming a protection layer covering the epitaxial layer in the groove; forming a stack structure on the protection layer, wherein the stack structure is used for forming a gate of a memory unit in the memory and the gate isused for controlling on or off of the memory unit; forming a through hole which penetrates through the stack structure and exposes the protection layer; removing the protection layer and exposing theepitaxial layer; and forming a channel region of the memory unit in the through hole, wherein the channel region is connected with the epitaxial layer and is used for the memory unit to store chargescorresponding to written data.

Owner:YANGTZE MEMORY TECH CO LTD

Formation method of semiconductor device

PendingCN114156182AAvoid formingPromote formationNanoinformaticsSolid-state devicesDevice materialDielectric layer

The invention relates to a semiconductor device forming method, which comprises the steps of providing a substrate, and forming a plurality of initial fin parts which are separately arranged on the substrate; forming an isolation structure on the substrate; forming connecting layers on the side walls of the initial fin parts and between the adjacent initial fin parts; forming a dummy gate structure crossing the initial fin part and the connecting layer on the substrate, wherein the dummy gate structure covers the side wall of the connecting layer and part of the top surface of the initial fin part; forming grooves in the initial fin parts at the two sides of the dummy gate structures, and forming source-drain doping layers in the grooves; a dielectric layer is formed on the substrate, the dielectric layer covers the dummy gate structure and the source-drain doped layer, and the top surface of the dielectric layer is flush with the top surface of the dummy gate structure; removing the dummy gate structure to form a gate structure; according to the invention, the quality of the finally formed semiconductor device can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

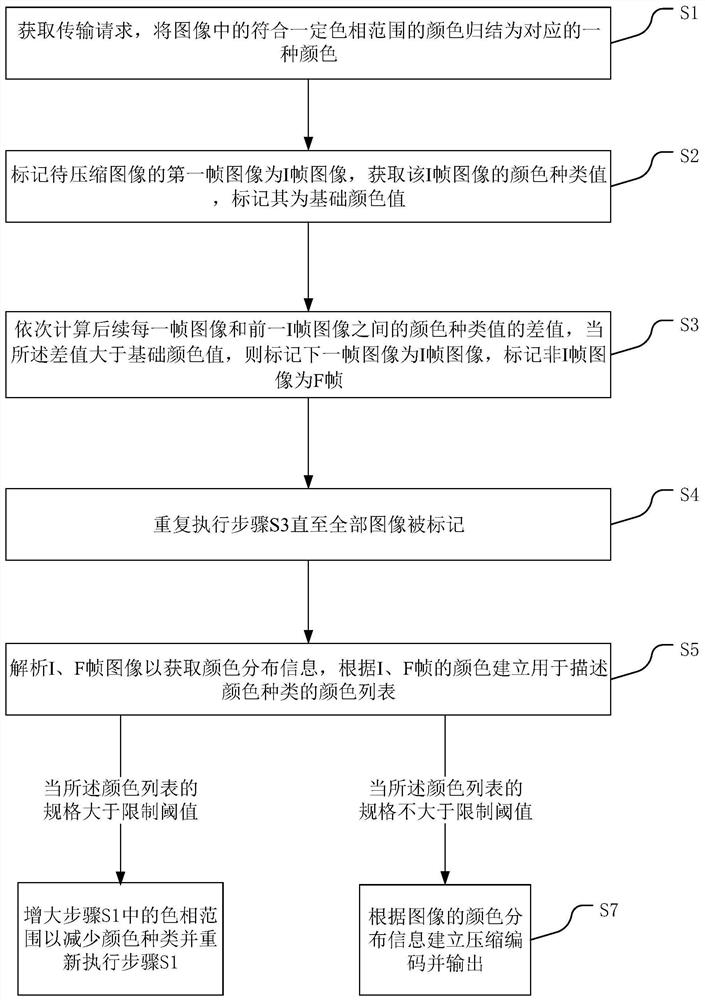

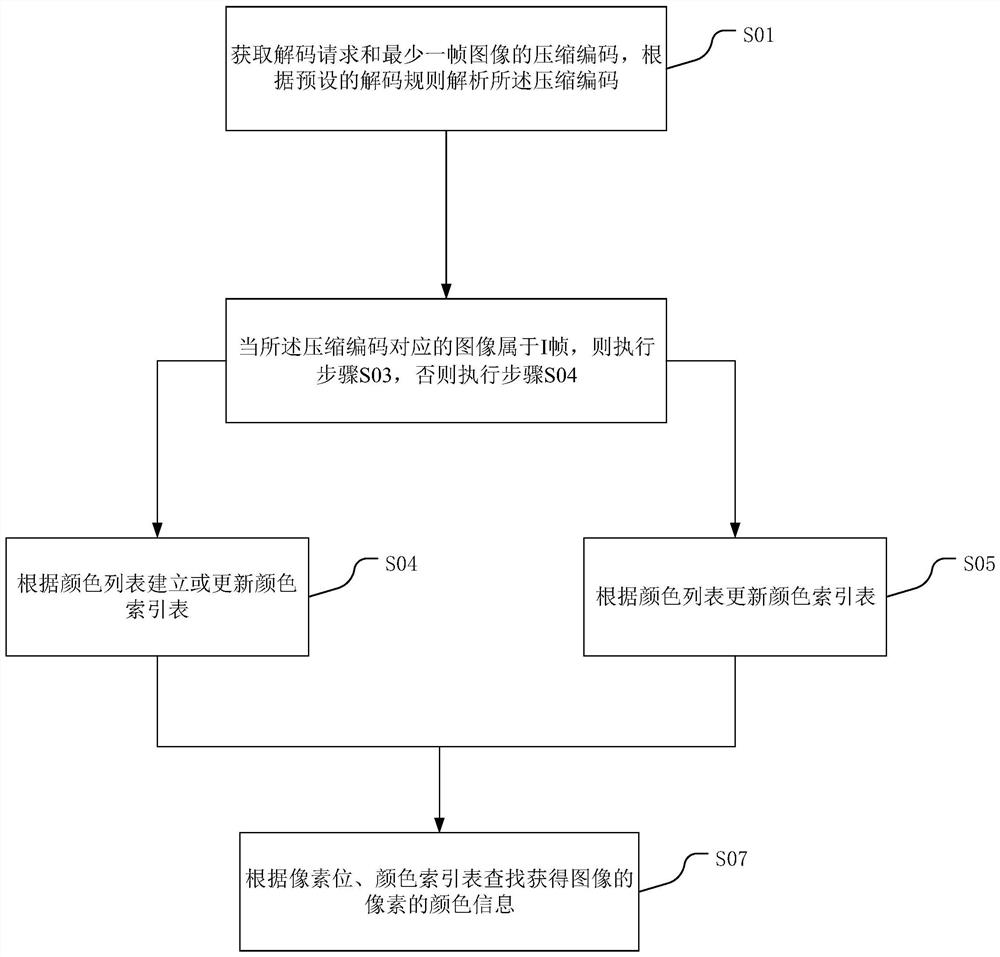

A lossy image compression transmission method and system

ActiveCN109819254BReduce the difficulty of formationReduce difficultyDigital video signal modificationComputer graphics (images)Engineering

The invention discloses a lossy image compression transmission method and system. The encoding process is: S1, attribute the colors that meet the range into one color; S2, mark the first frame as an I frame, obtain the color type value, and mark it as the basis Color value; S3, calculate the difference, when the difference is greater than the basic color value, then mark the next frame as an I frame, otherwise it is an F frame; S5, analyze the I and F frames to obtain color distribution information and establish a color list, the color list is greater than threshold, execute S6, otherwise S7; S6, reduce color types and re-execute S1; S7, establish compression code according to the color distribution information and output it. The system is used to execute the method. The present invention reduces the difficulty of forming the color list by distinguishing the type of the frame, improves the compression loss rate through the limitation of the color list, reduces the difficulty of data transmission, can reasonably complete the compression of the image and can reduce the difficulty of data transmission according to the requirements, and is beneficial in Used in IoT systems with low processing power.

Owner:SHENZHEN ZHANYIN TECH CO LTD

Three-dimensional memory, preparation method thereof and electronic equipment

ActiveCN111341775AStructure does not affectSimple structureSolid-state devicesSemiconductor devicesEngineering physicsMaterials science

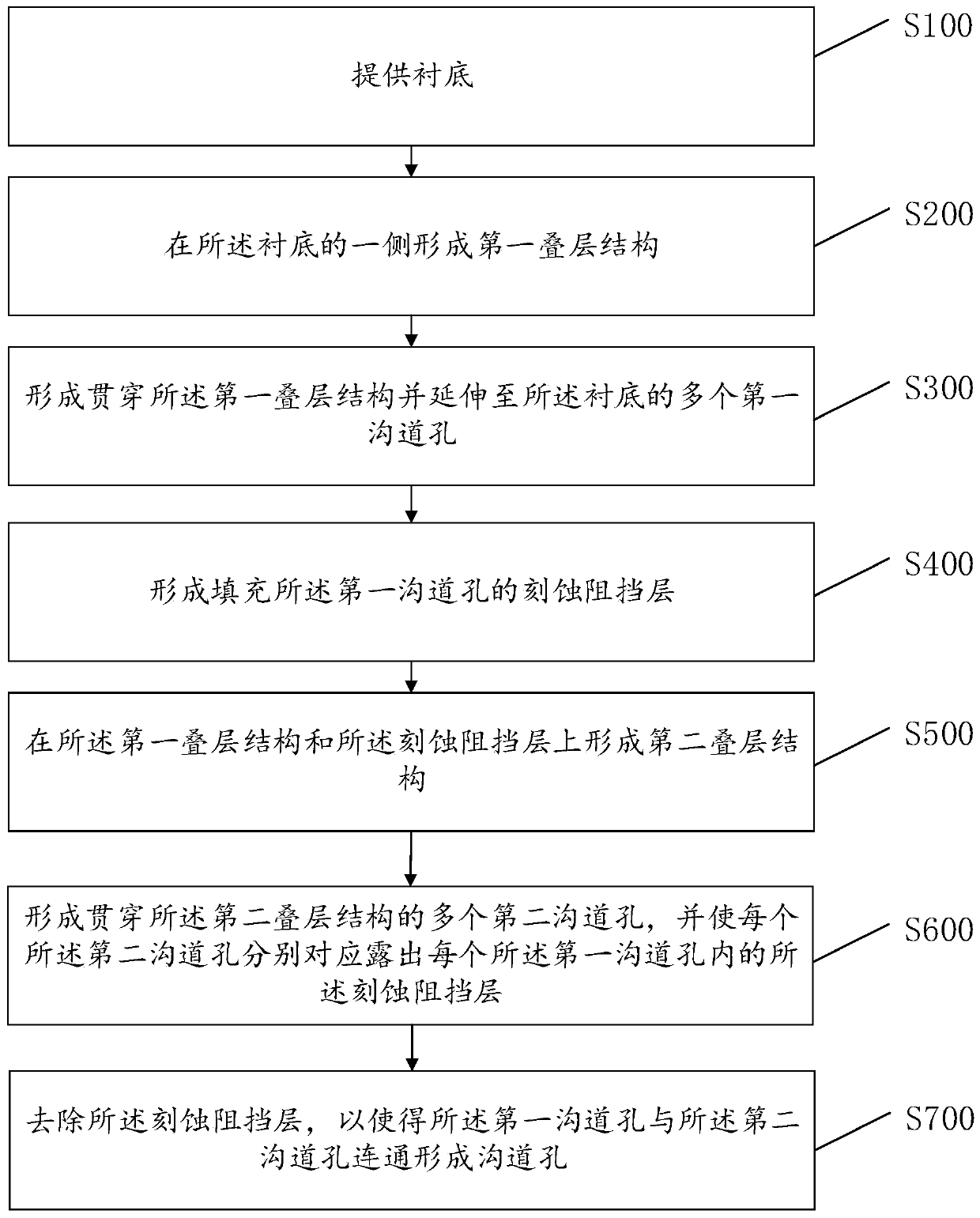

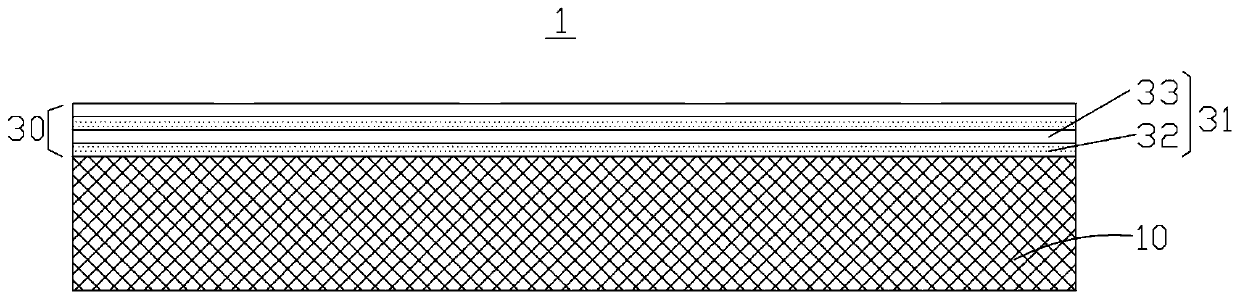

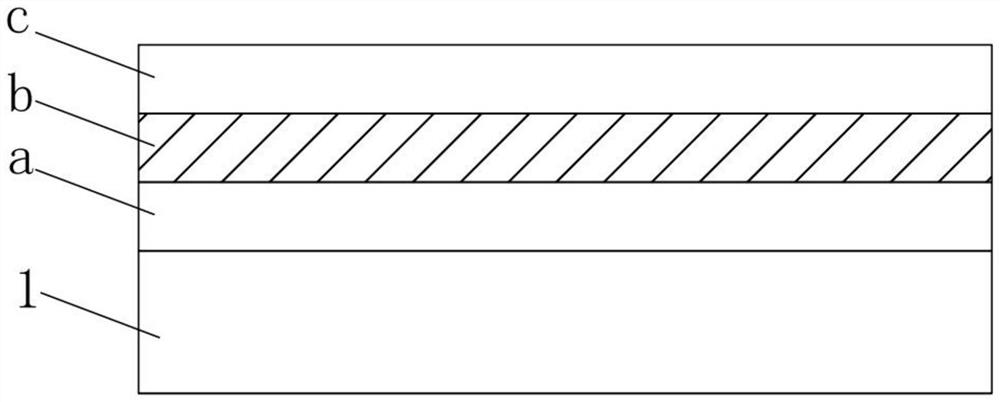

The invention provides a three-dimensional memory, a preparation method thereof and electronic equipment. The preparation method comprises the following steps: providing a substrate; forming a first laminated structure on one side of the substrate; forming a plurality of first channel holes which penetrate through the first laminated structure and extend to the substrate; forming an etching barrier layer filling the first channel holes; forming a second laminated structure on the first laminated structure and the etching barrier layer; forming a plurality of second channel holes penetrating through the second laminated structure; and removing the etching barrier layer to enable the first channel holes and the second channel holes to be communicated to form channel holes. The channel holes,which are formed in one step in related technologies, are formed in two steps in the method of the invention. The first channel holes close to the bottom are first formed, and then the other second channel holes communicated with the first channel holes are formed. According to the forming method provided by the invention, the forming difficulty of the channel holes can be reduced, the channel holes with excellent structures are formed, and the uniformity of the depth of the channel holes is improved.

Owner:YANGTZE MEMORY TECH CO LTD

Battery positive electrode material, its preparation method and battery

ActiveCN105161683BIncrease contentIncrease capacityLead-acid accumulator electrodesLead dioxideSulfur

The invention provides a battery cathode material. The battery cathode material comprises sulfur particles, a conductive additive and graphene, wherein the sulfur particles are loaded on the surface of the conductive additive; the conductive additive and the sulfur particles are wrapped into the graphene; and the conductive additive comprises the following constituents based on weight: 1-10 parts of Pb3O4 and 25-50 parts of Beta-PbO2. By the battery cathode material, the content of lead dioxide is increased, the polar plate formation difficulty is reduced, and the capacity of a polar plate is improved; with the addition of the Beta-PbO2, the capacity of a battery can be improved, and meanwhile, the charging and discharging voltage of the battery is increased slightly; and by adjusting the proportion of the Pb3O4 and Beta-PbO2, the strength of the polar plate, the charging and discharging voltage at an early stage, the charging and discharging voltage at a post stage, the cyclic post-stage capacity and the like are improved to an ideal level.

Owner:无锡品源知识产权顾问有限公司

Additive of lead-zinc accumulator positive material and modified alkaline accumulator positive material

InactiveCN100459241CIncrease capacityIncrease charge and discharge voltageAlkaline accumulator electrodesComposition BPolymer chemistry

The disclosed additive for positive pole of accumulator is composed of composition A and composition B according to weight ratio 1:2.8-3. Composition A contains Pb3O4 equal to or larger than 75%, and surplus is beta - PbO2. Composition B contains beta - PbO2 equal to or larger than 80%, and surplus is PbSO4. The invention also discloses a modified anode material of accumulator of using the said additive. The additive and anode material of accumulator can raise capacity of first time and cycle life of accumulator.

Owner:赵恒祥

Infrared detector and its manufacturing method

ActiveCN111106203BImprove quantum efficiencyIncrease flexibilityFinal product manufactureVacuum evaporation coatingHeterojunctionPhysical chemistry

The invention discloses a manufacturing method of an infrared detector. The manufacturing method comprises: forming a detector mesa on an N-type substrate, and the detector mesa includes N-type InAsP / InAsSb superstructures formed sequentially on the N-type substrate. Lattice absorption layer, InPSb barrier layer and N-type InAsP / InAsSb superlattice contact layer; the first electrode is formed on the N-type InAsP / InAsSb superlattice contact layer on the detector table, and formed on the N-type substrate A second electrode corresponding to the detector mesa. The invention also discloses an infrared detector manufactured by the above manufacturing method. The invention solves the problem that it is difficult to form a heterojunction structure in the manufacturing process of the infrared detector.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Method of forming contact plugs

ActiveCN105097650BEasy to fillReduce the difficulty of formationSemiconductor/solid-state device manufacturingConductive materialsDielectric layer

A formation method of a contact plug comprises the steps of providing a substrate; forming an interlayer dielectric layer on the substrate; forming a high K dielectric layer on the interlayer dielectric layer; etching the high K dielectric layer and the interlayer dielectric layer orderly until the substrate is exposed to form a contact hole; continuously etching the high K dielectric layer along the contact hole until the diameter of the contact hole located at the high K dielectric layer is increased; adopting a conductive material to fill the contact hole. The formation method of the contact plug enables the formation difficulty of the contact plug to be reduced and also the quality of the formed contact plug to be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A kind of semiconductor device and its forming method

ActiveCN104183641BImprove uniformityImprove balanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerSemiconductor

Disclosed in the invention is a semiconductor device comprising a semiconductor substrate, a semiconductor drift region, base electrode regions, source regions, a grid dielectric layer, a grid electrode, metal pre dielectric layers, and a second electrode. To be specific, a first electrode is formed at one side of the semiconductor substrate. The semiconductor drift region is formed by a first drift region, a second drift region, and a third drift region; and the first drift region, the second drift region, and the third drift region are stacked at the other side of the semiconductor substrate upwardly in sequence. The base electrode regions are formed inside the third drift region. The source regions are formed inside the base electrode region. The grid dielectric layer is formed on the third drift region and is located between the two base electrode regions. The grid electrode is formed on the grid dielectric layer. The metal pre dielectric layers are formed around the grid electrode and at the top of the third drift region except the portion between the two source regions. The second electrode is formed on the grid electrode, the metal pre dielectric layers, and the third drift region between the two source regions. In addition, the invention also discloses a forming method of the semiconductor device. Therefore, the charge balance capability of the super junction drift region can be effectively improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com