Semiconductor structure and preparation method thereof

A semiconductor and isolation structure technology, which is applied in the field of semiconductor structure and its preparation, can solve the problems of difficult production, device size reduction, large parasitic resistance, etc., and achieve the effect of reducing the difficulty of forming, reducing the parasitic resistance, and reducing the parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

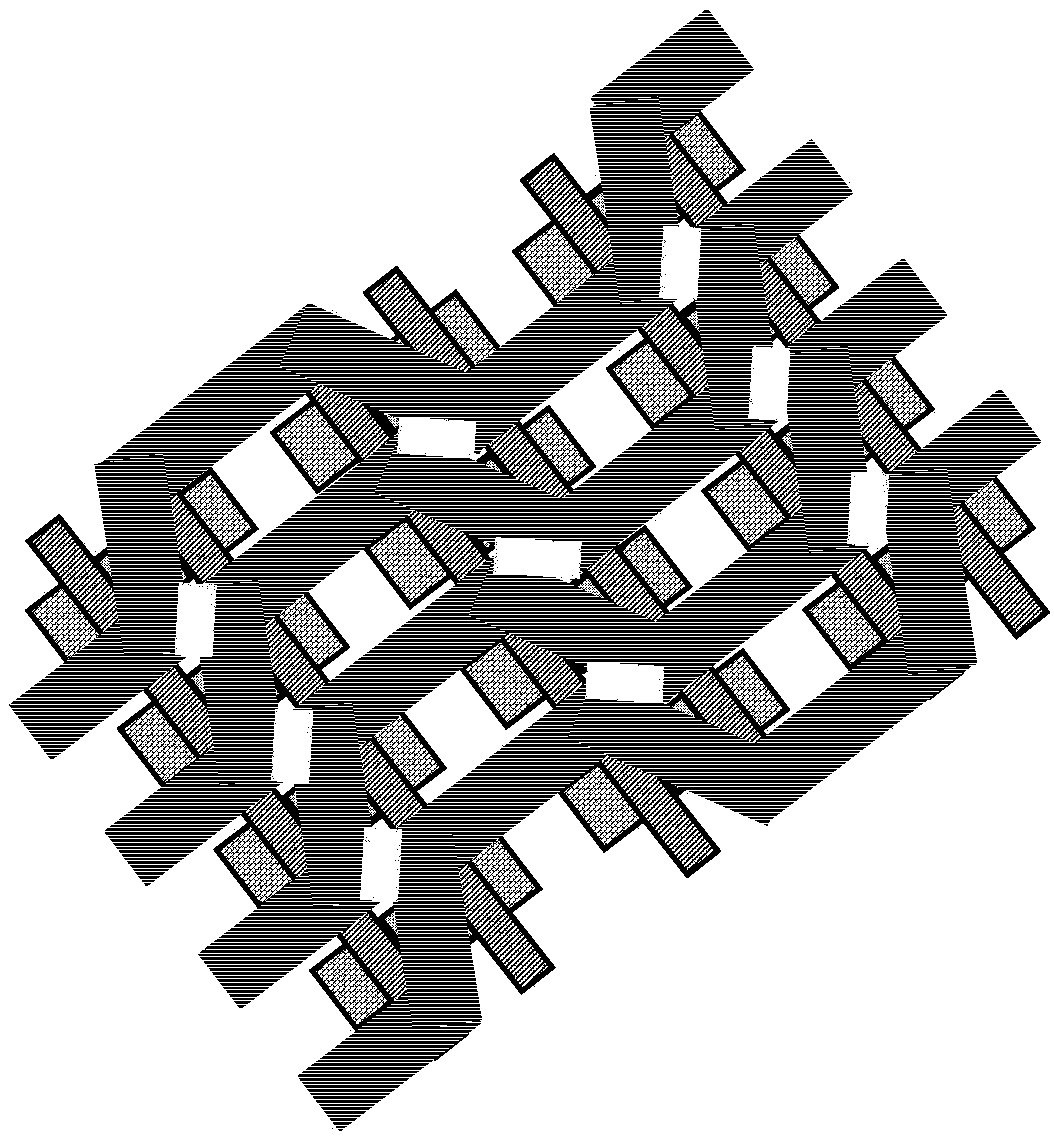

[0099] This embodiment provides a semiconductor structure preparation method, such as figure 2 As shown, the semiconductor structure preparation method at least includes the following steps:

[0100] S01, providing a semiconductor substrate, forming a shallow trench isolation structure on the semiconductor substrate to isolate a plurality of active regions arranged at intervals, and forming a plurality of buried gate components on the active region ;

[0101] S02, forming a first isolation layer on the substrate;

[0102] S03, forming a patterned first mask layer on the first isolation layer, where a plurality of first grooves are formed on the first mask layer;

[0103] S04, forming a patterned second mask layer on the first mask layer, forming a plurality of second grooves on the second mask layer, the direction of the second grooves is the same as that of the first mask layer The directions of the grooves intersect;

[0104] S05. Using the first mask layer and the seco...

Embodiment 2

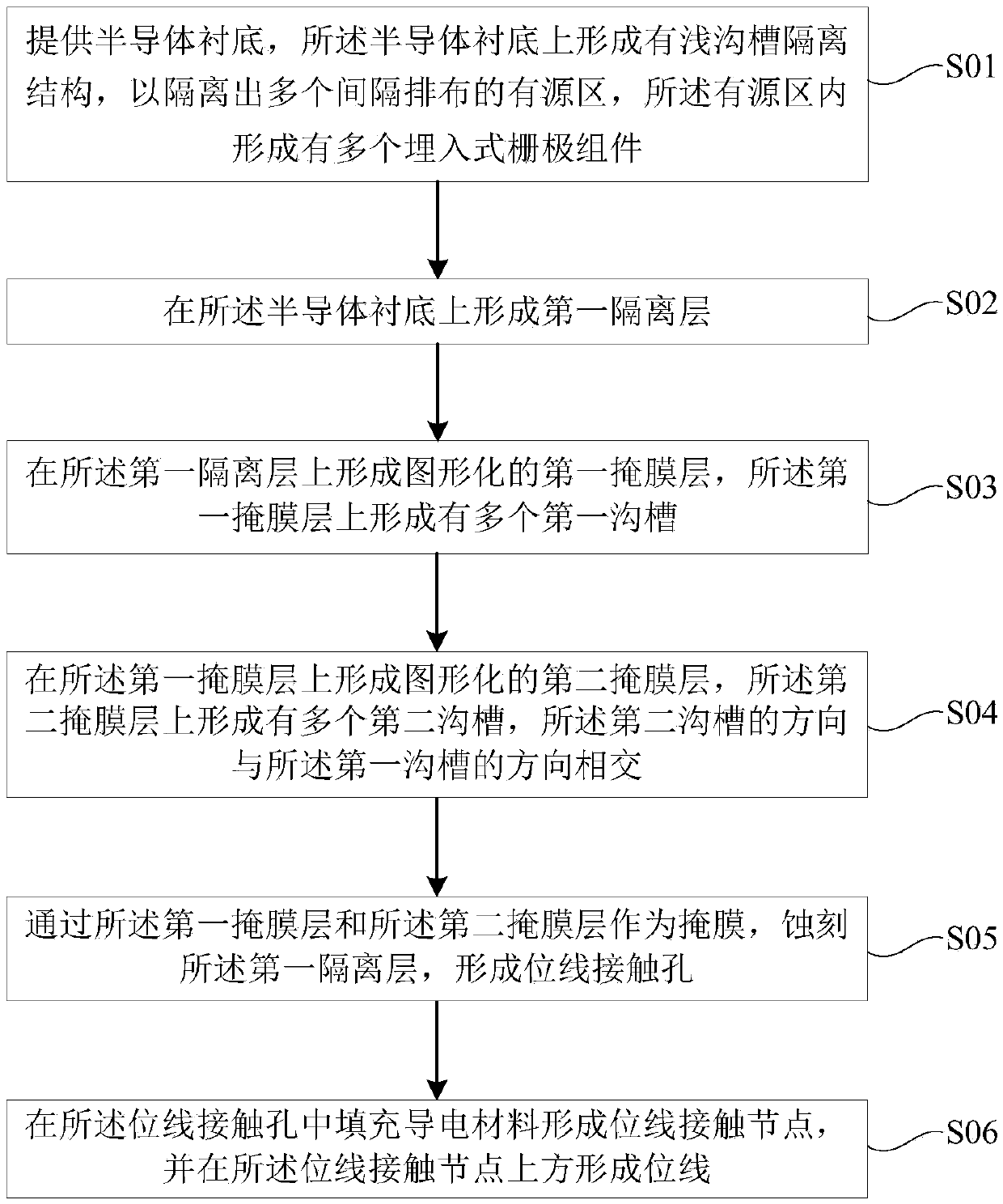

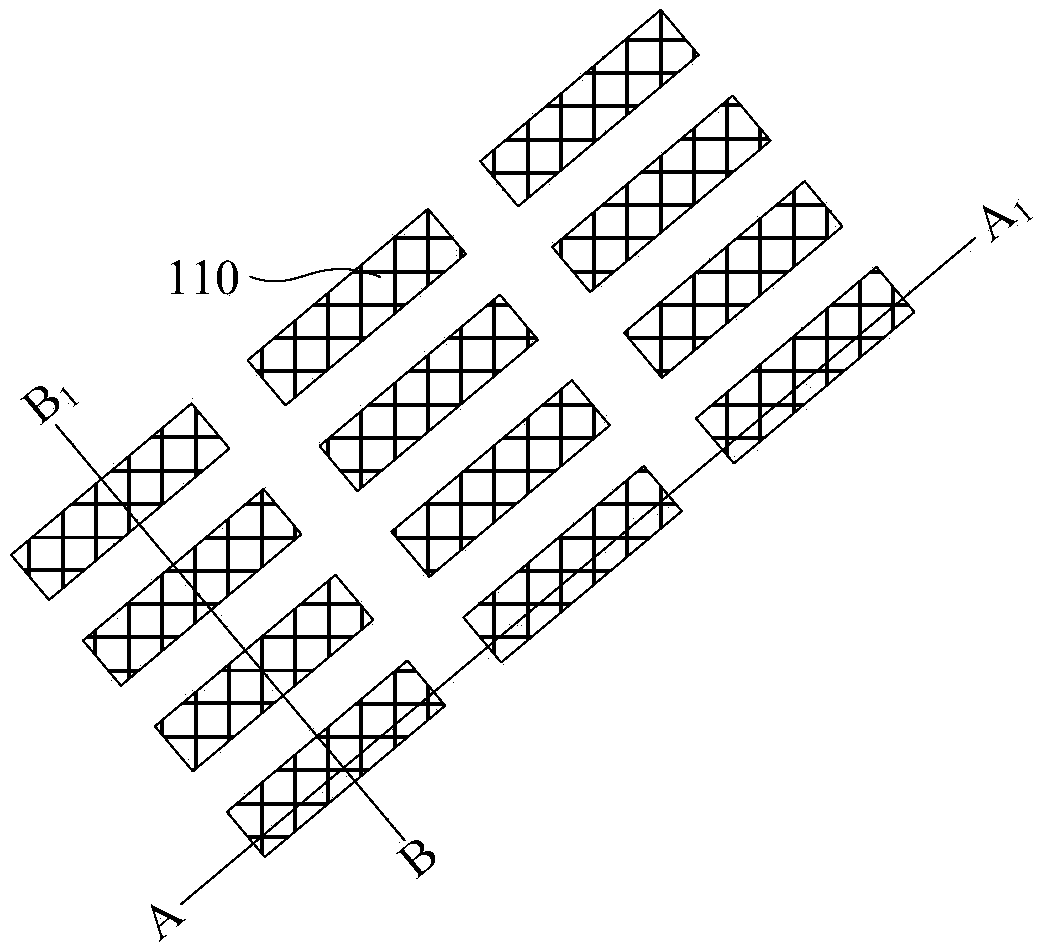

[0122] Continue to refer to the attached Figures 3 to 14-2B , the present invention also provides a semiconductor structure, in this embodiment, the semiconductor structure at least includes:

[0123] A semiconductor substrate 100, the semiconductor substrate 100 has a shallow trench isolation structure 125 to isolate a plurality of active regions 110 arranged at intervals, and the active region 110 has a plurality of buried gate components 215 ;

[0124] The first isolation layer 220, such as Figure 4-2 As shown in A, the first isolation layer 220 is located above the semiconductor substrate 100 .

[0125] The bit line contact node 375, the bit line contact node 375 is located at least part of the active region and part of the shallow trench isolation structure 125 between the adjacent buried gate components 215 in the same active region 110 , the bit line contact node 375 is isolated by the first isolation layer 220; as Figure 11B As shown, in a preferred embodiment o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com